- 您现在的位置:买卖IC网 > PDF目录298505 > 72821L15TF8 (INTEGRATED DEVICE TECHNOLOGY INC) 1K X 9 BI-DIRECTIONAL FIFO, 10 ns, PQFP64 PDF资料下载

参数资料

| 型号: | 72821L15TF8 |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | FIFO |

| 英文描述: | 1K X 9 BI-DIRECTIONAL FIFO, 10 ns, PQFP64 |

| 封装: | SLIM, TQFP-64 |

| 文件页数: | 15/16页 |

| 文件大小: | 211K |

| 代理商: | 72821L15TF8 |

8

IDT72801/728211/72821/72831/72841/72851 DUAL CMOS SyncFIFOTM

DUAL 256 x 9, DUAL 512 x 9, DUAL 1K x 9, DUAL 2K x 9, DUAL 4K x 9, DUAL 8K x 9

COMMERCIAL AND INDUSTRIAL

TEMPERATURERANGES

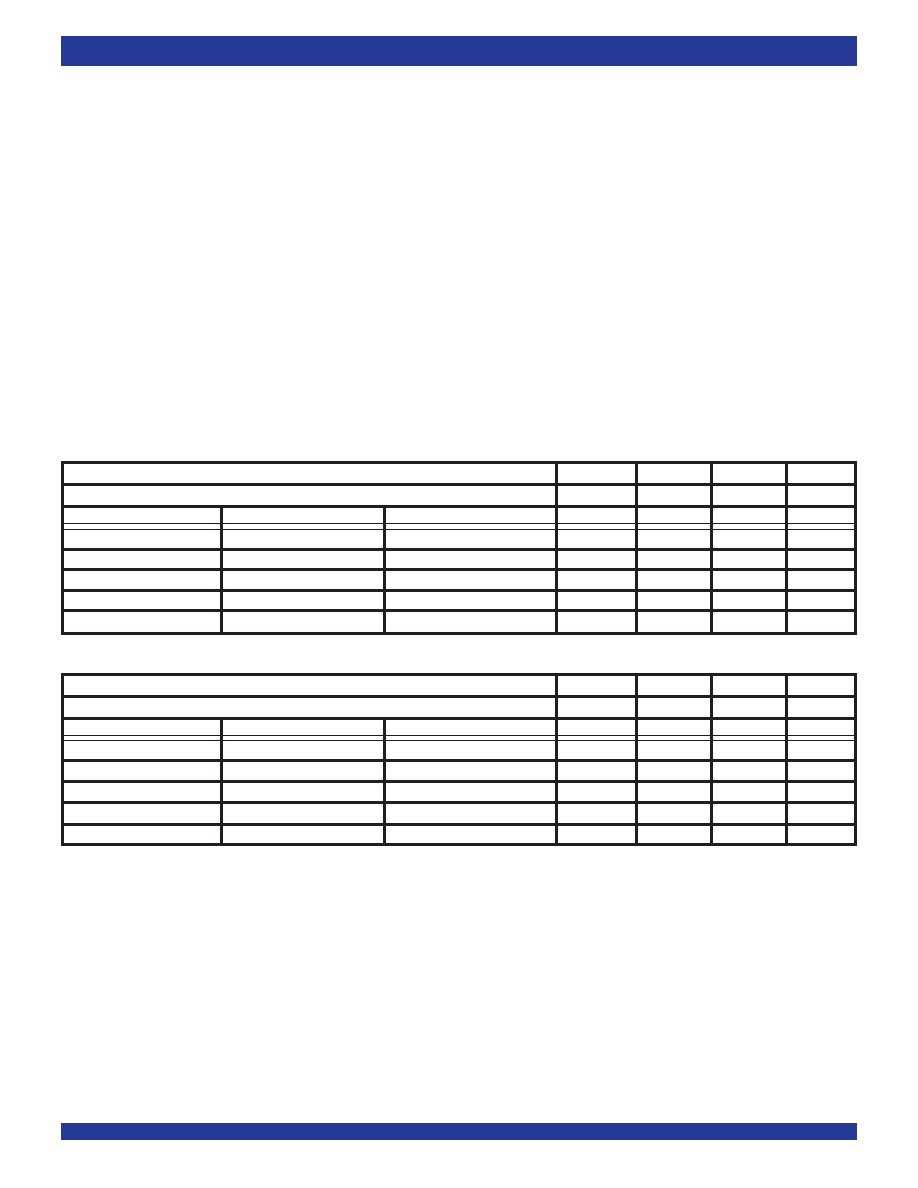

NUMBER OF WORDS IN ARRAY A

FFA

PAFA

PAEA

EFA

NUMBER OF WORDS IN ARRAY B

FFB

PAFB

PAEB

EFB

72801

72811

72821

00

0

H

L

1 to n(1)

HH

L

H

(n+1) to (256-(m+1))

(n+1) to (512-(m+1))

(n+1) to (1,024-(m+1))

H

(256-m)(2) to 255

(512-m)(2) to 511

(1,024-m)(2) to 1,023

H

L

H

256

512

1,024

L

H

NUMBER OF WORDS IN ARRAY A

FFA

PAFA

PAEA

EFA

NUMBER OF WORDS IN ARRAY B

FFB

PAFB

PAEB

EFB

72831

72841

72851

00

0

H

L

1 to n(1)

HH

L

H

(n+1) to (2,048-(m+1))

(n+1) to (4,096-(m+1))

(n+1) to (8,192-(m+1))

H

(2,048-m)(2) to 2,047

(4,096-m)(2) to 4,095

(8,192-m)(2) to 8,191

H

L

H

2,048

4,096

8,192

L

H

Programmable Almost–Full Flag (

PAFA, PAFB)—PAFA(PAFB)willgo

LOW when the amount of data in Array A (B) reaches the almost-full condition.

If no reads are performed after Reset,

PAFA(PAFB)willgoLOWafter(256-m)

writes to the IDT72801's FIFO A (B); (512-m) writes to the IDT72811's FIFO

A (B); (1,024-m) writes to the IDT72821's FIFO A (B); (2,048-m) writes to the

IDT72831's FIFO A (B); (4,096-m) writes to the IDT72841's FIFO A (B); or

(8,192-m) writes to the IDT72851's FIFO A (B).

FFA(FFB)issynchronizedwithrespecttotheLOW-to-HIGHtransitionofthe

Write Clock WCLKA (WCLKB). The offset “m” is defined in the Full Offset

registers.

If there is no Full offset specified,

PAFA(PAFB)willgoLOWatFull-7words.

PAFA(PAFB)issynchronizedwithrespecttotheLOW-to-HIGHtransition

of WCLKA (WCLKB).

ProgrammableAlmost–EmptyFlag(

PAEA, PAEB)—PAEA(PAEB)will

goLOWwhenthereadpointeris"n+1"locationslessthanthewritepointer. The

offset"n"isdefinedintheEmptyOffset registers. Ifnoreadsareperformedafter

Reset,

PAEA(PAEB)willgoHIGHafter"n+1"writestoFIFOA(B).

If there is no Empty offset specified,

PAEA(PAEB)willgoLOWatEmpty+7

words.

PAEA(PAEB)issynchronizedwithrespecttotheLOW-to-HIGHtransition

of the Read Clock RCLKA (RCLKB).

Data Outputs (QA0 – QA8, QB0 – QB8 ) — QA0 - QA8 are the nine data

outputs for memory array A, QB0 - QB8 are the nine data outputs for memory

array B.

TABLE 1: STATUS FLAGS FOR A AND B FIFOS

NOTES:

1. n = Empty Offset (n = 7 default value)

2. m = Full Offset (m = 7 default value)

相关PDF资料 |

PDF描述 |

|---|---|

| 72R99-P | 25 A, BARRIER STRIP TERMINAL BLOCK, 1 ROW, 1 DECK |

| 72R99-M | 25 A, BARRIER STRIP TERMINAL BLOCK, 1 ROW, 1 DECK |

| 72R99-59 | 25 A, BARRIER STRIP TERMINAL BLOCK, 1 ROW, 1 DECK |

| 72R99-49 | 25 A, BARRIER STRIP TERMINAL BLOCK, 1 ROW, 1 DECK |

| 72R99-47 | 25 A, BARRIER STRIP TERMINAL BLOCK, 1 ROW, 1 DECK |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 72821L15TFI8 | 制造商:Integrated Device Technology Inc 功能描述:FIFO SYNC QUAD DEPTH/WIDTH BI-DIR 1KX9X2 64TQFP - Tape and Reel |

| 72821L25PF | 功能描述:先进先出 RoHS:否 制造商:IDT 电路数量: 数据总线宽度:18 bit 总线定向:Unidirectional 存储容量:4 Mbit 定时类型:Synchronous 组织:256 K x 18 最大时钟频率:100 MHz 访问时间:10 ns 电源电压-最大:3.6 V 电源电压-最小:6 V 最大工作电流:35 mA 最大工作温度:+ 85 C 封装 / 箱体:TQFP-80 封装: |

| 72821L25PF8 | 功能描述:先进先出 RoHS:否 制造商:IDT 电路数量: 数据总线宽度:18 bit 总线定向:Unidirectional 存储容量:4 Mbit 定时类型:Synchronous 组织:256 K x 18 最大时钟频率:100 MHz 访问时间:10 ns 电源电压-最大:3.6 V 电源电压-最小:6 V 最大工作电流:35 mA 最大工作温度:+ 85 C 封装 / 箱体:TQFP-80 封装: |

| 72821L25PFI | 功能描述:先进先出 RoHS:否 制造商:IDT 电路数量: 数据总线宽度:18 bit 总线定向:Unidirectional 存储容量:4 Mbit 定时类型:Synchronous 组织:256 K x 18 最大时钟频率:100 MHz 访问时间:10 ns 电源电压-最大:3.6 V 电源电压-最小:6 V 最大工作电流:35 mA 最大工作温度:+ 85 C 封装 / 箱体:TQFP-80 封装: |

| 72821L25PFI8 | 制造商:Integrated Device Technology Inc 功能描述:FIFO Mem Sync Quad Depth/Width Bi-Dir 1K x 9 x 2 64-Pin TQFP T/R 制造商:Integrated Device Technology Inc 功能描述:FIFO SYNC QUAD DEPTH/WIDTH BI-DIR 1KX9X2 64TQFP - Tape and Reel |

发布紧急采购,3分钟左右您将得到回复。