- 您现在的位置:买卖IC网 > PDF目录298505 > 72821L15TF8 (INTEGRATED DEVICE TECHNOLOGY INC) 1K X 9 BI-DIRECTIONAL FIFO, 10 ns, PQFP64 PDF资料下载

参数资料

| 型号: | 72821L15TF8 |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | FIFO |

| 英文描述: | 1K X 9 BI-DIRECTIONAL FIFO, 10 ns, PQFP64 |

| 封装: | SLIM, TQFP-64 |

| 文件页数: | 16/16页 |

| 文件大小: | 211K |

| 代理商: | 72821L15TF8 |

9

IDT72801/728211/72821/72831/72841/72851 DUAL CMOS SyncFIFOTM

DUAL 256 x 9, DUAL 512 x 9, DUAL 1K x 9, DUAL 2K x 9, DUAL 4K x 9, DUAL 8K x 9

COMMERCIAL AND INDUSTRIAL

TEMPERATURERANGES

NOTES:

1. Holding WENA2/

LDA (WENB2/LDB) HIGH during reset will make the pin act as a second write enable pin. Holding WENA2/LDA (WENB2/LDB) LOW

during reset will make the pin act as a load enable for the programmable flag offset registers.

2.

After reset, QA0 - QA8 (QB0 - QB8) will be LOW if

OEA (OEB) = 0 and tri-state if OEA (OEB) = 1.

3.

The clocks RCLKA, WCLKA (RCLKB, WCLKB) can be free-running during reset.

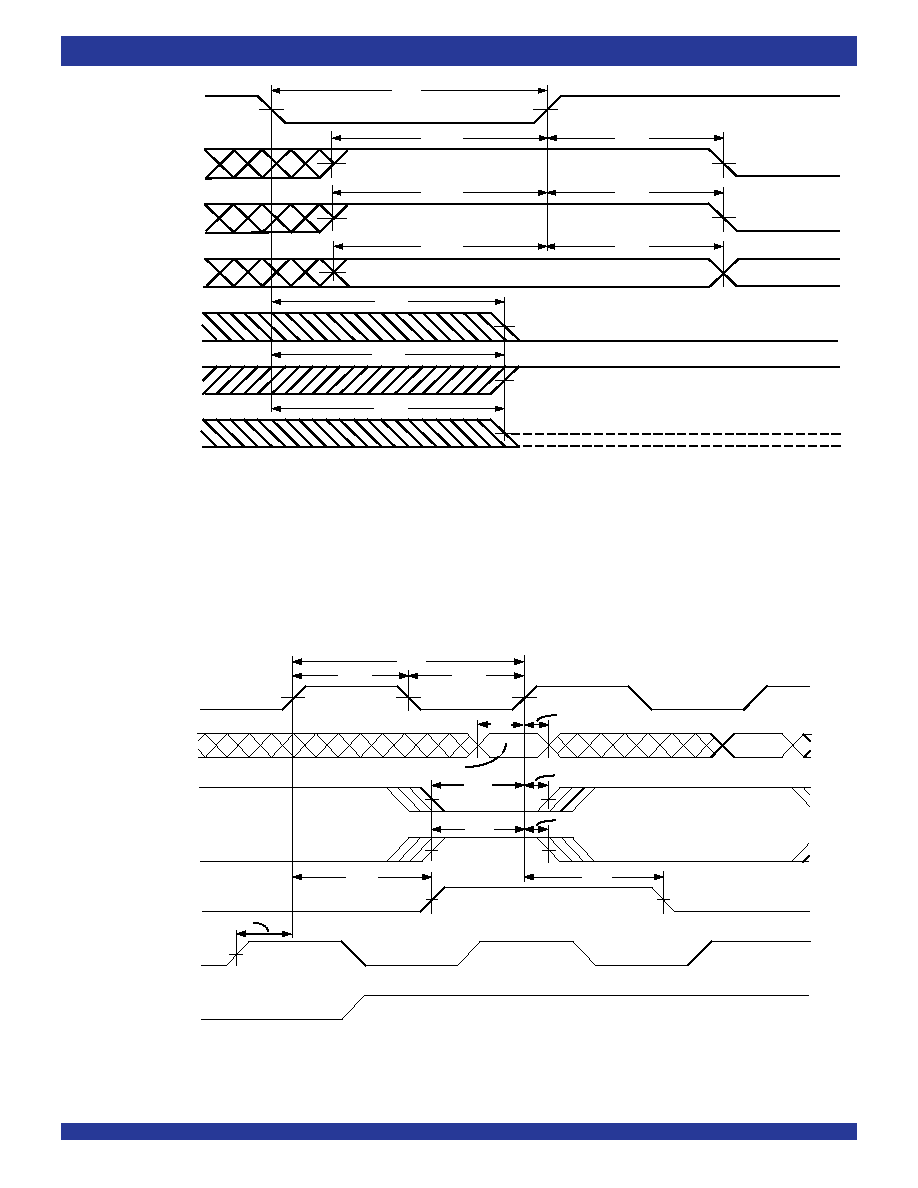

Figure 4. Reset Timing

tRS

tRSR

RSA (RSB)

RENA1, RENA2

(

RENB1, RENB2)

tRSF

OEA (OEB) = 1

OEA (OEB) = 0

(2)

EFA, PAEA

(

EFB, PAEB)

FFA, PAFA

(

FFB, PAFB)

QA0 - QA8

(QB0 - QB8)

3034 drw 05

WENA1

(

WENB1)

tRSS

tRSF

tRSR

tRSS

tRSR

tRSS

WENA2/

LDA

(WENB2/

LDB)

(1)

NOTE:

1.

tSKEW1 is the minimum time between a rising RCLKA (RCLKB) edge and a rising WCLKA (WCLKB) edge for

FFA (FFB) to change during the current clock cycle. If the time between

the rising edge of RCLKA (RCLKB) and the rising edge of WCLKA (WCLKB) is less than tSKEW1, then

FFA (FFB) may not change state until the next WCLKA (WCLKB) edge.

Figure 5. Write Cycle Timing

tDH

tENH

tSKEW1(1)

tCLK

tCLKH

tCLKL

tDS

tENS

tWFF

WCLKA (WCLKB)

DA0 - DA8

(DB0 - DB8)

WENA1

(

WENB1)

WENA2 (WENB2)

(If Applicable)

FFA

(

FFB)

RCLKA (RCLKB)

RENA1, RENA2

(

RENB1, RENB2)

NO OPERATION

3034 drw 06

DATA IN VALID

tENS

tENH

相关PDF资料 |

PDF描述 |

|---|---|

| 72R99-P | 25 A, BARRIER STRIP TERMINAL BLOCK, 1 ROW, 1 DECK |

| 72R99-M | 25 A, BARRIER STRIP TERMINAL BLOCK, 1 ROW, 1 DECK |

| 72R99-59 | 25 A, BARRIER STRIP TERMINAL BLOCK, 1 ROW, 1 DECK |

| 72R99-49 | 25 A, BARRIER STRIP TERMINAL BLOCK, 1 ROW, 1 DECK |

| 72R99-47 | 25 A, BARRIER STRIP TERMINAL BLOCK, 1 ROW, 1 DECK |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 72821L15TFI8 | 制造商:Integrated Device Technology Inc 功能描述:FIFO SYNC QUAD DEPTH/WIDTH BI-DIR 1KX9X2 64TQFP - Tape and Reel |

| 72821L25PF | 功能描述:先进先出 RoHS:否 制造商:IDT 电路数量: 数据总线宽度:18 bit 总线定向:Unidirectional 存储容量:4 Mbit 定时类型:Synchronous 组织:256 K x 18 最大时钟频率:100 MHz 访问时间:10 ns 电源电压-最大:3.6 V 电源电压-最小:6 V 最大工作电流:35 mA 最大工作温度:+ 85 C 封装 / 箱体:TQFP-80 封装: |

| 72821L25PF8 | 功能描述:先进先出 RoHS:否 制造商:IDT 电路数量: 数据总线宽度:18 bit 总线定向:Unidirectional 存储容量:4 Mbit 定时类型:Synchronous 组织:256 K x 18 最大时钟频率:100 MHz 访问时间:10 ns 电源电压-最大:3.6 V 电源电压-最小:6 V 最大工作电流:35 mA 最大工作温度:+ 85 C 封装 / 箱体:TQFP-80 封装: |

| 72821L25PFI | 功能描述:先进先出 RoHS:否 制造商:IDT 电路数量: 数据总线宽度:18 bit 总线定向:Unidirectional 存储容量:4 Mbit 定时类型:Synchronous 组织:256 K x 18 最大时钟频率:100 MHz 访问时间:10 ns 电源电压-最大:3.6 V 电源电压-最小:6 V 最大工作电流:35 mA 最大工作温度:+ 85 C 封装 / 箱体:TQFP-80 封装: |

| 72821L25PFI8 | 制造商:Integrated Device Technology Inc 功能描述:FIFO Mem Sync Quad Depth/Width Bi-Dir 1K x 9 x 2 64-Pin TQFP T/R 制造商:Integrated Device Technology Inc 功能描述:FIFO SYNC QUAD DEPTH/WIDTH BI-DIR 1KX9X2 64TQFP - Tape and Reel |

发布紧急采购,3分钟左右您将得到回复。