- 您现在的位置:买卖IC网 > PDF目录158197 > 72825LB15PFI9 (INTEGRATED DEVICE TECHNOLOGY INC) 1K X 18 BI-DIRECTIONAL FIFO, 10 ns, PQFP128 PDF资料下载

参数资料

| 型号: | 72825LB15PFI9 |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | FIFO |

| 英文描述: | 1K X 18 BI-DIRECTIONAL FIFO, 10 ns, PQFP128 |

| 封装: | TQFP-128 |

| 文件页数: | 12/26页 |

| 文件大小: | 336K |

| 代理商: | 72825LB15PFI9 |

COMMERCIALANDINDUSTRIAL

TEMPERATURERANGES

IDT72805LB/72815LB/72825LB/72835LB/72845LB CMOS Dual SyncFIFOTM

256 x 18, 512 x 18, 1,024 x 18, 2,048 x 18 and 4,096 x 18

2

PIN CONFIGURATIONS

WCLKA

DA3

DA1

DA0

DB13

DB16

RCLKB

LDB

RSB

QB17

QB16

PAFA

DA4

WENA

DA2

DB12

DB15

RENB

OEB

EFB

QB15

QB14

FFA

RXIA

WXIA

DA5

DB14

DB11

GND

DB17

GND

QB13

QB11

QB8

QB10

QB12

VCC

DB7

DB10

DB8

FLA

QA2

QA0

RXOA

QA1

QA4

QA3

WXOA/

HFA

PAEA

DB9

DB6

VCC

QB9

QB7

QA5

QA6

GND

VCC

GND

VCC

GND

QB6

QB5

QA7

QA9

VCC

DA6

DA9

PAEB

WXOB/

HFB

QB3

QB4

QB1

QA8

QA10

QA12

VCC

DA7

DA10

DA8

FLB

QB2

QB0

RXOB

QA11

QA13

GND

DA17

GND

DA11

DA14

DB5

WXIB

RXIB

FFB

QA14

QA15

EFA

OEA

RENA

DA15

DA12

DB2

WENB

DB4

PAFB

QA16

QA17

RSA

LDA

RCKLA

DA16

DA13

DB0

DB1

DB3

WCLKB

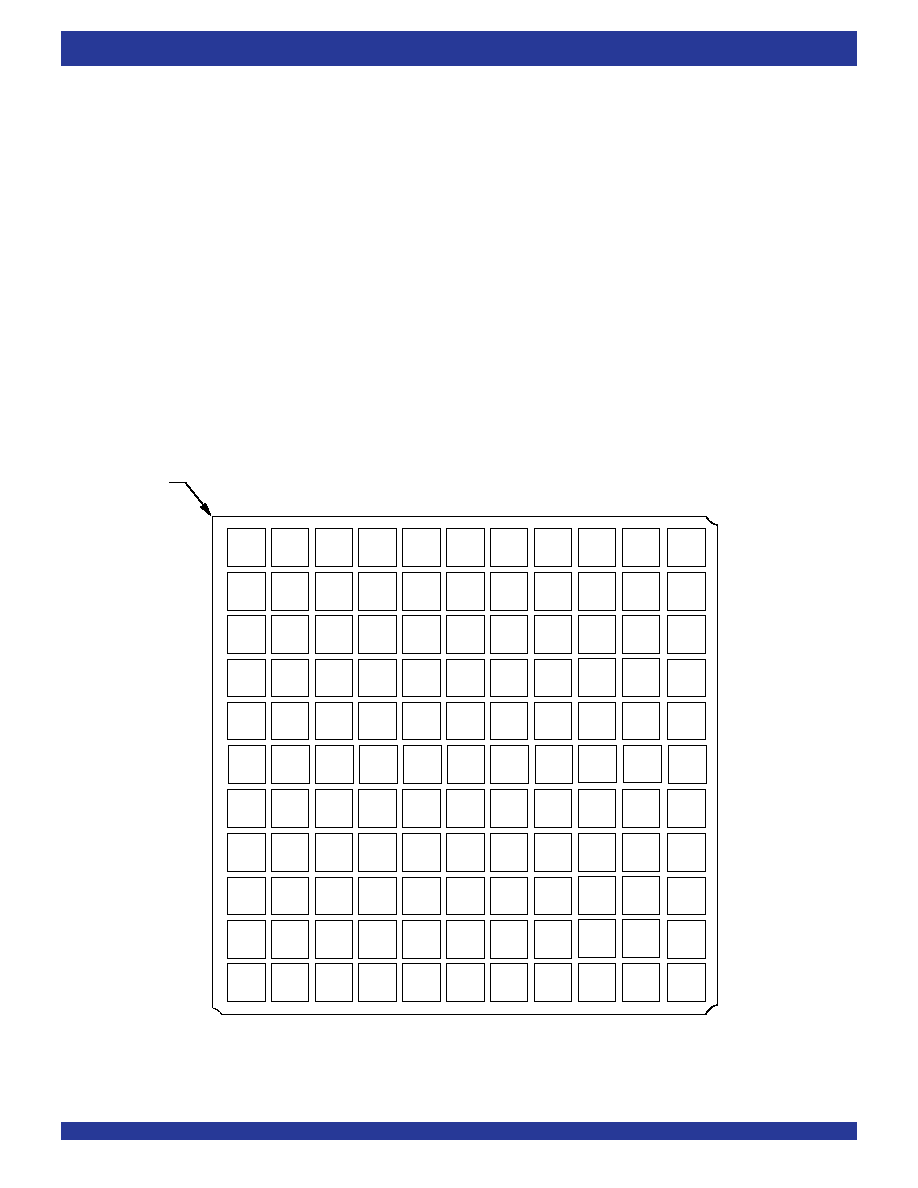

123

456

789

10

11

A

B

C

D

E

F

G

H

J

K

L

PIN 1

3139 drw 02

PBGA (BG121-1, order code: BG)

TOP VIEW

NOTE:

1.

The PBGA is only available for the IDT72805LB/72815LB/72825LB in the 15 or 25 ns speed grade.

IDT72205LB/72215LB/72225LB/72235LB/72245LB FIFOs in a single package

with all associated control, data, and flag lines assigned to independent

pins. These devices are very high-speed, low-power First-In, First-Out

(FIFO) memories with clocked read and write controls. These FIFOs are

applicable for a wide variety of data buffering needs, such as optical disk

controllers, Local Area Networks (LANs), and interprocessor communication.

Each of the two FIFOs contained in these devices has an 18-bit input and

output port. Each input port is controlled by a free-running clock (WCLK), and

an input enable pin (

WEN). Data is read into the synchronous FIFO on every

clock when

WEN is asserted. The output port of each FIFO bank is controlled

by another clock pin (RCLK) and another enable pin (

REN). The Read Clock

can be tied to the Write Clock for single clock operation or the two clocks can

run asynchronous of one another for dual-clock operation. An Output Enable

pin (

OE) is provided on the read port of each FIFO for three-state control of the

output.

The synchronous FIFOs have two fixed flags, Empty Flag/Output Ready

(

EF/OR) and Full Flag/Input Ready (FF/IR), and two programmable flags,

Almost-Empty(

PAE)andAlmost-Full(PAF).Theoffsetloadingoftheprogram-

mable flags is controlled by a simple state machine, and is initiated by asserting

the Load pin (

LD). A Half-Full flag (HF) is available for each FIFO that is

implemented as a single device configuration.

There are two possible timing modes of operation with these devices: IDT

Standard mode and First Word Fall Through (FWFT) mode.

In IDT Standard Mode, the first word written to an empty FIFO will not

appear on the data output lines unless a specific read operation is performed.

A read operation, which consists of activating

REN and enabling a rising RCLK

edge, will shift the word from internal memory to the data output lines.

In FWFT mode, the first word written to an empty FIFO is clocked directly

to the data output lines after three transitions of the RCLK signal. A

REN does

not have to be asserted for accessing the first word.

These devices are depth expandable using a daisy-chain technique or First

Word Fall Through (FWFT) mode. The

XI and XO pins are used to expand the

FIFOs. In depth expansion configuration,

FLisgroundedonthefirstdeviceand

set to HIGH for all other devices in the Daisy Chain.

The IDT72805LB/72815LB/72825LB/72835LB/72845LB are fabricated

using IDT’s high-speed submicron CMOS technology.

DESCRIPTION (Continued)

相关PDF资料 |

PDF描述 |

|---|---|

| 7283-1019 | 1 CONTACT(S), FEMALE, COMBINATION LINE CONNECTOR |

| 7283-1114 | 1 CONTACT(S), FEMALE, COMBINATION LINE CONNECTOR |

| 7283-4421 | 2 CONTACT(S), FEMALE, COMBINATION LINE CONNECTOR |

| 7283-1064 | 6 CONTACT(S), FEMALE, COMBINATION LINE CONNECTOR |

| 7283-1118 | 11 CONTACT(S), FEMALE, COMBINATION LINE CONNECTOR |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 72825LB25BG | 功能描述:先进先出 RoHS:否 制造商:IDT 电路数量: 数据总线宽度:18 bit 总线定向:Unidirectional 存储容量:4 Mbit 定时类型:Synchronous 组织:256 K x 18 最大时钟频率:100 MHz 访问时间:10 ns 电源电压-最大:3.6 V 电源电压-最小:6 V 最大工作电流:35 mA 最大工作温度:+ 85 C 封装 / 箱体:TQFP-80 封装: |

| 72825LB25BG8 | 制造商:Integrated Device Technology Inc 功能描述:FIFO Mem Sync Quad Depth/Width Bi-Dir 1K x 18 x 2 121-Pin BGA T/R 制造商:Integrated Device Technology Inc 功能描述:FIFO SYNC QUAD DEPTH/WIDTH BI-DIR 1KX18X2 121BGA - Tape and Reel |

| 72825LB25PF | 功能描述:先进先出 RoHS:否 制造商:IDT 电路数量: 数据总线宽度:18 bit 总线定向:Unidirectional 存储容量:4 Mbit 定时类型:Synchronous 组织:256 K x 18 最大时钟频率:100 MHz 访问时间:10 ns 电源电压-最大:3.6 V 电源电压-最小:6 V 最大工作电流:35 mA 最大工作温度:+ 85 C 封装 / 箱体:TQFP-80 封装: |

| 72825LB25PF8 | 功能描述:先进先出 RoHS:否 制造商:IDT 电路数量: 数据总线宽度:18 bit 总线定向:Unidirectional 存储容量:4 Mbit 定时类型:Synchronous 组织:256 K x 18 最大时钟频率:100 MHz 访问时间:10 ns 电源电压-最大:3.6 V 电源电压-最小:6 V 最大工作电流:35 mA 最大工作温度:+ 85 C 封装 / 箱体:TQFP-80 封装: |

| 7282-5PG-300 | 功能描述:标准环形连接器 5P PIN PANEL MNT RoHS:否 制造商:Hirose Connector 系列:EM-W 产品类型:Accessories 位置/触点数量:1 触点类型: 触点电镀: 安装风格:Cable 外壳材质: 端接类型:Clamp 电压额定值: |

发布紧急采购,3分钟左右您将得到回复。