- 您现在的位置:买卖IC网 > PDF目录158197 > 72825LB15PFI9 (INTEGRATED DEVICE TECHNOLOGY INC) 1K X 18 BI-DIRECTIONAL FIFO, 10 ns, PQFP128 PDF资料下载

参数资料

| 型号: | 72825LB15PFI9 |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | FIFO |

| 英文描述: | 1K X 18 BI-DIRECTIONAL FIFO, 10 ns, PQFP128 |

| 封装: | TQFP-128 |

| 文件页数: | 13/26页 |

| 文件大小: | 336K |

| 代理商: | 72825LB15PFI9 |

COMMERCIALANDINDUSTRIAL

TEMPERATURERANGES

IDT72805LB/72815LB/72825LB/72835LB/72845LB CMOS Dual SyncFIFOTM

256 x 18, 512 x 18, 1,024 x 18, 2,048 x 18 and 4,096 x 18

20

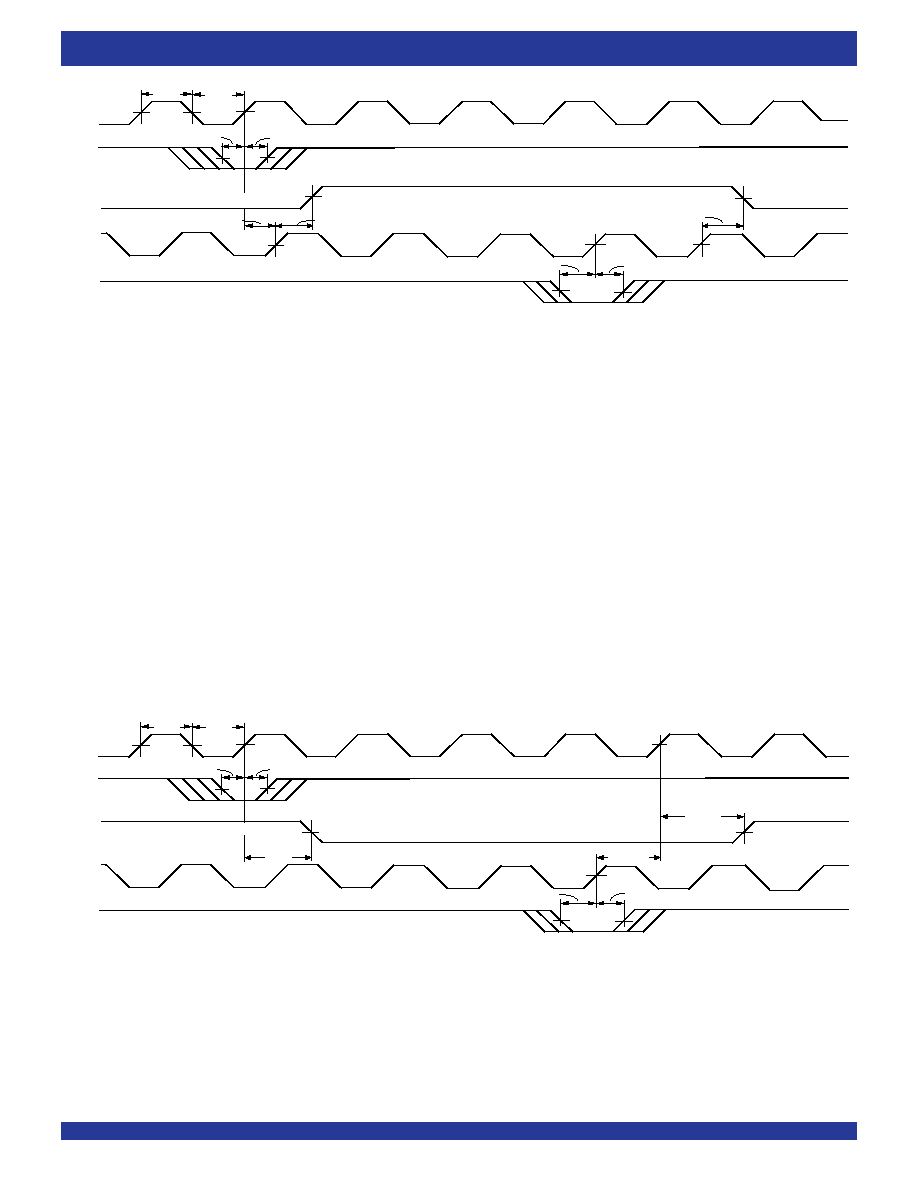

Figure 22. Synchronous Programmable Almost-Empty Flag Timing (IDT Standard and FWFT Modes)

Figure 23. Synchronous Programmable Almost-Full Flag Timing (IDT Standard and FWFT Modes)

NOTES:

1. n =

PAE offset.

2. For IDT Standard Mode.

3. For FWFT Mode.

4. tSKEW2 is the minimum time between a rising WCLK edge and a rising RCLK edge for

PAE to go HIGH during the current clock cycle. If the time between the rising edge of WCLK and the

rising edge of RCLK is less than tSKEW2, then the

PAE deassertion may be delayed one extra RCLK cycle.

5.

PAE is asserted and updated on the rising edge of RCLK only.

6. Select this mode by setting (

FL, RXI, WXI) = (1,0,0), (1,0,1), or (1,1,0) during Reset.

NOTES:

1. m =

PAF offset.

2. D = maximum FIFO Depth.

In IDT Standard Mode: D = 256 for the IDT72805, 512 for the IDT72815, 1,024 for the IDT72825, 2,048 for the IDT72835 and 4,096 for the IDT72845.

In FWFT Mode: D = 257 for the IDT72805, 513 for the IDT72815, 1,025 for the IDT72825, 2,049 for the IDT72835 and 4,097 for the IDT72845.

3. tSKEW2 is the minimum time between a rising RCLK edge and a rising WCLK edge for

PAF to go HIGH during the current clock cycle. If the time between the rising edge of RCLK and

the rising edge of WCLK is less than tSKEW2, then the

PAF deassertion time may be delayed an extra WCLK cycle.

4.

PAF is asserted and updated on the rising edge of WCLK only.

5. Select this mode by setting (

FL, RXI, WXI) = (1,0,0), (1,0,1), or (1,1,0) during Reset.

WCLK

tENH

tCLKH

tCLKL

WEN

PAE

RCLK

REN

3139 drw 22

tENS

tENH

tENS

n words in FIFO(2),

n + 1words in FIFO(3)

n + 1 words in FIFO(2),

n + 2 words in FIFO(3)

tSKEW2

tPAES

n Words in FIFO(2),

n + 1 words in FIFO(3)

(4)

tPAES

WCLK

tENH

tCLKH

tCLKL

WEN

PAF

RCLK

REN

3139 drw 23

tENS

tENH

tENS

D-(m+1) Words in FIFO

D - m Words in FIFO

D -(m+1) Words

in FIFO

tPAFS

tSKEW2(3)

相关PDF资料 |

PDF描述 |

|---|---|

| 7283-1019 | 1 CONTACT(S), FEMALE, COMBINATION LINE CONNECTOR |

| 7283-1114 | 1 CONTACT(S), FEMALE, COMBINATION LINE CONNECTOR |

| 7283-4421 | 2 CONTACT(S), FEMALE, COMBINATION LINE CONNECTOR |

| 7283-1064 | 6 CONTACT(S), FEMALE, COMBINATION LINE CONNECTOR |

| 7283-1118 | 11 CONTACT(S), FEMALE, COMBINATION LINE CONNECTOR |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 72825LB25BG | 功能描述:先进先出 RoHS:否 制造商:IDT 电路数量: 数据总线宽度:18 bit 总线定向:Unidirectional 存储容量:4 Mbit 定时类型:Synchronous 组织:256 K x 18 最大时钟频率:100 MHz 访问时间:10 ns 电源电压-最大:3.6 V 电源电压-最小:6 V 最大工作电流:35 mA 最大工作温度:+ 85 C 封装 / 箱体:TQFP-80 封装: |

| 72825LB25BG8 | 制造商:Integrated Device Technology Inc 功能描述:FIFO Mem Sync Quad Depth/Width Bi-Dir 1K x 18 x 2 121-Pin BGA T/R 制造商:Integrated Device Technology Inc 功能描述:FIFO SYNC QUAD DEPTH/WIDTH BI-DIR 1KX18X2 121BGA - Tape and Reel |

| 72825LB25PF | 功能描述:先进先出 RoHS:否 制造商:IDT 电路数量: 数据总线宽度:18 bit 总线定向:Unidirectional 存储容量:4 Mbit 定时类型:Synchronous 组织:256 K x 18 最大时钟频率:100 MHz 访问时间:10 ns 电源电压-最大:3.6 V 电源电压-最小:6 V 最大工作电流:35 mA 最大工作温度:+ 85 C 封装 / 箱体:TQFP-80 封装: |

| 72825LB25PF8 | 功能描述:先进先出 RoHS:否 制造商:IDT 电路数量: 数据总线宽度:18 bit 总线定向:Unidirectional 存储容量:4 Mbit 定时类型:Synchronous 组织:256 K x 18 最大时钟频率:100 MHz 访问时间:10 ns 电源电压-最大:3.6 V 电源电压-最小:6 V 最大工作电流:35 mA 最大工作温度:+ 85 C 封装 / 箱体:TQFP-80 封装: |

| 7282-5PG-300 | 功能描述:标准环形连接器 5P PIN PANEL MNT RoHS:否 制造商:Hirose Connector 系列:EM-W 产品类型:Accessories 位置/触点数量:1 触点类型: 触点电镀: 安装风格:Cable 外壳材质: 端接类型:Clamp 电压额定值: |

发布紧急采购,3分钟左右您将得到回复。