- 您现在的位置:买卖IC网 > PDF目录10922 > 73S1209F-68IMR/F (Maxim Integrated Products)IC SMART CARD READER 68-QFN PDF资料下载

参数资料

| 型号: | 73S1209F-68IMR/F |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 119/123页 |

| 文件大小: | 0K |

| 描述: | IC SMART CARD READER 68-QFN |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 2,500 |

| 系列: | 73S12xx |

| 核心处理器: | 80515 |

| 芯体尺寸: | 8-位 |

| 速度: | 24MHz |

| 连通性: | I²C,智能卡,UART/USART |

| 外围设备: | LED,POR,WDT |

| 输入/输出数: | 9 |

| 程序存储器容量: | 32KB(32K x 8) |

| 程序存储器类型: | 闪存 |

| RAM 容量: | 2K x 8 |

| 电压 - 电源 (Vcc/Vdd): | 2.7 V ~ 5.5 V |

| 振荡器型: | 内部 |

| 工作温度: | -40°C ~ 85°C |

| 封装/外壳: | 68-VFQFN 裸露焊盘 |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页当前第119页第120页第121页第122页第123页

DS_1209F_004

73S1209F Data Sheet

Rev. 1.2

95

FD Control Register (FDReg): 0xFE13

0x11

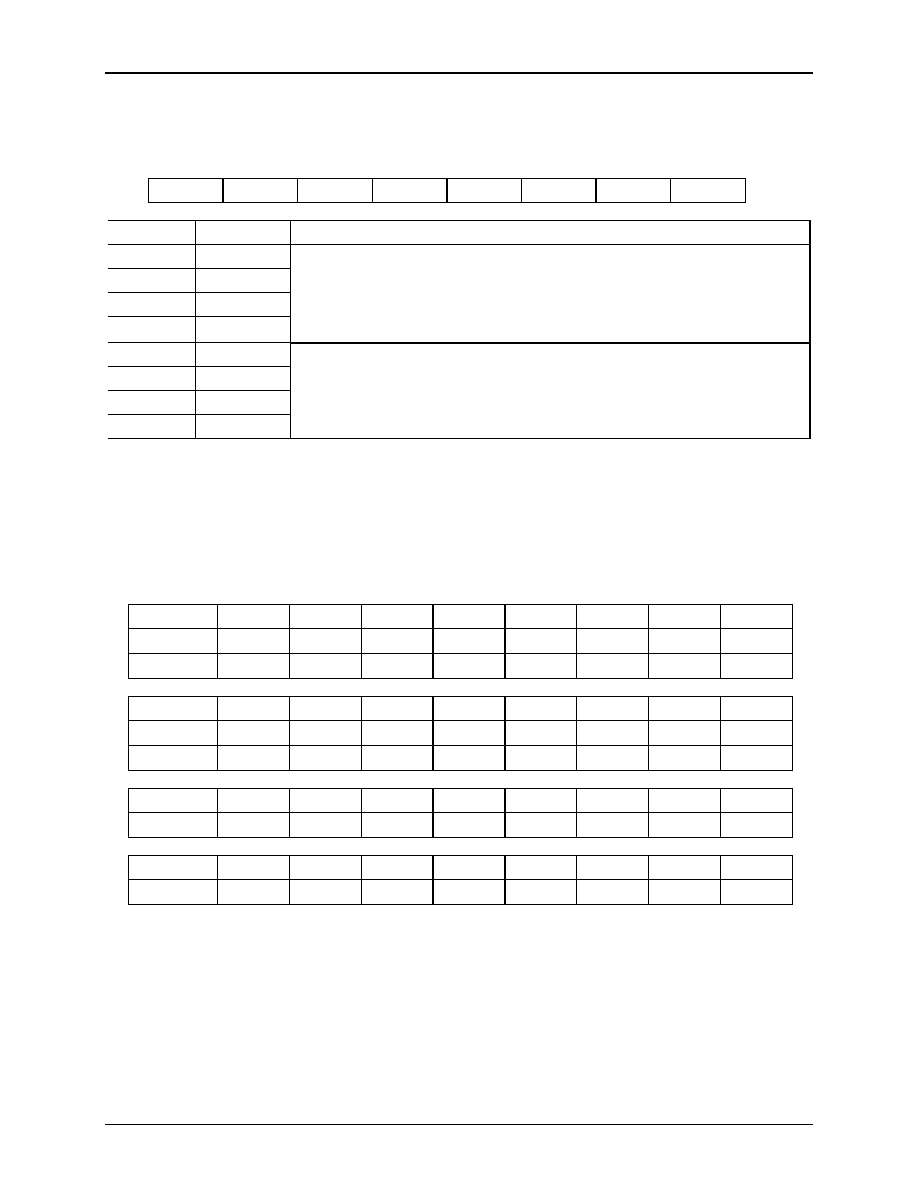

Table 91: The FDReg Register

MSB

LSB

FVAL.3

FVAL.2

FVAL.1

FVAL.0

DVAL.3

DVAL.2

DVAL.1

DVAL.0

Bit

Symbol

Function

FDReg.7

FVAL.3

Refer to Table 93 above. This value is converted per the table to set the

divide ratio used to generate the baud rate (ETU). Default, also used for

ATR, is 0001 (Fi = 372). This value is used by the selected interface.

FDReg.6

FVAL.2

FDReg.5

FVAL.1

FDReg.4

FVAL.0

FDReg.3

DVAL.3

Refer to Table 93 above. This value is used to set the divide ratio used to

generate the smart card CLK. Default, also used for ATR, is 0001 (Di = 1).

FDReg.2

DVAL.2

FDReg.1

DVAL.1

FDReg.0

DVAL.0

This register uses the transmission factors F and D to set the ETU (baud) rate. The values in this register

are mapped to the ISO 7816 conversion factors as described below. The CLK signal for each interface is

created by dividing a high-frequency, intermediate signal (MSCLK) by 2. The ETU baud rate is created

by dividing MSCLK by 2 times the Fi/Di ratio specified by the codes below. For example, if FI = 0001 and

DI = 0001, the ratio of Fi/Di is 372/1. Thus the ETU divider is configured to divide by 2 * 372 = 744. The

maximum supported F/D ratio is 4096.

Table 92: Divider Ratios Provided by the ETU Counter

FI (code)

0000

0001

0010

0011

0100

0101

0110

0111

Fi (ratio)

372

558

744

1116

1488

1860

⊕

FCLK max

4

5

6

8

12

16

20

⊕

FI(code)

1000

1001

1010

1011

1100

1101

1110

1111

Fi(ratio)

512

⊕

512

768

1024

1536

2048

⊕

2048

⊕

FCLK max

5

⊕

5

7.5

10

15

20

⊕

20

⊕

DI(code)

0000

0001

0010

0011

0100

0101

0110

0111

Di(ratio)

1

⊕

1

2

4

8

16

32

⊕

DI(code)

1000

1001

1010

1011

1100

1101

1110

1111

Di(ratio)

12

20

16

⊕

16

⊕

16

⊕

16

⊕

16

⊕

16

⊕

Note: values marked with

⊕ are not included in the ISO definition and arbitrary values have been

assigned.

The values given below are used by the ETU divider to create the ETU clock. The entries that are not

shaded will result in precise CLK/ETU per ISO requirements. Shaded areas are not precise but are

within 1% of the target value.

相关PDF资料 |

PDF描述 |

|---|---|

| VI-22N-IX-F4 | CONVERTER MOD DC/DC 18.5V 75W |

| ISD1750PYI | IC VOICE REC/PLAY 50-SEC 28-DIP |

| VI-22N-IX-F2 | CONVERTER MOD DC/DC 18.5V 75W |

| VE-25H-CV-S | CONVERTER MOD DC/DC 52V 150W |

| VI-22N-IX-F1 | CONVERTER MOD DC/DC 18.5V 75W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 73S1209F-68M/F/P1 | 功能描述:8位微控制器 -MCU Contained 80515-SoC Serial Hst Interface RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

| 73S1209F-EB | 功能描述:开发板和工具包 - 8051 73S1209F Eval Brd (Doc. Cd, Cable) RoHS:否 制造商:Silicon Labs 产品:Development Kits 工具用于评估:C8051F960, Si7005 核心: 接口类型:USB 工作电源电压: |

| 73S1209F-IM44 DK | 制造商:Maxim Integrated Products 功能描述:Development Boards & Kits - 8051 73S1209F Dev Kit Eval Bd Ice Cable Cd |

| 73S1209F-IM44 EB | 制造商:Maxim Integrated Products 功能描述:Development Boards & Kits - 8051 73S1209F Eval Brd Eval Bd Doc Cd Cable |

| 73S1209F-IM68 DK | 制造商:Maxim Integrated Products 功能描述:Development Boards & Kits - 8051 73S1209F Dev Kit Eval Bd Ice Cable Cd |

发布紧急采购,3分钟左右您将得到回复。