- 您现在的位置:买卖IC网 > PDF目录24802 > 935262730528 (NXP SEMICONDUCTORS) 4 CHANNEL(S), 500K bps, SERIAL COMM CONTROLLER, PQFP80 PDF资料下载

参数资料

| 型号: | 935262730528 |

| 厂商: | NXP SEMICONDUCTORS |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 4 CHANNEL(S), 500K bps, SERIAL COMM CONTROLLER, PQFP80 |

| 封装: | 12 X 12 MM, 1.40 MM HEIGHT, PLASTIC, MS-026, SOT-315-1, LQFP-80 |

| 文件页数: | 10/52页 |

| 文件大小: | 303K |

| 代理商: | 935262730528 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页当前第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页

Philips Semiconductors

Product specification

SC28L194

Quad UART for 3.3V and 5V supply voltage

2001 Feb 13

18

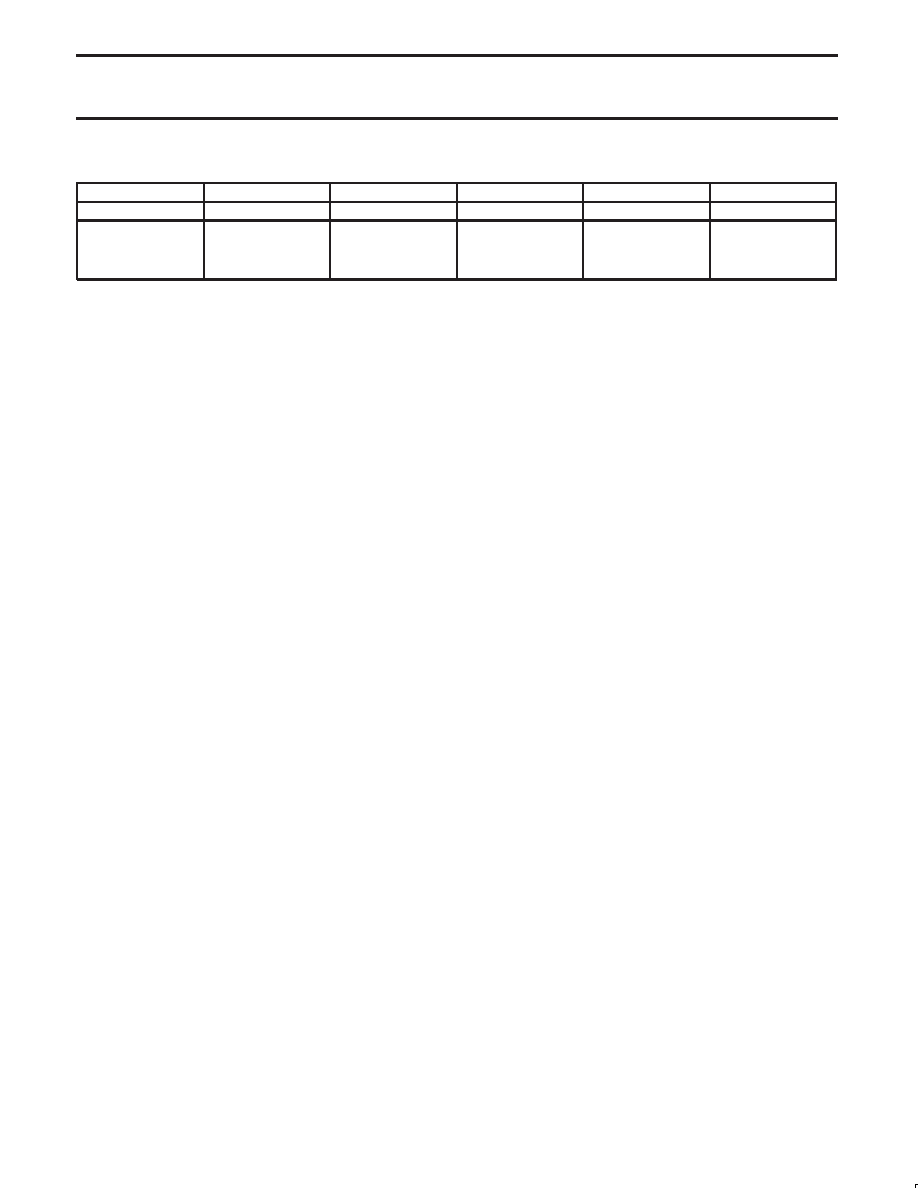

Table 4.

MR1 - Mode Register 1

Bit 7

Bit 6

Bit 5

Bit 4:3

Bit 2

Bit 1:0

RxRTS Control

ISR Read Mode

Error Mode

Parity Mode

Parity Type

Bits per Character

0 - off

1 - on

0 - ISR unmasked

1 - ISR masked

0 = Character

1 = Block

00 - With Parity

01 - Force parity

10 - No parity

11 - Special Mode

0 = Even

1 = Odd

00 - 5

01 - 6

10 - 7

11 - 8

MR1[7]: Receiver Request to Send Control

This bit controls the deactivation of the RTSN output (I/O2) by the

receiver. This output is asserted and negated by commands applied

via the command register. MR1[7] = 1 causes RTSN to be

automatically negated upon receipt of a valid start bit if the receiver

FIFO is 3/4 full or greater. RTSN is reasserted when an the FIFO fill

level falls below 3/4 full. This constitutes a change from previous

members of Philips (Signets)’ UART families where the RTSN

function triggered on FIFO full. This behavior caused problems with

PC UARTs that could not stop transmission at the proper time. The

RTSN feature can be used to prevent overrun in the receiver, by

using the RTSN output signal, to control the CTSN input of the

transmitting device.

MR1[6]: Interrupt Status Masking

This bit controls the readout mode of the Interrupt Status Register,

ISR. If set, the ISR reads the current status masked by the IMR, i.e.

only interrupt sources enabled in the IMR can ever show a ‘1’ in the

ISR. If cleared, the ISR shows the current status of the interrupt

source without regard to the Interrupt Mask setting.

MR1[5]: Error Mode Select

This bit selects the operating mode of the three FIFOed status bits

(FE, PE, received break). In the character mode, status is provided

on a character by character basis; the status applies only to the

character at. the bottom of the FIFO. In the block mode, the status

provided in the SR for these bits is the accumulation (logical OR) of

the status for all characters coming to the top of the FIFO, since the

last reset error command was issued.

MR1[4:3]: Parity Mode Select

If ‘with parity’ or ’force parity’ is selected, a parity bit is added to the

transmitted character and the receiver performs a parity check on

incoming data. MR1[4:3] = 11 selects the channel to operate in the

special Wake-up mode.

MR1[2]: Parity Type Select

This bit sets the parity type (odd or even) if the ’with parity’ mode is

programmed by MR1[4:3], and the polarity of the forced parity bit if

the ’force parity’ mode is programmed. It has no effect if the ’no

parity’ mode is programmed. In the special ’Wake-up’ mode, it

selects the polarity of the A/D bit. The parity bit is used to an

address or data byte in the ’Wake-up’ mode.

MR1[1:0]: Bits per Character Select

This field selects the number of data bits per character to be

transmitted and received. This number does not include the start,

parity, or stop bits.

相关PDF资料 |

PDF描述 |

|---|---|

| 935261296518 | 4 CHANNEL(S), 500K bps, SERIAL COMM CONTROLLER, PQCC68 |

| 0737-0-00-15-00-00-03-0 | BRASS, GOLD FINISH, PCB TERMINAL |

| 935261430551 | 8-BIT, MROM, 25 MHz, MICROCONTROLLER, PQFP64 |

| 935261430557 | 8-BIT, MROM, 25 MHz, MICROCONTROLLER, PQFP64 |

| 935262073518 | 8-BIT, MROM, 25 MHz, MICROCONTROLLER, PQFP44 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 935264217557 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC |

| 935267356112 | 制造商:NXP Semiconductors 功能描述:IC TEA1507PN |

| 935268081112 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC |

| 935268721125 | 制造商:NXP Semiconductors 功能描述:Buffer/Line Driver 1-CH Non-Inverting 3-ST CMOS 5-Pin TSSOP T/R |

| 935269304128 | 制造商:ST-Ericsson 功能描述:IC AUDIO CODEC W/TCH SCRN 48LQFP |

发布紧急采购,3分钟左右您将得到回复。