- 您现在的位置:买卖IC网 > PDF目录122717 > 935263686518 (NXP SEMICONDUCTORS) 6 CHANNEL(S), 200M bps, SERIAL COMM CONTROLLER, PQFP64 PDF资料下载

参数资料

| 型号: | 935263686518 |

| 厂商: | NXP SEMICONDUCTORS |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 6 CHANNEL(S), 200M bps, SERIAL COMM CONTROLLER, PQFP64 |

| 封装: | 10 X 10 MM, 1.40 MM HEIGHT, PLASTIC, SOT-314-2, LQFP-64 |

| 文件页数: | 6/22页 |

| 文件大小: | 170K |

| 代理商: | 935263686518 |

Philips Semiconductors

Preliminary specification

PDI1394P11A

3-port physical layer interface

1999 Mar 10

14

18.17

Current setting resistor (R[0:1],

pins [59,60])

An internal reference voltage is applied across the resistor

connected between these two pins to set the internal operating and

the cable driver output currents. A low TCR (<150ppm/

°C

temperature coefficient) with a value of 6.34 k

±1% should be used

to meet the 1394 standard output voltage limits.

18.18

Isolation Barrier disable (ISO–, pin 62)

When ISO– is high, busholder circuits are enabled on the LREQ,

PD, and LPS input pins and on the CTL, and Data bidirectional pins.

This mode also allows isolation using a single 1nF capacitor per

signal line. Details for this kind of isolation can be found in the

Philips Isolation Application Note AN2452. When ISO– is low,

busholder circuits are disabled and isolation can be realized by

using the scheme explained in Annex J of the 1394–1995 spec.

18.19

Supply filters (AVDD, pins [24, 25, 51, 55],

DVDD, pins [5,6,19,20], and PLLVDD, pin 58)

A combination of decoupling capacitors is suggested for each

supply group, such as paralleled 10

F and 0.1 F. The high

frequency 0.1

F capacitors should be mounted as close as

possible to the PDI1394P11A device supply leads. These supply

lines are separated on the IC to provide noise isolation. They should

be tied together at a low impedance point on the circuit board.

Individual filter networks are desirable.

Details of a phy-link Interface supporting an optional isolation barrier

are provided in Annex J of the 1394 standard.

19.0

PRINCIPLES OF OPERATION

The PDI1394P11A is designed to operate with a link layer controller.

These devices use an interface such as described in Annex J of the

1394 standard. The following describes the operation of the phy-link

interface.

19.1

Data Transfer and Clock rates

The PDI1394P11A supports 100/200 Mbit/s data transfer, and has

four bi-directional data lines D[0:3] crossing the interface. In 100

Mbit/s operation only D[0:1] pins are used, in 200 Mbit/s operations

all D[0:3] pins are used for data transfer. The unused D[n] pins are

driven low. In addition there are two bi-directional control lines CTL[0:1],

the 50 MHz SYSCLK line from the phy to the link, and the link request

line LREQ from the link to the phy. The PDI1394P11A has control of

all the bi-directional pins. The link is allowed to drive these pins only

after it has been given permission by the phy. The dedicated LREQ

request pin is used by the link for any activity which it wishes to

initiate.

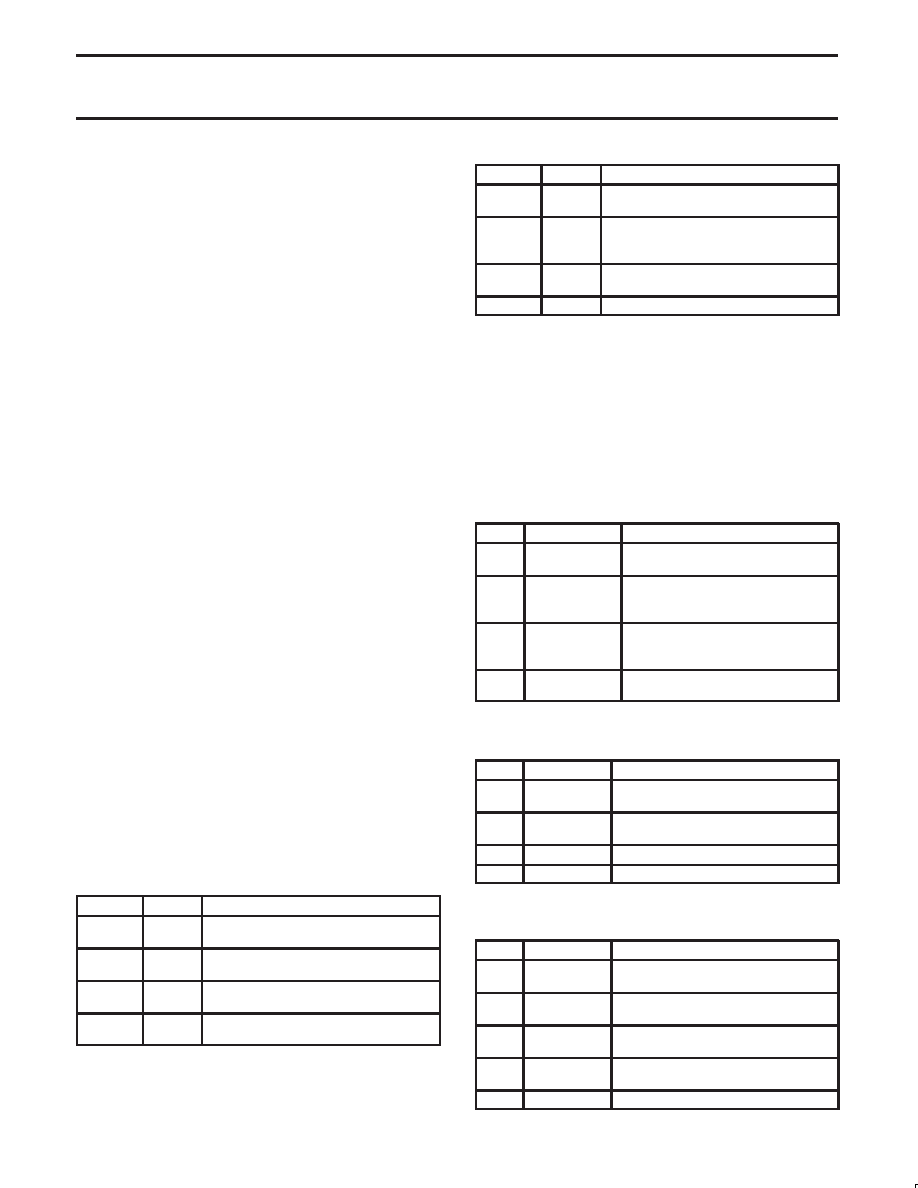

When the phy has control of the bus the CTL[0:1] lines are encoded

as follows:

CTL [0:1]

NAME

DESCRIPTION OF ACTIVITY

00

Idle

No activity is occurring (this is the default

mode).

01

Status

Status information is being sent from the

phy to the link.

10

Receive

An incoming packet is being sent from the

phy to the link.

11

Grant

The link has been given control of the bus

to send an outgoing packet.

When the link has control of the bus (phy permission) the CTL[0:1]

lines are encoded as follows:

CTL [0:1]

NAME

DESCRIPTION OF ACTIVITY

00

Idle

The link releases the bus (transmission

has been completed).

01

Hold

The link is holding the bus while data is

being prepared for transmission or

sending another packet without arbitrating.

10

Transmit

An outgoing packet is being sent from the

link to the phy.

11

NA

None

19.2

Request

When the link layer controller wishes to request the bus, or access a

register that is located in the PDI1394P11A, a serial stream of

information is sent across the LREQ line. The length of the stream

will vary depending on whether the transfer is a bus request, a read

command, or a write command. Regardless of the type of transfer, a

start bit of 1 is required at the beginning of the stream, and a stop bit

of 0 is required at the end of the stream. Bit 0 is the most significant,

and is transmitted first. The LREQ line will be required to idle low

(logic level 0).

19.2.1

Link Layer Controller Bus Request

For a Bus Request, the length of the LREQ data stream is 7 bits as

follows:

BIT(S)

NAME

DESCRIPTION

0

Start Bit

Indicates the beginning of the transfer

(always 1)

1–3

Request Type

Indicates the type of bus request (see

the table below for the encoding of this

field)

4–5

Request Speed

This should be 00 for PDI1394P11A’s

100 Mbit/s speed and 01 for

200 Mbit/s speed.

6

Stop Bit

Indicates the end of the transfer

(always 0)

19.2.2

Link Layer Controller Requests Read Register Access

For a Read Register Request, the length of the LREQ data stream is

9 bits as follows:

BIT(S)

NAME

DESCRIPTION

0

Start Bit

Indicates the beginning of the transfer

(always 1)

1–3

Request Type

Always a 100 indicating that this is a

read register request

4–7

Address

The address of the phy register to be read

8

Stop Bit

Indicates the end of the transfer (always 0)

19.2.3

Link Layer Controller Requests Write Register Access

For a Write Register Request, the length of the LREQ data stream is

17 bits. The details of bits are as shown below:

BIT(S)

NAME

DESCRIPTION

0

Start Bit

Indicates the beginning of the transfer

(always 1)

1–3

Request Type

Always a 101 indicating that this is a

write register request

4–7

Address

The address of the phy register to be

written to

8–15

Data

The data that is to be written to the

specified register address

16

Stop Bit

Indicates the end of the transfer (always 0)

相关PDF资料 |

PDF描述 |

|---|---|

| 9154A-04CS16 | 100 MHz, OTHER CLOCK GENERATOR, PDSO16 |

| 9212AF-13 | 533.3 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO24 |

| 9248BF-138LF | 166.67 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| 9250BF-28LF-T | 133.32 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 932S208DGLF | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 935264217557 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC |

| 935267356112 | 制造商:NXP Semiconductors 功能描述:IC TEA1507PN |

| 935268081112 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC |

| 935268721125 | 制造商:NXP Semiconductors 功能描述:Buffer/Line Driver 1-CH Non-Inverting 3-ST CMOS 5-Pin TSSOP T/R |

| 935269304128 | 制造商:ST-Ericsson 功能描述:IC AUDIO CODEC W/TCH SCRN 48LQFP |

发布紧急采购,3分钟左右您将得到回复。