- 您现在的位置:买卖IC网 > PDF目录122717 > 935263686518 (NXP SEMICONDUCTORS) 6 CHANNEL(S), 200M bps, SERIAL COMM CONTROLLER, PQFP64 PDF资料下载

参数资料

| 型号: | 935263686518 |

| 厂商: | NXP SEMICONDUCTORS |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 6 CHANNEL(S), 200M bps, SERIAL COMM CONTROLLER, PQFP64 |

| 封装: | 10 X 10 MM, 1.40 MM HEIGHT, PLASTIC, SOT-314-2, LQFP-64 |

| 文件页数: | 9/22页 |

| 文件大小: | 170K |

| 代理商: | 935263686518 |

Philips Semiconductors

Preliminary specification

PDI1394P11A

3-port physical layer interface

1999 Mar 10

17

22.0

TRANSMIT

When the link wants to transmit information, it will first request

access to the bus through the LREQ pin. Once the phy receives this

request, it will arbitrate to gain control of the bus. When the phy wins

ownership of the serial bus, it will grant the bus to the link by

asserting the ‘transmit’ state on the CTL pins for at least one

SYSCLK cycle, followed by idle for one clock cycle.

The link will take control of the bus by asserting either ‘hold’ or

‘transmit’ on the CTL lines. ‘hold’ is used by the link to keep control

of the bus if it needs some time to prepare the data for transmission.

The phy will keep control of the bus for the link by asserting a

‘data-prefix’ state on the bus. It is not necessary for the link to use

‘hold’ if it is ready to transmit as soon as bus ownership is granted.

When the link is prepared to send data, it will assert ‘transmit’ on the

CTL lines as well as sending the first four bits of the packet on the

D[0:3] lines (assuming 200 Mb/s). The ‘transmit’ state is held on the

CTL pins until the last bits of data have been sent. The link will then

assert ‘Idle’ on the CTL lines for one clock cycle after which it

releases control of the interface.

However, there will be times when the link will need to send another

packet without releasing the bus. For example, the link may want to

send consecutive isochronous packets or it may want to attach a

response to an acknowledgment. To do this, the link will assert ‘hold’

instead of ‘Idle’ when the first packet of data has been completely

transmitted. ‘Hold’, in this case, informs the phy that the link needs

to send another packet without releasing control of the bus. The phy

will then wait a set amount of time before asserting ‘transmit’. The

link can then proceed with the transmittal of the second packet. After

all data has been transmitted and the link has asserted ‘Idle’ on the

CTL pins, the phy will assert its own ‘Idle’ state on the CTL lines.

When sending multiple packets in this fashion, it is required that all

data be transmitted at the same speed. This is required because the

transmission speed is set during arbitration and since the arbitration

step will be skipped, there will be no way of informing the network of

a change in speed.

The PDI1394P11A includes a digital camera/single port Phy

interoperability enhancement. When a node is root (and

consequently cycle master) and is sending Isochronous data, it does

not need to arbitrate for the bus (by default it would win any such

arbitration). This fact was overlooked by some early 100 Mbps

single port Phy manufacturers whose chips are too slow to handle

the absence of the arbitration time. This causes their Phys to see a

header CRC error and the packet to be discarded. The

PDI1394P11A compensates for this by extending the Data_Prefix

time before sending the packet. This makes the PDI1394P11A fully

compatible with all existing 100 Mbps Phys on the market.

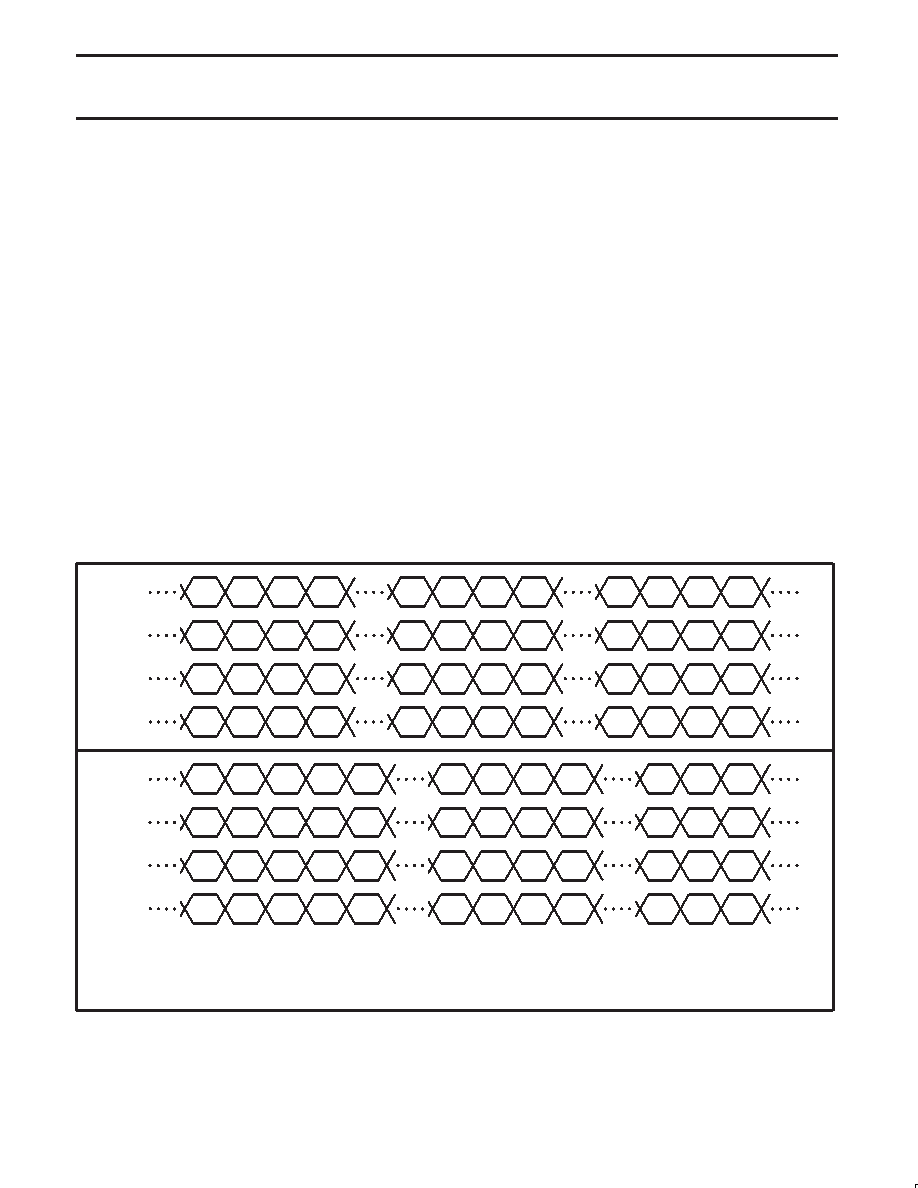

22.1

TRANSMIT TIMING WAVEFORMS

00

PHY

CTL [0:1]

11

00

ZZ

00

SV00235

ZZ

0000

PHY

D [0:3]

0000

ZZZZ

0000

ZZZZ

ZZ

LINK

CTL [0:1]

ZZ

10

00

01

ZZ

10

00

ZZZZ

LINK

D [0:3]

ZZZZ

P2

Pn

0000

ZZZZ

P0

P1

0000

ZZ

PHY

CTL [0:1]

ZZ

00

ZZ

11

00

ZZ

00

ZZZZ

PHY

D [0:3]

ZZZZ

0000

ZZZZ

0000

ZZZZ

0000

10

LINK

CTL [0:1]

10

01

10

ZZ

00

ZZ

10

ZZ

Pn–1

LINK

CTL [0:1]

Pn

0000

P0

ZZZZ

0000

ZZZZ

P1

ZZZZ

NOTE:

ZZ = High Impedance State

P0 Pn = Packet Data

NOTE:

ZZ = High Impedance State

P0 => Pn = Packet data

Figure 10.

Transmit Timing Waveforms

相关PDF资料 |

PDF描述 |

|---|---|

| 9154A-04CS16 | 100 MHz, OTHER CLOCK GENERATOR, PDSO16 |

| 9212AF-13 | 533.3 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO24 |

| 9248BF-138LF | 166.67 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| 9250BF-28LF-T | 133.32 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 932S208DGLF | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 935264217557 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC |

| 935267356112 | 制造商:NXP Semiconductors 功能描述:IC TEA1507PN |

| 935268081112 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC |

| 935268721125 | 制造商:NXP Semiconductors 功能描述:Buffer/Line Driver 1-CH Non-Inverting 3-ST CMOS 5-Pin TSSOP T/R |

| 935269304128 | 制造商:ST-Ericsson 功能描述:IC AUDIO CODEC W/TCH SCRN 48LQFP |

发布紧急采购,3分钟左右您将得到回复。