- 您现在的位置:买卖IC网 > PDF目录25563 > 9DB102AGILF (INTEGRATED DEVICE TECHNOLOGY INC) PLL BASED CLOCK DRIVER, PDSO20 PDF资料下载

参数资料

| 型号: | 9DB102AGILF |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟及定时 |

| 英文描述: | PLL BASED CLOCK DRIVER, PDSO20 |

| 封装: | 4.40 MM, 0.65 MM PITCH, ROHS COMPLIANT, MO-153, TSSOP-20 |

| 文件页数: | 12/13页 |

| 文件大小: | 223K |

| 代理商: | 9DB102AGILF |

IDTTM

Two Output Differential Buffer for PCIe Gen1 & Gen2

852

REV J 01/15/10

ICS9DB102

Two Output Differential Buffer for PCIe Gen1 & Gen2

8

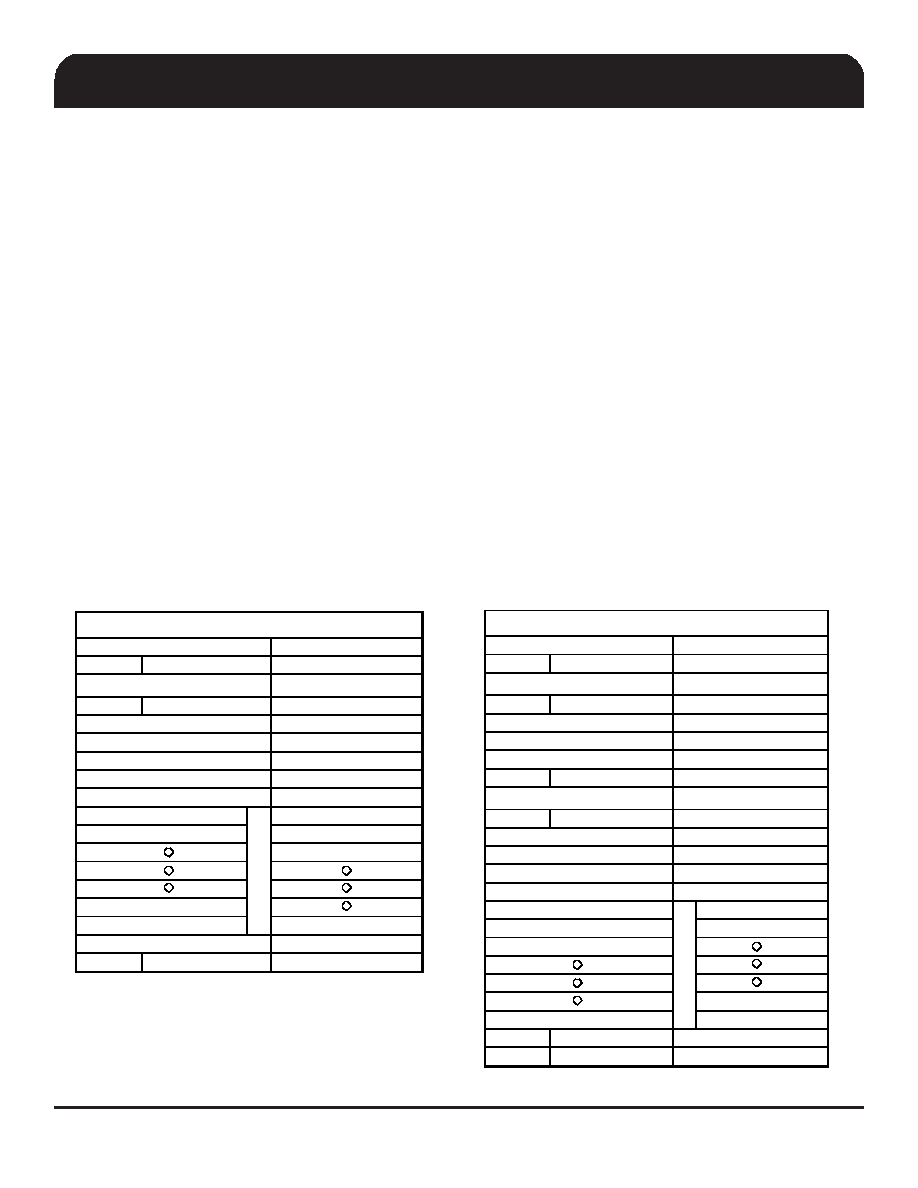

General SMBus serial interface information for the ICS9DB102

How to Write:

Controller (host) sends a start bit.

Controller (host) sends the write address D4

(h)

ICS clock will

acknowledge

Controller (host) sends the begining byte location = N

ICS clock will

acknowledge

Controller (host) sends the data byte count = X

ICS clock will

acknowledge

Controller (host) starts sending

Byte N through

Byte N + X -1

ICS clock will

acknowledge each byte one at a time

Controller (host) sends a Stop bit

How to Read:

Controller (host) will send start bit.

Controller (host) sends the write address D4

(h)

ICS clock will

acknowledge

Controller (host) sends the begining byte

location = N

ICS clock will

acknowledge

Controller (host) will send a separate start bit.

Controller (host) sends the read address D5

(h)

ICS clock will

acknowledge

ICS clock will send the data byte count = X

ICS clock sends

Byte N + X -1

ICS clock sends

Byte 0 through byte X (if X

(h)

was written to byte 8).

Controller (host) will need to acknowledge each byte

Controllor (host) will send a not acknowledge bit

Controller (host) will send a stop bit

ICS (Slave/Receiver)

T

WR

ACK

P

Byte N + X - 1

Data Byte Count = X

Beginning Byte N

stoP bit

X

B

yt

e

Index Block Write Operation

Slave Address D4(h)

Beginning Byte = N

WRite

starT bit

Controller (Host)

T

starT bit

WR

WRite

RT

Repeat starT

RD

ReaD

Beginning Byte N

Byte N + X - 1

N

Not acknowledge

PstoP bit

ICS (Slave/Receiver)

Controller (Host)

X

Byte

ACK

Data Byte Count = X

ACK

Slave Address D5(h)

Index Block Read Operation

Slave Address D4(h)

Beginning Byte = N

ACK

相关PDF资料 |

PDF描述 |

|---|---|

| 9DB102AGLF | PLL BASED CLOCK DRIVER, PDSO20 |

| 9DB102AFLFT | PLL BASED CLOCK DRIVER, PDSO20 |

| 9DB102AFLF | PLL BASED CLOCK DRIVER, PDSO20 |

| 9DB102AGLFT | PLL BASED CLOCK DRIVER, PDSO20 |

| 9DB102BFILF | 9DB SERIES, PLL BASED CLOCK DRIVER, 2 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO20 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 9DB102BFILF | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:Two Output Differential Buffer for PCIe Gen1 & Gen2 |

| 9DB102BFILFT | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:Two Output Differential Buffer for PCIe Gen1 & Gen2 |

| 9DB102BFLF | 功能描述:时钟缓冲器 2 OUTPUT PCIE GEN2 BUFFER RoHS:否 制造商:Texas Instruments 输出端数量:5 最大输入频率:40 MHz 传播延迟(最大值): 电源电压-最大:3.45 V 电源电压-最小:2.375 V 最大功率耗散: 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:LLP-24 封装:Reel |

| 9DB102BFLFT | 功能描述:时钟缓冲器 2 OUTPUT PCIE GEN2 BUFFER RoHS:否 制造商:Texas Instruments 输出端数量:5 最大输入频率:40 MHz 传播延迟(最大值): 电源电压-最大:3.45 V 电源电压-最小:2.375 V 最大功率耗散: 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:LLP-24 封装:Reel |

| 9DB102BGILF | 功能描述:时钟缓冲器 2 OUTPUT PCIE GEN2 BUFFER RoHS:否 制造商:Texas Instruments 输出端数量:5 最大输入频率:40 MHz 传播延迟(最大值): 电源电压-最大:3.45 V 电源电压-最小:2.375 V 最大功率耗散: 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:LLP-24 封装:Reel |

发布紧急采购,3分钟左右您将得到回复。