参数资料

| 型号: | A1240A-TQ176C |

| 厂商: | Microsemi SoC |

| 文件页数: | 13/54页 |

| 文件大小: | 0K |

| 描述: | IC FPGA 4K GATES 176-TQFP COM |

| 标准包装: | 40 |

| 系列: | ACT™ 2 |

| LAB/CLB数: | 684 |

| 输入/输出数: | 104 |

| 门数: | 4000 |

| 电源电压: | 4.5 V ~ 5.5 V |

| 安装类型: | 表面贴装 |

| 工作温度: | 0°C ~ 70°C |

| 封装/外壳: | 176-LQFP |

| 供应商设备封装: | 176-TQFP(24x24) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页当前第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页

Detailed Specifications

2- 14

R e visio n 8

A1225A Timing Characteristics (continued)

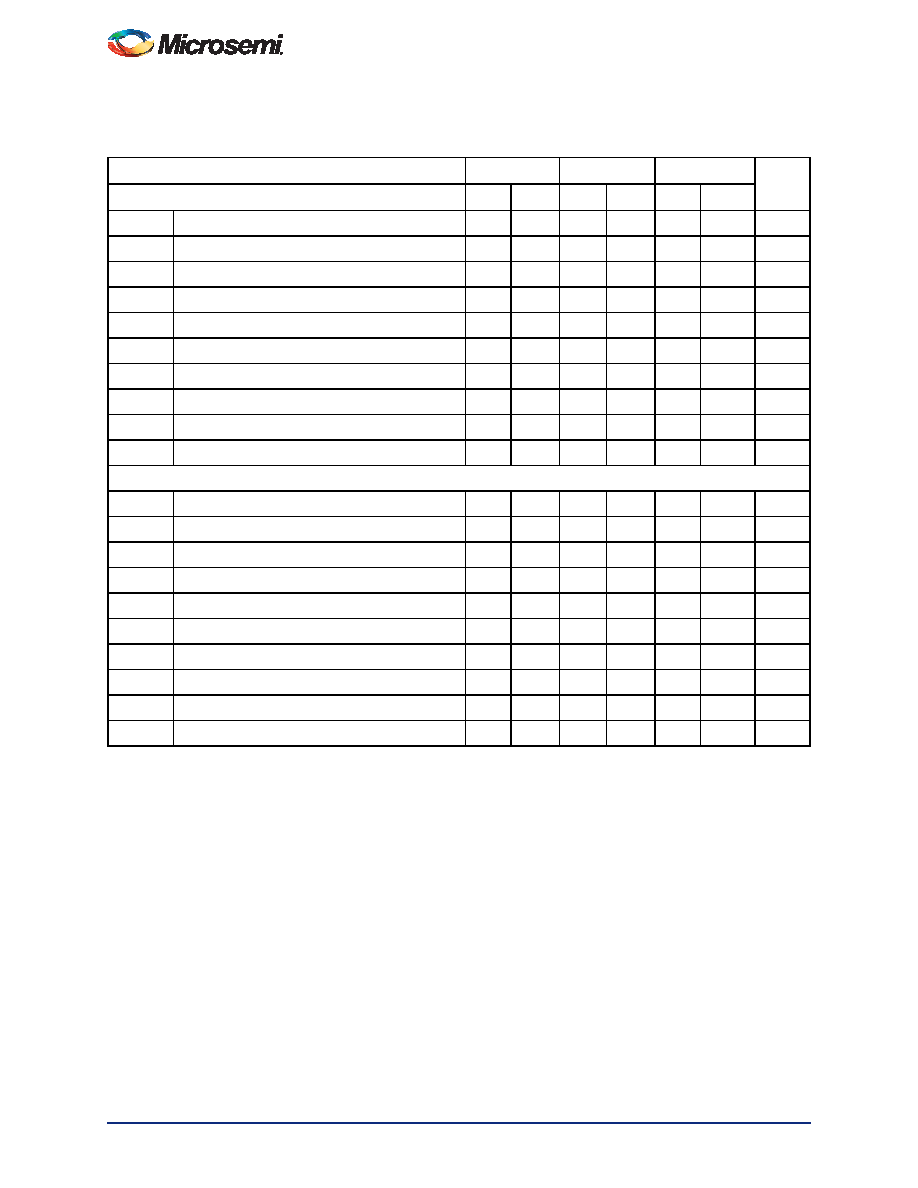

Table 2-14 A1225A Worst-Case Commercial Conditions, VCC = 4.75 V, TJ = 70°C

TTL Output Module Timing1

–2 Speed

–1 Speed

Std. Speed

Units

Parameter/Description

Min.

Max.

Min.

Max.

Min.

Max.

tDLH

Data to Pad High

8.0

9.0

10.6

ns

tDHL

Data to Pad Low

10.1

11.4

13.4

ns

tENZH

Enable Pad Z to High

8.9

10.0

11.8

ns

tENZL

Enable Pad Z to Low

11.6

13.2

15.5

ns

tENHZ

Enable Pad High to Z

7.1

8.0

9.4

ns

tENLZ

Enable Pad Low to Z

8.3

9.5

11.1

ns

tGLH

G to Pad High

8.9

10.2

11.9

ns

tGHL

G to Pad Low

11.2

12.7

14.9

ns

dTLH

Delta Low to High

0.07

0.08

0.09

ns/pF

dTHL

Delta High to Low

0.12

0.13

0.16

ns/pF

CMOS Output Module Timing1

tDLH

Data to Pad High

10.1

11.5

13.5

ns

tDHL

Data to Pad Low

8.4

9.6

11.2

ns

tENZH

Enable Pad Z to High

8.9

10.0

11.8

ns

tENZL

Enable Pad Z to Low

11.6

13.2

15.5

ns

tENHZ

Enable Pad High to Z

7.1

8.0

9.4

ns

tENLZ

Enable Pad Low to Z

8.3

9.5

11.1

ns

tGLH

G to Pad High

8.9

10.2

11.9

ns

tGHL

G to Pad Low

11.2

12.7

14.9

ns

dTLH

Delta Low to High

0.12

0.13

0.16

ns/pF

dTHL

Delta High to Low

0.09

0.10

0.12

ns/pF

Notes:

1. Delays based on 50 pF loading.

2. SSO information can be found at www.microsemi.com/soc/techdocs/appnotes/board_consideration.aspx.

相关PDF资料 |

PDF描述 |

|---|---|

| A1240A-TQG176C | IC FPGA 4K GATES 176-TQFP COM |

| AX1000-1BGG729I | IC FPGA AXCELERATOR 1M 729-PBGA |

| AX1000-1BG729I | IC FPGA AXCELERATOR 1M 729-PBGA |

| EP1S10F484I6N | IC STRATIX FPGA 10K LE 484-FBGA |

| EP1S10F484C5N | IC STRATIX FPGA 10K LE 484-FBGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| A1240A-TQ176I | 制造商:MICROSEMI 制造商全称:Microsemi Corporation 功能描述:ACT 2 Family FPGAs |

| A1240A-TQ176M | 制造商:MICROSEMI 制造商全称:Microsemi Corporation 功能描述:ACT 2 Family FPGAs |

| A1240A-TQG160B | 制造商:MICROSEMI 制造商全称:Microsemi Corporation 功能描述:ACT 2 Family FPGAs |

| A1240A-TQG160C | 制造商:MICROSEMI 制造商全称:Microsemi Corporation 功能描述:ACT 2 Family FPGAs |

| A1240A-TQG160I | 制造商:MICROSEMI 制造商全称:Microsemi Corporation 功能描述:ACT 2 Family FPGAs |

发布紧急采购,3分钟左右您将得到回复。