参数资料

| 型号: | A14100A-1RQ208I |

| 厂商: | Microsemi SoC |

| 文件页数: | 21/90页 |

| 文件大小: | 0K |

| 描述: | IC FPGA 10K GATES 208-PQFP |

| 标准包装: | 24 |

| 系列: | ACT™ 3 |

| LAB/CLB数: | 1377 |

| 输入/输出数: | 175 |

| 门数: | 10000 |

| 电源电压: | 4.5 V ~ 5.5 V |

| 安装类型: | 表面贴装 |

| 工作温度: | -40°C ~ 85°C |

| 封装/外壳: | 208-BFQFP 裸露焊盘 |

| 供应商设备封装: | 208-RQFP(28x28) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页当前第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页

Detailed Specifications

2- 20

R e visio n 3

Tightest Delay Distributions

Propagation delay between logic modules depends on the resistive and capacitive loading of the routing

tracks, the interconnect elements, and the module inputs being driven. Propagation delay increases as

the length of routing tracks, the number of interconnect elements, or the number of inputs increases.

From a design perspective, the propagation delay can be statistically correlated or modeled by the fanout

(number of loads) driven by a module. Higher fanout usually requires some paths to have longer lengths

of routing track. The ACT 3 family delivers the tightest fanout delay distribution of any FPGA. This tight

distribution is achieved in two ways: by decreasing the delay of the interconnect elements and by

decreasing the number of interconnect elements per path.

Microsemi’s patented PLICE antifuse offers a very low resistive/capacitive interconnect. The ACT 3

family’s antifuses, fabricated in 0.8 micron m lithography, offer nominal levels of 200

Ω resistance and 6

femtofarad (fF) capacitance per antifuse. The ACT 3 fanout distribution is also tighter than alternative

devices due to the low number of antifuses required per interconnect path. The ACT 3 family’s

proprietary architecture limits the number of antifuses per path to only four, with 90% of interconnects

using only two antifuses.

The ACT 3 family’s tight fanout delay distribution offers an FPGA design environment in which fanout can

be traded for the increased performance of reduced logic level designs. This also simplifies performance

estimates when designing with ACT 3 devices.

Timing Characteristics

Timing characteristics for ACT 3 devices fall into three categories: family dependent, device dependent,

and design dependent. The input and output buffer characteristics are common to all ACT 3 family

members. Internal routing delays are device dependent. Design dependency means actual delays are

not determined until after placement and routing of the user’s design is complete. Delay values may then

be determined by using the ALS Timer utility or performing simulation with post-layout delays.

Critical Nets and Typical Nets

Propagation delays are expressed only for typical nets, which are used for initial design performance

evaluation. Critical net delays can then be applied to the most time-critical paths. Critical nets are

determined by net property assignment prior to placement and routing. Up to 6% of the nets in a design

may be designated as critical, while 90% of the nets in a design are typical.

Long Tracks

Some nets in the design use long tracks. Long tracks are special routing resources that span multiple

rows, columns, or modules. Long tracks employ three and sometimes four antifuse connections. This

increases capacitance and resistance, result ng in longer net delays for macros connected to long tracks.

Typically up to 6% of nets in a fully utilized device require long tracks. Long tracks contribute

approximately 4 ns to 14 ns delay. This additional delay is represented statistically in higher fanout

(FO = 8) routing delays in the datasheet specifications section.

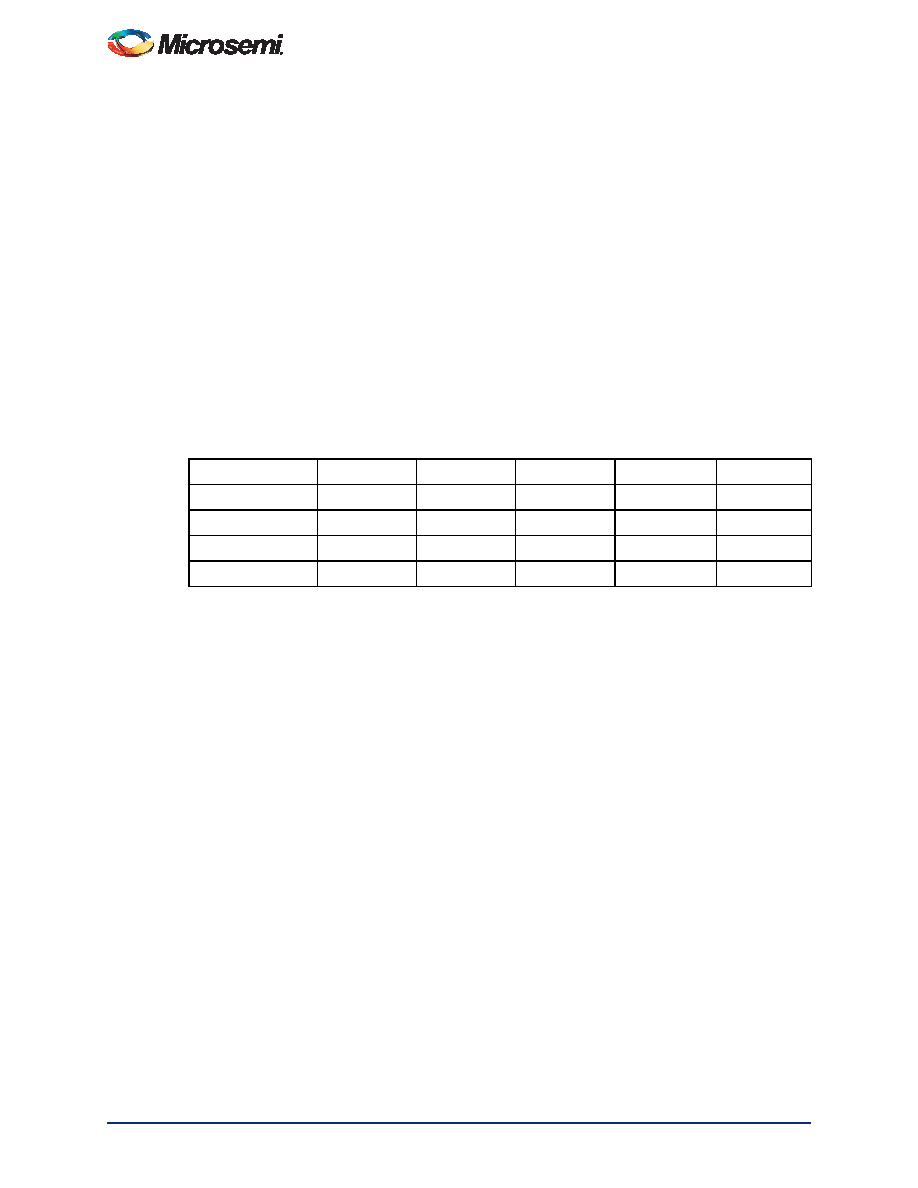

Table 2-14 Logic Module and Routing Delay by Fanout (ns); Worst-Case Commercial Conditions

Speed Grade

FO = 1

FO = 2

FO = 3

FO = 4

FO = 8

ACT 3 –3

2.9

3.2

3.4

3.7

4.8

ACT 3 –2

3.3

3.7

3.9

4.2

5.5

ACT 3 –1

3.7

4.2

4.4

4.8

6.2

ACT 3 STD

4.3

4.8

5.1

5.5

7.2

Notes:

1. Obtained by added tRD(x=FO) to tPD from the Logic Module Timing Characteristics Tables found in this

datasheet.

2. The –2 and –3 speed grades have been discontinued. Refer to

相关PDF资料 |

PDF描述 |

|---|---|

| ASC49DREI-S734 | CONN EDGECARD 98POS .100 EYELET |

| RBB106DHBT-S621 | EDGECARD 212POS DIP R/A .050 SLD |

| ASC50DRTF-S13 | CONN EDGECARD 100POS .100 EXTEND |

| AMC50DRTF-S13 | CONN EDGECARD 100POS .100 EXTEND |

| ASC50DREF-S13 | CONN EDGECARD 100POS .100 EXTEND |

相关代理商/技术参数 |

参数描述 |

|---|---|

| A14100A-2BG313C | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Field Programmable Gate Array (FPGA) |

| A14100A-2BG313I | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Field Programmable Gate Array (FPGA) |

| A14100A-2PG257C | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Field Programmable Gate Array (FPGA) |

| A14100A-2RQ208C | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Field Programmable Gate Array (FPGA) |

| A14100A-2RQ208I | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Field Programmable Gate Array (FPGA) |

发布紧急采购,3分钟左右您将得到回复。