- 您现在的位置:买卖IC网 > PDF目录17042 > A3PE-STARTER-KIT-2 (Microsemi SoC)KIT EVAL FOR A3PE1500 PROASIC3 PDF资料下载

参数资料

| 型号: | A3PE-STARTER-KIT-2 |

| 厂商: | Microsemi SoC |

| 文件页数: | 67/162页 |

| 文件大小: | 0K |

| 描述: | KIT EVAL FOR A3PE1500 PROASIC3 |

| 产品变化通告: | Kit/Part Number Change 25/Jul/2012 |

| 标准包装: | 1 |

| 系列: | ProASIC3 |

| 类型: | FPGA |

| 适用于相关产品: | A3PE1500 |

| 所含物品: | 板,电源,编程器 |

| 其它名称: | 1100-1144 A3PE-STARTER-KIT |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页当前第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页第155页第156页第157页第158页第159页第160页第161页第162页

ProASIC3E Flash Family FPGAs

Revision 13

5-9

Advance v0.5

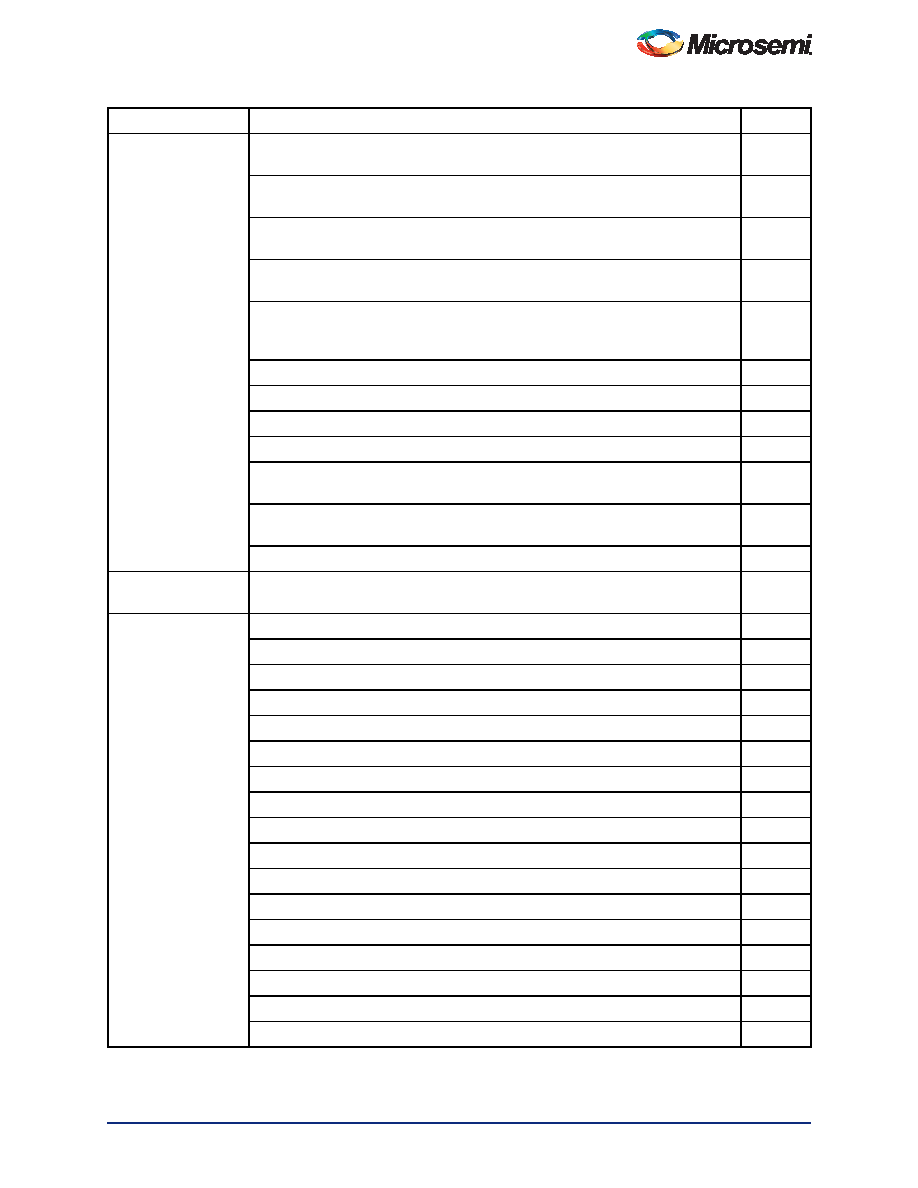

(continued)

The "I/O User Input/Output" pin description was updated to include information on

what happens when the pin is unused.

2-50

The "JTAG Pins" section was updated to include information on what happens

when the pin is unused.

2-51

The "Programming" section was updated to include information concerning

serialization.

2-53

The "JTAG 1532" section was updated to include SAMPLE/PRELOAD

information.

2-54

The "DC and Switching Characteristics" chapter was updated with new

information.

Starting

on page

3-1

Table 3-6 was updated.

3-5

In Table 3-10, PAC4 was updated.

3-8

Table 3-19 was updated.

3-20

The note in Table 3-24 was updated.

3-23

All Timing Characteristics tables were updated from LVTTL to Register Delays

3-26 to

3-64

The Timing Characteristics for RAM4K9, RAM512X18, and FIFO were updated.

3-74 to

3-79

FTCKMAX was updated in Table 3-98.

3-80

Advance v0.4

(October 2005)

The "Packaging Tables" table was updated.

ii

Advance v0.3

Figure 2-11 was updated.

2-9

The "Clock Resources (VersaNets)" section was updated.

2-9

The "VersaNet Global Networks and Spine Access" section was updated.

2-9

The "PLL Macro" section was updated.

2-15

Figure 2-27 was updated.

2-28

Figure 2-20 was updated.

2-19

Table 2-5 was updated.

2-25

Table 2-6 was updated.

2-25

The "FIFO Flag Usage Considerations" section was updated.

2-27

Table 2-33 was updated.

2-51

Figure 2-24 was updated.

2-31

The "Cold-Sparing Support" section is new.

2-34

Table 2-45 was updated.

2-64

Table 2-48 was updated.

2-81

Pin descriptions in the "JTAG Pins" section were updated.

2-51

The "Pin Descriptions" section was updated.

2-50

Table 3-7 was updated.

3-6

Revision

Changes

Page

相关PDF资料 |

PDF描述 |

|---|---|

| 0210490279 | CABLE JUMPER 1.25MM .051M 22POS |

| EBM22DCMD-S288 | CONN EDGECARD 44POS .156 EXTEND |

| ECA14DRMI-S288 | CONN EDGECARD 28POS .125 EXTEND |

| 0210490905 | CABLE JUMPER 1.25MM .102M 21POS |

| MPC8377E-RDBA | BOARD REF DES MPC8377 REV 2.1 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| A3PFA1X201J1 | 制造商:APEM 功能描述:Pushbutton,A3,latching,12V,red |

| A3PFA1X201J2 | 制造商:APEM 功能描述:Pushbutton,latching,12V,green |

| A3PFA1X201J3 | 制造商:APEM 功能描述:Pushbutton,latching,12V,amber |

| A3PFA1X201J4 | 制造商:APEM 功能描述:Pushbutton,A3,latching,12V,blue |

| A3PFA1X201K1 | 制造商:APEM 功能描述:Pushbutton,A3,latching 24V,red |

发布紧急采购,3分钟左右您将得到回复。