- 您现在的位置:买卖IC网 > PDF目录164971 > A3PE1500-PQG208 FPGA, 38400 CLBS, 1500000 GATES, PQFP208 PDF资料下载

参数资料

| 型号: | A3PE1500-PQG208 |

| 元件分类: | FPGA |

| 英文描述: | FPGA, 38400 CLBS, 1500000 GATES, PQFP208 |

| 封装: | 28 X 28 MM, 3.40 MM HEIGHT, 0.50 MM PITCH, GREEN, PLASTIC, QFP-208 |

| 文件页数: | 2/152页 |

| 文件大小: | 4932K |

| 代理商: | A3PE1500-PQG208 |

第1页当前第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页

ProASIC3E Device Family Overview

1- 6

v1.1

Pro I/Os with Advanced I/O Standards

The ProASIC3E family of FPGAs features a flexible I/O structure, supporting a range of voltages

(1.5 V, 1.8 V, 2.5 V, and 3.3 V). ProASIC3E FPGAs support 19 different I/O standards, including single-

ended, differential, and voltage-referenced. The I/Os are organized into banks, with eight banks

per device (two per side). The configuration of these banks determines the I/O standards

supported. Each I/O bank is subdivided into VREF minibanks, which are used by voltage-referenced

I/Os. VREF minibanks contain 8 to 18 I/Os. All the I/Os in a given minibank share a common VREF line.

Therefore, if any I/O in a given VREF minibank is configured as a VREF pin, the remaining I/Os in that

minibank will be able to use that reference voltage.

Each I/O module contains several input, output, and enable registers. These registers allow the

implementation of the following:

Single-Data-Rate applications (e.g., PCI 66 MHz, bidirectional SSTL 2 and 3, Class I and II)

Double-Data-Rate applications (e.g., DDR LVDS, B-LVDS, and M-LVDS I/Os for point-to-point

communications, and DDR 200 MHz SRAM using bidirectional HSTL Class II)

ProASIC3E banks support M-LVDS with 20 multi-drop points.

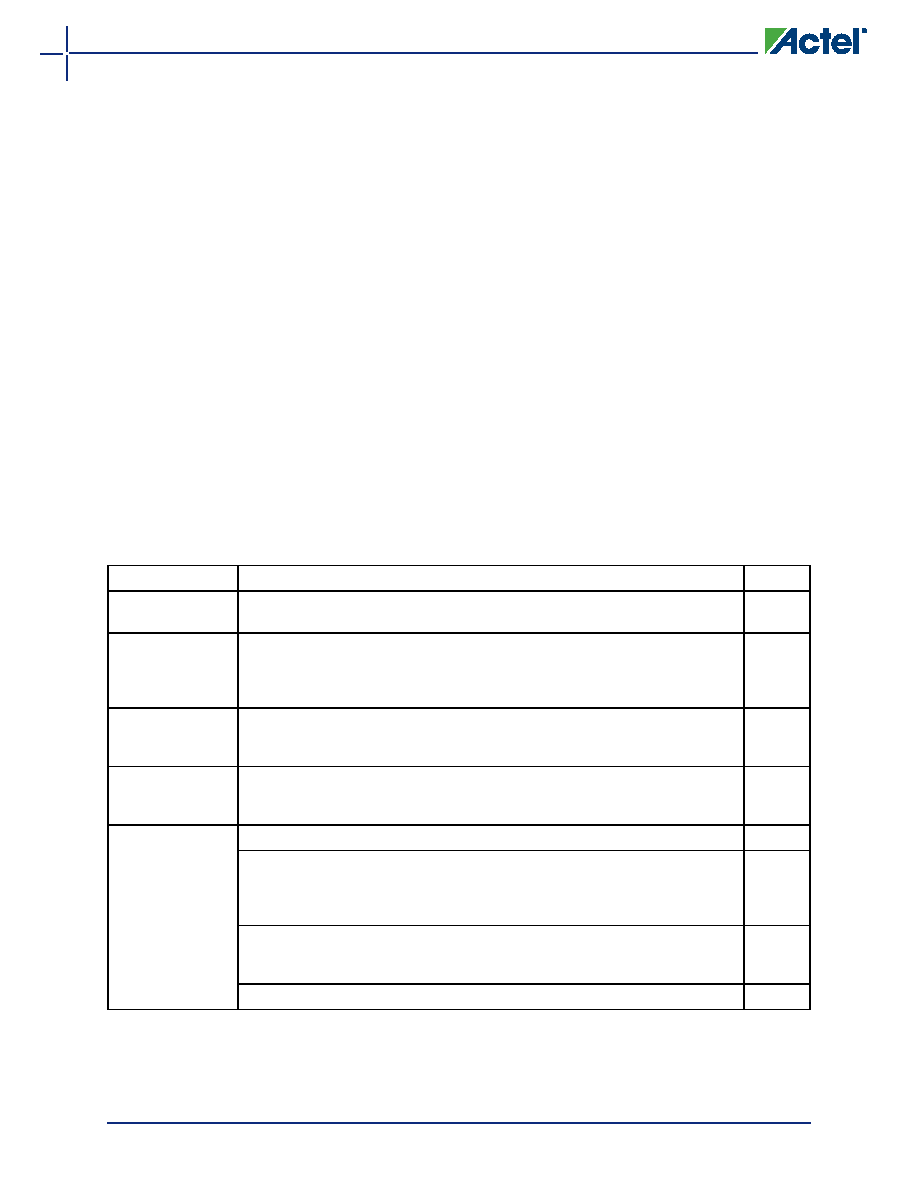

Part Number and Revision Date

Part Number 51700098-001-2

Revised February 2009

List of Changes

The following table lists critical changes that were made in the current version of the document.

Previous Version

Changes in Current Version (v1.1)

Page

v1.0

(March 2008)

51700098-001-1

This document was divided into two sections and given a version number,

starting at v1.0. The first section of the document includes features, benefits,

ordering information, and temperature and speed grade offerings. The second

section is a device family overview.

N/A

51700098-001-0

(January 2008)

The FG324 package was added to the "ProASIC3E Product Family" table, the

"I/Os Per Package1" table, and the "Temperature Grade Offerings" table for

A3PE3000.

v2.1

(July 2007)

This document was previously in datasheet v2.1. As a result of moving to the

handbook format, Actel has restarted the version numbers. The new version

number is 51700098-001-0.

N/A

v2.0

(April 2007)

CoreMP7 information was removed from the "Features and Benefits" section.

i

The M1 device part numbers have been updated in Table 4 ProASIC3E

Product Family, "Packaging Tables", "Temperature Grade Offerings", "Speed

Grade and Temperature Grade Matrix", and "Speed Grade and Temperature

Grade Matrix".

ii, iii,

iv, iv

The words "ambient temperature" were added to the temperature range in

the "Temperature Grade Offerings", "Speed Grade and Temperature Grade

Matrix", and "Speed Grade and Temperature Grade Matrix" sections.

iii, iv, iv

The "Clock Conditioning Circuit (CCC) and PLL" section was updated.

i

相关PDF资料 |

PDF描述 |

|---|---|

| A3PN060-FVQ100 | FPGA, 1536 CLBS, 60000 GATES, PQFP100 |

| A3PN060-FVQG100 | FPGA, 1536 CLBS, 60000 GATES, PQFP100 |

| A3PN060-ZFVQ100 | FPGA, 1536 CLBS, 60000 GATES, PQFP100 |

| A3PN060-ZFVQG100 | FPGA, 1536 CLBS, 60000 GATES, PQFP100 |

| A3PN125-FVQ100 | FPGA, 3072 CLBS, 125000 GATES, PQFP100 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| A3PE1500-PQG208I | 功能描述:IC FPGA 1KB FLASH 1.5M 208-PQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:ProASIC3E 产品培训模块:Three Reasons to Use FPGA's in Industrial Designs Cyclone IV FPGA Family Overview 特色产品:Cyclone? IV FPGAs 标准包装:60 系列:CYCLONE® IV GX LAB/CLB数:9360 逻辑元件/单元数:149760 RAM 位总计:6635520 输入/输出数:270 门数:- 电源电压:1.16 V ~ 1.24 V 安装类型:表面贴装 工作温度:0°C ~ 85°C 封装/外壳:484-BGA 供应商设备封装:484-FBGA(23x23) |

| A3PE1500-PQG896 | 制造商:ACTEL 制造商全称:Actel Corporation 功能描述:ProASIC3E Flash Family FPGAs |

| A3PE1500-PQG896ES | 制造商:ACTEL 制造商全称:Actel Corporation 功能描述:ProASIC3E Flash Family FPGAs |

| A3PE1500-PQG896I | 制造商:ACTEL 制造商全称:Actel Corporation 功能描述:ProASIC3E Flash Family FPGAs |

| A3PE1500-PQG896PP | 制造商:ACTEL 制造商全称:Actel Corporation 功能描述:ProASIC3E Flash Family FPGAs |

发布紧急采购,3分钟左右您将得到回复。