- 您现在的位置:买卖IC网 > PDF目录164971 > A3PN125-FVQG100 FPGA, 3072 CLBS, 125000 GATES, PQFP100 PDF资料下载

参数资料

| 型号: | A3PN125-FVQG100 |

| 元件分类: | FPGA |

| 英文描述: | FPGA, 3072 CLBS, 125000 GATES, PQFP100 |

| 封装: | 14 X 14 MM, 1.20 MM HEIGHT, 0.50 MM PITCH, ROHS COMPLIANT, VQFP-100 |

| 文件页数: | 13/92页 |

| 文件大小: | 3184K |

| 代理商: | A3PN125-FVQG100 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页当前第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页

ProASIC3 nano DC and Switching Characteristics

2- 6

A d vance v0.2

Calculating Power Dissipation

Quiescent Supply Current

Power per I/O Pin

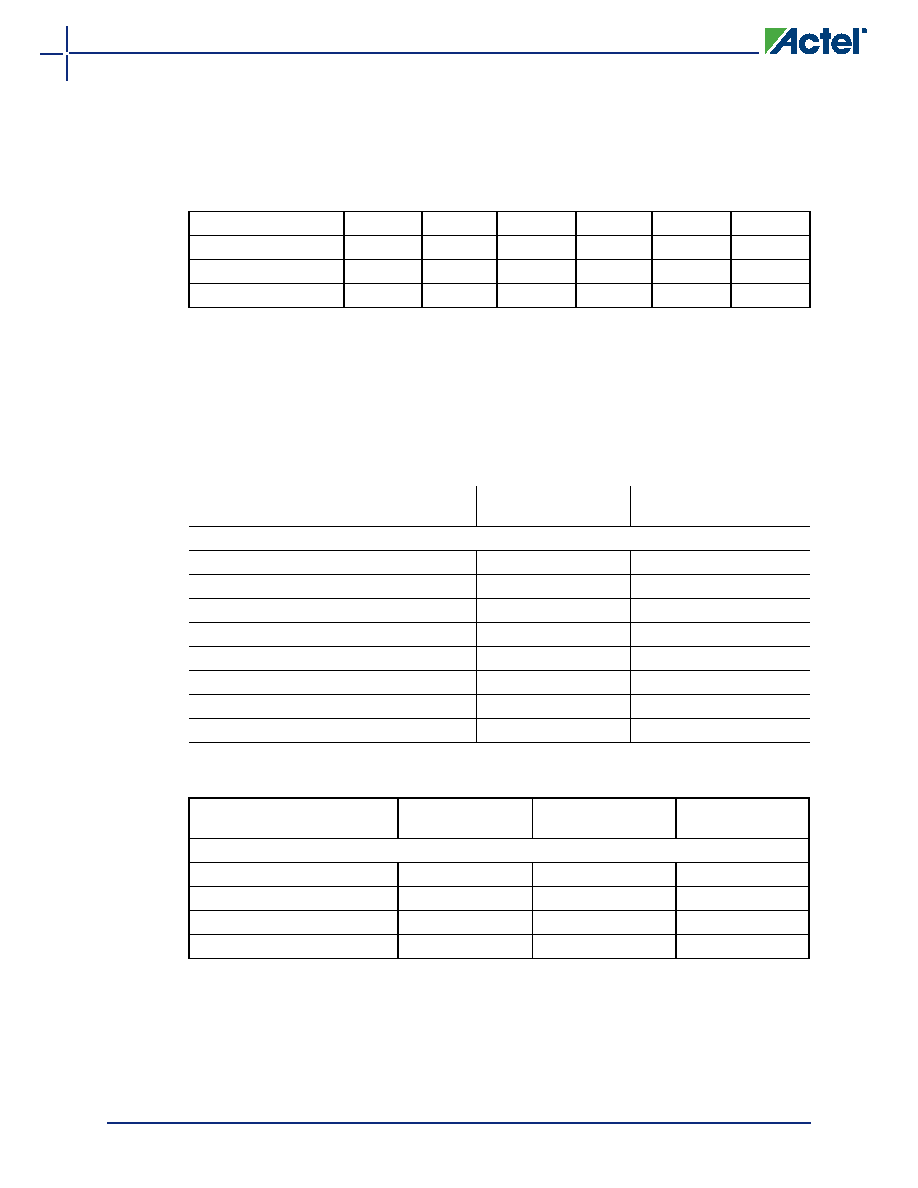

Table 2-7

Quiescent Supply Current Characteristics

A3PN010

A3PN015

A3PN020

A3PN060

A3PN125

A3PN250

Typical (25°C)

1 mA

2 mA

3 mA

Max. (Commercial)

5 mA

10 mA

20 mA

Max. (Industrial)

8 mA

15 mA

30 mA

Notes:

1. IDD Includes VCC, VPUMP, and VCCI, currents. Values do not include I/O static contribution, which

is shown in Table 2-9.

2. –F speed grade devices may experience higher standby IDD of up to five times the standard IDD

and higher I/O leakage.

Table 2-8

Summary of I/O Input Buffer Power (Per Pin) – Default I/O Software Settings

VCCI (V)

Dynamic Power

PAC9 (W/MHz)

*

Single-Ended

3.3 V LVTTL / 3.3 V LVCMOS

3.3

16.26

3.3 V LVTTL / 3.3 V LVCMOS – Schmitt Trigger

3.3

18.95

2.5 V LVCMOS

2.5

4.59

2.5 V LVCMOS – Schmitt Trigger

2.5

6.01

1.8 V LVCMOS

1.8

1.61

1.8 V LVCMOS – Schmitt Trigger

1.8

1.70

1.5 V LVCMOS (JESD8-11)

1.5

0.96

1.5 V LVCMOS (JESD8-11) – Schmitt Trigger

1.5

0.90

Note: *PAC9 is the total dynamic power measured on VCCI.

Table 2-9

Summary of I/O Output Buffer Power (per pin) – Default I/O Software Settings1

CLOAD (pF)

2

VCCI (V)

Dynamic Power

PAC10 (W/MHz)

3

Single-Ended

3.3 V LVTTL / 3.3 V LVCMOS

10

3.3

162.43

2.5 V LVCMOS

10

2.5

92.49

1.8 V LVCMOS

10

1.8

47.48

1.5 V LVCMOS (JESD8-11)

10

1.5

32.75

Notes:

1. Dynamic power consumption is given for standard load and software default drive strength

and output slew.

2. Values are for A3PN020, A3PN015, and A3PN010. A3PN060, A3PN125, and A3PN250 have a

default loading of 35 pF.

3. PAC10 is the total dynamic power measured on VCCI.

相关PDF资料 |

PDF描述 |

|---|---|

| A3PN125-ZFVQ100 | FPGA, 3072 CLBS, 125000 GATES, PQFP100 |

| A3PN125-ZFVQG100 | FPGA, 3072 CLBS, 125000 GATES, PQFP100 |

| A3PN125-1VQ100I | FPGA, 3072 CLBS, 125000 GATES, PQFP100 |

| A3PN125-1VQ100 | FPGA, 3072 CLBS, 125000 GATES, PQFP100 |

| A3PN125-1VQG100I | FPGA, 3072 CLBS, 125000 GATES, PQFP100 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| A3PN125-VQ100 | 功能描述:IC FPGA NANO 125K GATES 100-VQFP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:ProASIC3 nano 标准包装:152 系列:IGLOO PLUS LAB/CLB数:- 逻辑元件/单元数:792 RAM 位总计:- 输入/输出数:120 门数:30000 电源电压:1.14 V ~ 1.575 V 安装类型:表面贴装 工作温度:-40°C ~ 85°C 封装/外壳:289-TFBGA,CSBGA 供应商设备封装:289-CSP(14x14) |

| A3PN125-VQ100I | 功能描述:IC FPGA NANO 125K GATES 100-VQFP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:ProASIC3 nano 标准包装:152 系列:IGLOO PLUS LAB/CLB数:- 逻辑元件/单元数:792 RAM 位总计:- 输入/输出数:120 门数:30000 电源电压:1.14 V ~ 1.575 V 安装类型:表面贴装 工作温度:-40°C ~ 85°C 封装/外壳:289-TFBGA,CSBGA 供应商设备封装:289-CSP(14x14) |

| A3PN125-VQG100 | 功能描述:IC FPGA NANO 1024MAC 100VQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:ProASIC3 nano 标准包装:60 系列:XP LAB/CLB数:- 逻辑元件/单元数:10000 RAM 位总计:221184 输入/输出数:244 门数:- 电源电压:1.71 V ~ 3.465 V 安装类型:表面贴装 工作温度:0°C ~ 85°C 封装/外壳:388-BBGA 供应商设备封装:388-FPBGA(23x23) 其它名称:220-1241 |

| A3PN125-VQG100I | 功能描述:IC FPGA NANO 125K GATES 100-VQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:ProASIC3 nano 标准包装:152 系列:IGLOO PLUS LAB/CLB数:- 逻辑元件/单元数:792 RAM 位总计:- 输入/输出数:120 门数:30000 电源电压:1.14 V ~ 1.575 V 安装类型:表面贴装 工作温度:-40°C ~ 85°C 封装/外壳:289-TFBGA,CSBGA 供应商设备封装:289-CSP(14x14) |

| A3PN125-Z1VQ100 | 功能描述:IC FPGA NANO 125K GATES 100-VQFP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:ProASIC3 nano 标准包装:152 系列:IGLOO PLUS LAB/CLB数:- 逻辑元件/单元数:792 RAM 位总计:- 输入/输出数:120 门数:30000 电源电压:1.14 V ~ 1.575 V 安装类型:表面贴装 工作温度:-40°C ~ 85°C 封装/外壳:289-TFBGA,CSBGA 供应商设备封装:289-CSP(14x14) |

发布紧急采购,3分钟左右您将得到回复。