- 您现在的位置:买卖IC网 > PDF目录164971 > A3PN125-FVQG100 FPGA, 3072 CLBS, 125000 GATES, PQFP100 PDF资料下载

参数资料

| 型号: | A3PN125-FVQG100 |

| 元件分类: | FPGA |

| 英文描述: | FPGA, 3072 CLBS, 125000 GATES, PQFP100 |

| 封装: | 14 X 14 MM, 1.20 MM HEIGHT, 0.50 MM PITCH, ROHS COMPLIANT, VQFP-100 |

| 文件页数: | 70/92页 |

| 文件大小: | 3184K |

| 代理商: | A3PN125-FVQG100 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页当前第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页

ProASIC3 nano DC and Switching Characteristics

2- 58

Advance v0.2

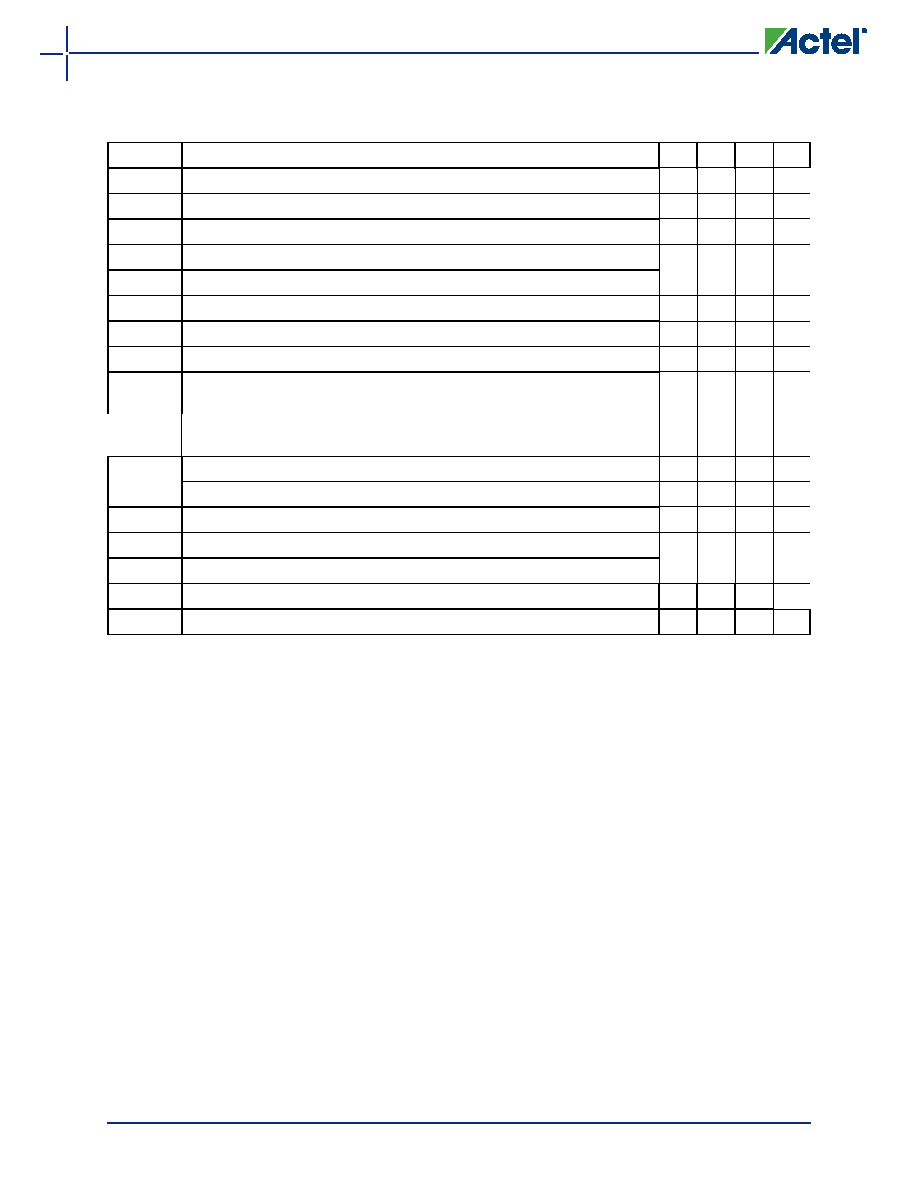

Table 2-71 RAM512X18

Commercial-Case Conditions: TJ = 70°C, Worst-Case VCC = 1.425 V

Parameter

Description

–2

–1

Std. Units

tAS

Address setup time

0.25 0.28 0.33

ns

tAH

Address hold time

0.00 0.00 0.00

ns

tENS

REN_B, WEN_B setup time

0.09 0.10 0.12

ns

tENH

REN_B, WEN_B hold time

0.06 0.07 0.08

ns

tDS

Input data (DI) setup time

0.18 0.21 0.25

ns

tDH

Input data (DI) hold time

0.00 0.00 0.00

ns

tCKQ1

Clock HIGH to new data valid on DO (output retained, WMODE = 0)

2.16 2.46 2.89

ns

tCKQ2

Clock HIGH to new data valid on DO (pipelined)

0.90 1.02 1.20

ns

tC2CRWH

Address collision clk-to-clk delay for reliable read access after write on same

address; applicable to opening edge

0.50 0.43 0.38

ns

tC2CWRH

Address collision clk-to-clk delay for reliable write access after read on same

address; applicable to opening edge

0.59 0.50 0.44

ns

tRSTBQ

RESET_B LOW to data out LOW on DO (flow-through)

0.92 1.05 1.23

ns

RESET_B LOW to data out LOW on DO (pipelined)

0.92 1.05 1.23

ns

tREMRSTB

RESET_B removal

0.29 0.33 0.38

ns

tRECRSTB

RESET_B recovery

1.50 1.71 2.01

ns

tMPWRSTB

RESET_B minimum pulse width

0.21 0.24 0.29

ns

tCYC

Clock cycle time

3.23 3.68 4.32

ns

FMAX

Maximum frequency

310

272

231 MHz

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-5 for

derating values.

相关PDF资料 |

PDF描述 |

|---|---|

| A3PN125-ZFVQ100 | FPGA, 3072 CLBS, 125000 GATES, PQFP100 |

| A3PN125-ZFVQG100 | FPGA, 3072 CLBS, 125000 GATES, PQFP100 |

| A3PN125-1VQ100I | FPGA, 3072 CLBS, 125000 GATES, PQFP100 |

| A3PN125-1VQ100 | FPGA, 3072 CLBS, 125000 GATES, PQFP100 |

| A3PN125-1VQG100I | FPGA, 3072 CLBS, 125000 GATES, PQFP100 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| A3PN125-VQ100 | 功能描述:IC FPGA NANO 125K GATES 100-VQFP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:ProASIC3 nano 标准包装:152 系列:IGLOO PLUS LAB/CLB数:- 逻辑元件/单元数:792 RAM 位总计:- 输入/输出数:120 门数:30000 电源电压:1.14 V ~ 1.575 V 安装类型:表面贴装 工作温度:-40°C ~ 85°C 封装/外壳:289-TFBGA,CSBGA 供应商设备封装:289-CSP(14x14) |

| A3PN125-VQ100I | 功能描述:IC FPGA NANO 125K GATES 100-VQFP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:ProASIC3 nano 标准包装:152 系列:IGLOO PLUS LAB/CLB数:- 逻辑元件/单元数:792 RAM 位总计:- 输入/输出数:120 门数:30000 电源电压:1.14 V ~ 1.575 V 安装类型:表面贴装 工作温度:-40°C ~ 85°C 封装/外壳:289-TFBGA,CSBGA 供应商设备封装:289-CSP(14x14) |

| A3PN125-VQG100 | 功能描述:IC FPGA NANO 1024MAC 100VQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:ProASIC3 nano 标准包装:60 系列:XP LAB/CLB数:- 逻辑元件/单元数:10000 RAM 位总计:221184 输入/输出数:244 门数:- 电源电压:1.71 V ~ 3.465 V 安装类型:表面贴装 工作温度:0°C ~ 85°C 封装/外壳:388-BBGA 供应商设备封装:388-FPBGA(23x23) 其它名称:220-1241 |

| A3PN125-VQG100I | 功能描述:IC FPGA NANO 125K GATES 100-VQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:ProASIC3 nano 标准包装:152 系列:IGLOO PLUS LAB/CLB数:- 逻辑元件/单元数:792 RAM 位总计:- 输入/输出数:120 门数:30000 电源电压:1.14 V ~ 1.575 V 安装类型:表面贴装 工作温度:-40°C ~ 85°C 封装/外壳:289-TFBGA,CSBGA 供应商设备封装:289-CSP(14x14) |

| A3PN125-Z1VQ100 | 功能描述:IC FPGA NANO 125K GATES 100-VQFP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:ProASIC3 nano 标准包装:152 系列:IGLOO PLUS LAB/CLB数:- 逻辑元件/单元数:792 RAM 位总计:- 输入/输出数:120 门数:30000 电源电压:1.14 V ~ 1.575 V 安装类型:表面贴装 工作温度:-40°C ~ 85°C 封装/外壳:289-TFBGA,CSBGA 供应商设备封装:289-CSP(14x14) |

发布紧急采购,3分钟左右您将得到回复。