- 您现在的位置:买卖IC网 > PDF目录379533 > A54SX08P-PQ208I (Electronic Theatre Controls, Inc.) LM1881 Video Sync Separator; Package: SOIC NARROW; No of Pins: 8 PDF资料下载

参数资料

| 型号: | A54SX08P-PQ208I |

| 厂商: | Electronic Theatre Controls, Inc. |

| 英文描述: | LM1881 Video Sync Separator; Package: SOIC NARROW; No of Pins: 8 |

| 中文描述: | 54SX家庭的FPGA |

| 文件页数: | 29/57页 |

| 文件大小: | 415K |

| 代理商: | A54SX08P-PQ208I |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页当前第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页

v3.1

29

5 4 S X F a m ily F P G A s

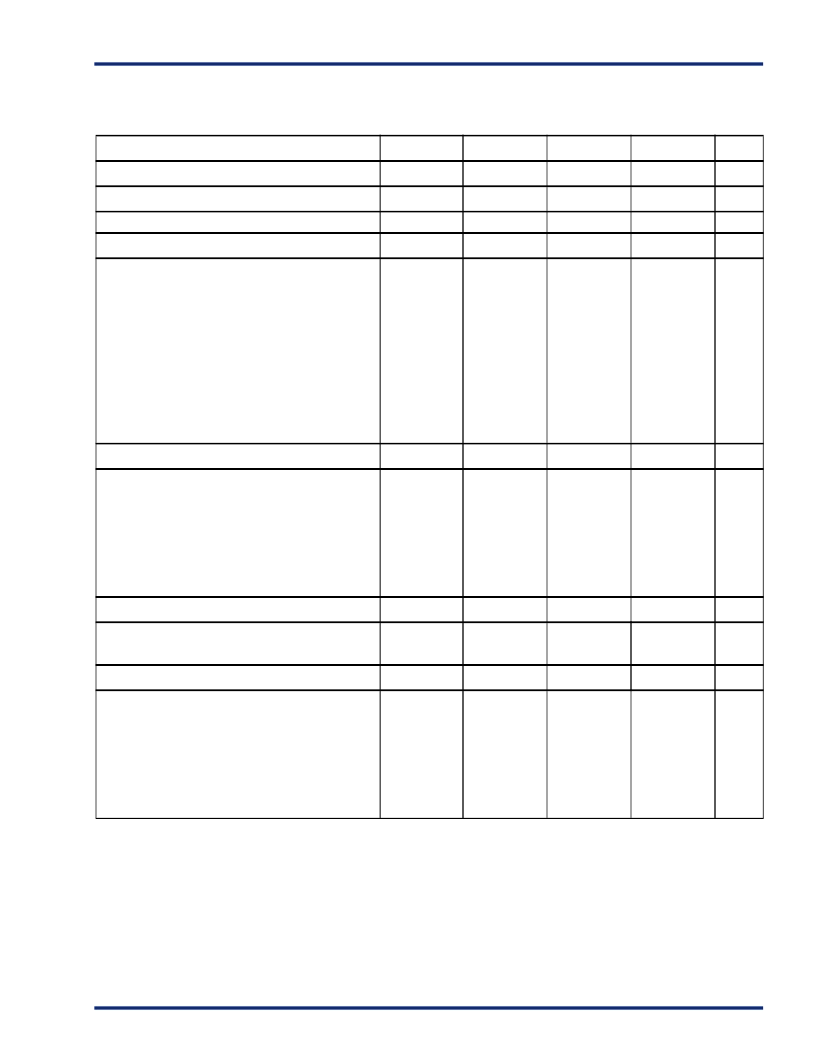

A 5 4 S X 1 6 P T im ing C ha ra c t e ris t ic s

(Wors t-C a s e C omme rc ia l C onditions , V

C C R

= 4 .75 V , V

C C A ,

V

C C I

= 3.0V , T

J

= 70

°

C )

‘–3’ Speed

‘–2’ Speed

‘–1’ Speed

‘Std’ Speed

Parameter

Description

Min.

Max.

Min.

Max.

Min.

Max.

Min.

Max.

Units

C-Cell Propagation Delays

1

t

PD

Predicted Routing Delays

2

Internal Array Module

0.6

0.7

0.8

0.9

ns

t

DC

FO=1 Routing Delay, Direct

Connect

0.1

0.1

0.1

0.1

ns

t

FC

t

RD1

t

RD2

t

RD3

t

RD4

t

RD8

t

RD12

FO=1 Routing Delay, Fast Connect

0.3

0.4

0.4

0.5

ns

FO=1 Routing Delay

0.3

0.4

0.4

0.5

ns

FO=2 Routing Delay

0.6

0.7

0.8

0.9

ns

FO=3 Routing Delay

0.8

0.9

1.0

1.2

ns

FO=4 Routing Delay

1.0

1.2

1.4

1.6

ns

FO=8 Routing Delay

1.9

2.2

2.5

2.9

ns

FO=12 Routing Delay

2.8

3.2

3.7

4.3

ns

R-Cell Timing

t

RCO

t

CLR

t

PRESET

t

SUD

t

HD

t

WASYN

Sequential Clock-to-Q

0.9

1.1

1.3

1.4

ns

Asynchronous Clear-to-Q

0.5

0.6

0.7

0.8

ns

Asynchronous Preset-to-Q

0.7

0.8

0.9

1.0

ns

Flip-Flop Data Input Set-Up

0.5

0.5

0.7

0.8

ns

Flip-Flop Data Input Hold

0.0

0.0

0.0

0.0

ns

Asynchronous Pulse Width

1.4

1.6

1.8

2.1

ns

Input Module Propagation Delays

t

INYH

t

INYL

Predicted Input Routing Delays

2

Input Data Pad-to-Y HIGH

1.5

1.7

1.9

2.2

ns

Input Data Pad-to-Y LOW

1.5

1.7

1.9

2.2

ns

t

IRD1

t

IRD2

t

IRD3

t

IRD4

t

IRD8

t

IRD12

Notes:

1.

2.

FO=1 Routing Delay

0.3

0.4

0.4

0.5

ns

FO=2 Routing Delay

0.6

0.7

0.8

0.9

ns

FO=3 Routing Delay

0.8

0.9

1.0

1.2

ns

FO=4 Routing Delay

1.0

1.2

1.4

1.6

ns

FO=8 Routing Delay

1.9

2.2

2.5

2.9

ns

FO=12 Routing Delay

2.8

3.2

3.7

4.3

ns

For dual-module macros, use t

PD

+ t

RD1

+ t

PDn

, t

RCO

+ t

RD1

+ t

PDn

or t

PD1

+ t

RD1

+ t

SUD

, whichever is appropriate.

Routing delays are for typical designs across worst-case operating conditions. These parameters should be used for estimating device

performance. Post-route timing analysis or simulation is required to determine actual worst-case performance. Post-route timing is

based on actual routing delay measurements performed on the device prior to shipment.

相关PDF资料 |

PDF描述 |

|---|---|

| A54SX08P-PQ208M | 54SX Family FPGAs |

| A54SX08P-PQ208PP | LM1881 Video Sync Separator; Package: SOIC NARROW; No of Pins: 8 |

| A54SX08P-TQ208 | LM1881 Video Sync Separator; Package: MDIP; No of Pins: 8; Qty per Container: 40; Container: Rail |

| A54SX08P-TQ208I | LM1894 Dynamic Noise Reduction System DNR®; Package: SOIC NARROW; No of Pins: 14; Qty per Container: 55; Container: Rail |

| A54SX08P-TQ208M | 54SX Family FPGAs |

相关代理商/技术参数 |

参数描述 |

|---|---|

| A54SX08P-PQ208M | 制造商:未知厂家 制造商全称:未知厂家 功能描述:54SX Family FPGAs |

| A54SX08P-PQ208PP | 制造商:未知厂家 制造商全称:未知厂家 功能描述:54SX Family FPGAs |

| A54SX08-PQ208 | 功能描述:IC FPGA SX 12K GATES 208-PQFP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:SX 标准包装:40 系列:SX-A LAB/CLB数:6036 逻辑元件/单元数:- RAM 位总计:- 输入/输出数:360 门数:108000 电源电压:2.25 V ~ 5.25 V 安装类型:表面贴装 工作温度:0°C ~ 70°C 封装/外壳:484-BGA 供应商设备封装:484-FPBGA(27X27) |

| A54SX08-PQ208I | 功能描述:IC FPGA SX 12K GATES 208-PQFP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:SX 标准包装:40 系列:SX-A LAB/CLB数:6036 逻辑元件/单元数:- RAM 位总计:- 输入/输出数:360 门数:108000 电源电压:2.25 V ~ 5.25 V 安装类型:表面贴装 工作温度:0°C ~ 70°C 封装/外壳:484-BGA 供应商设备封装:484-FPBGA(27X27) |

| A54SX08-PQ208M | 制造商:未知厂家 制造商全称:未知厂家 功能描述:54SX Family FPGAs |

发布紧急采购,3分钟左右您将得到回复。