- 您现在的位置:买卖IC网 > PDF目录378266 > ACE1202 (Fairchild Semiconductor Corporation) Arithmetic Controller Engine (ACEx⑩) for Low Power Applications PDF资料下载

参数资料

| 型号: | ACE1202 |

| 厂商: | Fairchild Semiconductor Corporation |

| 英文描述: | Arithmetic Controller Engine (ACEx⑩) for Low Power Applications |

| 中文描述: | 算术控制器引擎(ACEx⑩)的低功耗应用 |

| 文件页数: | 13/39页 |

| 文件大小: | 2121K |

| 代理商: | ACE1202 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页当前第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页

13

www.fairchildsemi.com

ACE1202 Product Family Rev. B.1

A

4.1.1 Accumulator (A)

The Accumulator is a general-purpose 8-bit register that is used to

hold data and results of arithmetic calculations or data manipulations.

4.1.2 X-Pointer (X)

The X-Pointer register allows for a 12-bit indexing value to be added

to an 8-bit offset creating an effective address used for reading and

writing between the entire memory space. (Software can only read

from code EEPROM.) This provides software with the flexibility of

storing lookup tables in the code EEPROM memory space for the

core

’

s accessibility during normal operation.

The ACEx core allows software to access the entire 12-bit X-Pointer

register using the special X-pointer instructions (e.g. LD X, #000H). (See

Table 9) However, software may also access the register through any of

the memory-mapped instructions using the XHI (X[11:8]) and XLO

(X[7:0]) variables located at 0xBE and 0xBF, respectively. (See Table 11)

The X register is divided into two sections. The 11 least significant

bits (LSBs) of the register is the address of the program or data

memory space. The most significant bit (MSB) of the register is

write only and selects between the data (0x000 to 0x0FF) or

program (0x800 to 0xFFF) memory space.

Example: If Bit 11 = 0, then the LD A, [00,X] instruction will take a

value from address range 0x000 to 0x0FF and load it into A. If Bit

11 = 1, then the LD A, [00,X] instruction will take a value from

address range 0x800 to 0xFFF and load it into A.

The X register can also serve as a counter or temporary storage

register. However, this is true only for the 11-LSBs since the 12

th

bit is dedicated for memory space selection.

4.1.3 Program Counter (PC)

The 10-bit program counter register contains the address of the

next instruction to be executed. After a reset, if in normal mode the

program counter is initialized to 0x800.

4.1.4 Stack Pointer (SP)

The ACEx microcontroller has an automatic program stack with a 4-

bit stack pointer. The stack can be initialized to any location between

addresses 0x30-0x3F. Normally, the stack pointer is initialized by one

of the first instructions in an application program. After a reset, the

stack pointer is defaulted to 0xF pointing to address 0x3F.

The stack is configured as a data structure which decrements

from high to low memory. Each time a new address is pushed

onto the stack, the core decrements the stack pointer by two.

Each time an address is pulled from the stack, the core incre-

ments the stack pointer is by two. At any given time, the stack

pointer points to the next free location in the stack.

When a subroutine is called by a jump to subroutine (JSR)

instruction, the address of the instruction is automatically pushed

onto the stack least significant byte first. When the subroutine is

finished, a return from subroutine (RET) instruction is executed.

The RET instruction pulls the previously stacked return address

from the stack and loads it into the program counter. Execution

then continues at the recovered return address.

4.1.5 Status Register (SR)

The 8-bit Status register (SR) contains four condition code indicators

(C, H, Z, and N), one interrupt masking bit (G), and an EEPROM write

flag (R). The condition codes are automatically updated by most

instructions. (See Table 10)

Carry/Borrow (C)

The carry flag is set if the arithmetic logic unit (ALU) performs a carry

or borrow during an arithmetic operation and by its dedicated

instructions. The rotate instruction operates with and through the

carry bit to facilitate multiple-word shift operations. The LDC and

INVC instructions facilitate direct bit manipulation using the carry flag.

Half Carry (H)

The half carry flag ndicates whether an overflow has taken place on the

boundary between the two nibbles in the accumulator. It is primarily

used for Binary Coded Decimal (BCD) arithmetic calculation.

Zero (Z)

The zero flag is set if the result of an arithmetic, logic, or data

manipulation operation is zero. Otherwise, it is cleared.

Negative (N)

The negative flag is set if the MSB of the result from an arithmetic,

logic, or data manipulation operation is set to one. Otherwise, the

flag is cleared. A result is said to be negative if its MSB is a one.

Interrupt Mask (G)

The interrupt request mask (G) is a global mask that disables all

maskable interrupt sources. If the G Bit is cleared, interrupts can

become pending, but the operation of the core continues uninter-

rupted. However, if the G Bit is set an interrupt is recognized. After any

reset, the G bit is cleared by default and can only be set by a software

instruction. When an interrupt is recognized, the G bit is cleared after

the PC is stacked and the interrupt vector is fetched. Once the interrupt

is serviced, a return from interrupt instruction is normally executed to

restore the PC to the value that was present before the interrupt

occurred. The G bit is reset to one after a return from interrupt is

executed. Although the G bit can be set within an interrupt service

routine,

“

nesting

”

interrupts in this way should only be done when there

is a clear understanding of latency and of the arbitration mechanism.

4.2 Interrupt handling

When an interrupt is recognized, the current instruction completes its

execution. The return address (the current value in the program

counter) is pushed onto the stack and execution continues at the

address specified by the unique interrupt vector (see Table 11). This

process takes five instruction cycles. At the end of the interrupt service

routine, a return from interrupt (RETI) instruction is executed. The RETI

instruction causes the saved address to be pulled off the stack in

reverse order. The G bit is set and instruction execution resumes at the

return address.

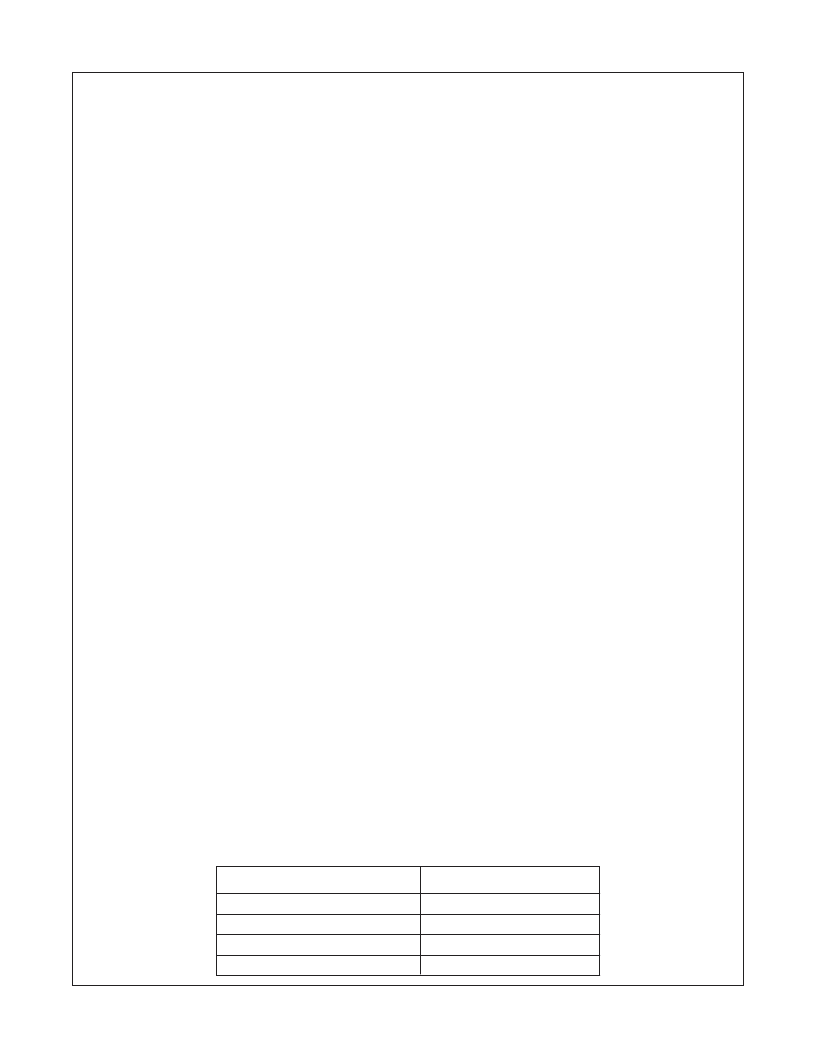

Table 8: Interrupt Priority Sequence

Priority (4 highest, 1 lowest)

Interrupt

4

MIW (EDGEI)

3

Timer0 (TMRI0)

2

Timer1 (TMRI1)

1

Software (INTR)

相关PDF资料 |

PDF描述 |

|---|---|

| ACE12022 | Arithmetic Controller Engine (ACEx⑩) for Low Power Applications |

| ACE12022B | Arithmetic Controller Engine (ACEx⑩) for Low Power Applications |

| ACE1202BEM8X | Arithmetic Controller Engine (ACEx⑩) for Low Power Applications |

| ACE12022EN14 | Arithmetic Controller Engine (ACEx⑩) for Low Power Applications |

| ACE12022BEN14 | Arithmetic Controller Engine (ACEx⑩) for Low Power Applications |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ACE12022 | 制造商:FAIRCHILD 制造商全称:Fairchild Semiconductor 功能描述:Arithmetic Controller Engine (ACEx⑩) for Low Power Applications |

| ACE12022B | 制造商:FAIRCHILD 制造商全称:Fairchild Semiconductor 功能描述:Arithmetic Controller Engine (ACEx⑩) for Low Power Applications |

| ACE12022BE | 制造商:FAIRCHILD 制造商全称:Fairchild Semiconductor 功能描述:Arithmetic Controller Engine (ACEx⑩) for Low Power Applications |

| ACE12022BEM | 制造商:FAIRCHILD 制造商全称:Fairchild Semiconductor 功能描述:Arithmetic Controller Engine (ACEx⑩) for Low Power Applications |

| ACE12022BEM8 | 制造商:FAIRCHILD 制造商全称:Fairchild Semiconductor 功能描述:Arithmetic Controller Engine (ACEx⑩) for Low Power Applications |

发布紧急采购,3分钟左右您将得到回复。