- 您现在的位置:买卖IC网 > PDF目录10938 > AD1838AASZ-REEL (Analog Devices Inc)IC CODEC 2ADC/6DAC 24 BIT 52MQFP PDF资料下载

参数资料

| 型号: | AD1838AASZ-REEL |

| 厂商: | Analog Devices Inc |

| 文件页数: | 15/24页 |

| 文件大小: | 0K |

| 描述: | IC CODEC 2ADC/6DAC 24 BIT 52MQFP |

| 标准包装: | 800 |

| 类型: | 立体声音频 |

| 数据接口: | 串行 |

| 分辨率(位): | 24 b |

| ADC / DAC 数量: | 2 / 6 |

| 三角积分调变: | 是 |

| S/N 比,标准 ADC / DAC (db): | 105 / 108 |

| 动态范围,标准 ADC / DAC (db): | 105 / 108 |

| 电压 - 电源,模拟: | 4.5 V ~ 5.5 V |

| 电压 - 电源,数字: | 4.5 V ~ 5.5 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 52-QFP |

| 供应商设备封装: | 52-MQFP(10x10) |

| 包装: | 带卷 (TR) |

REV. A

AD1838A

–22–

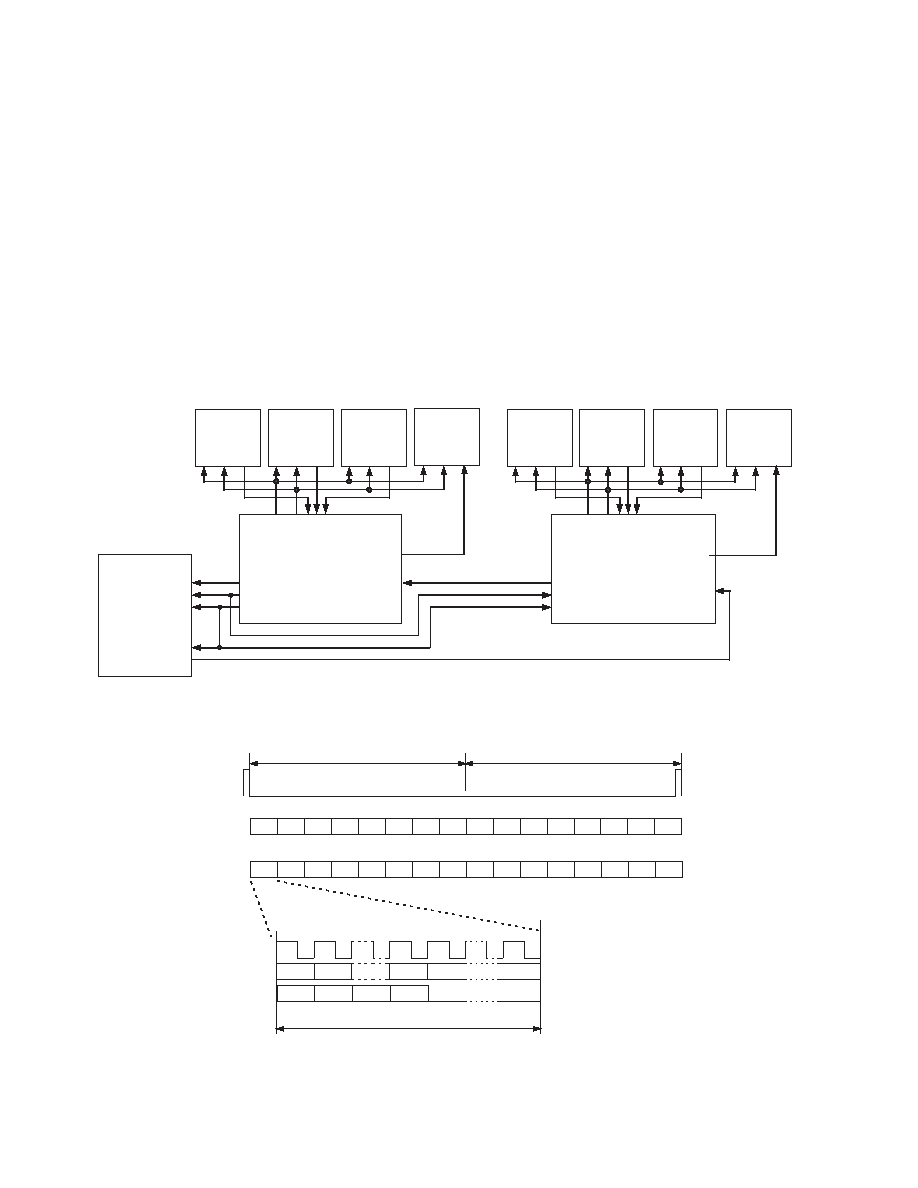

CASCADE MODE

Dual AD1838A Cascade

The AD1838A can be cascaded to an additional AD1838A,

which, in addition to six external stereo ADCs and one external

stereo DAC, can be used to create a 32-channel audio system

with 16 inputs and 16 outputs. The cascade is designed to

connect to a SHARC DSP and operates in a time division

multiplexing (TDM) format. Figure 14 shows the connection

diagram for cascade operation. The digital interface for both

parts must be set to operate in Auxiliary 512 mode by program-

ming ADC Control Register 2. AD1838A No. 1 is set as a master

device by connecting the

M/S pin to DGND and AD1838A

No. 2 is set as a slave device by connecting the

M/S to ODVDD.

Both devices should be run from the same MCLK and

PD/RST

signals to ensure that they are synchronized.

With Device 1 set as a master, it will generate the frame-sync

and bit clock signals. These signals are sent to the SHARC and

Device 2 ensuring that both know when to send and receive data.

The cascade can be thought of as two 256-bit shift registers, one

for each device. At the beginning of a sample interval, the shift

registers contain the ADC results from the previous sample

interval. The first shift register (Device 1) clocks data into the

SHARC and also clocks in data from the second shift register

(Device 2). While this is happening, the SHARC is sending

DAC data to the second shift register. By the end of the sample

interval, all 512 bits of ADC data in the shift registers will have

been clocked into the SHARC and been replaced by DAC data,

which is subsequently written to the DACs. Figure 15 shows the

timing diagram for the cascade operation.

AUX ADC

(SLAVE)

ALRCLK

ABCLK

ASDATA

DSDATA

ALRCLK

ABCLK

ASDATA

DSDATA

AD1838A NO. 1

(MASTER)

AD1838A NO. 2

(SLAVE)

SHARC

(SLAVE)

DOUT

LRCLK

BCLK

AUX ADC

(SLAVE)

DOUT

LRCLK

BCLK

AUX ADC

(SLAVE)

DOUT

LRCLK

BCLK

AUX ADC

(SLAVE)

DOUT

LRCLK

BCLK

AUX ADC

(SLAVE)

DOUT

LRCLK

BCLK

AUX ADC

(SLAVE)

DOUT

LRCLK

BCLK

AU

X

BCLK

AU

X

L

RCLK

AU

X

D

A

T

A

1

AU

X

D

A

T

A

2

AU

X

D

A

T

A

3

AU

X

BCLK

AU

X

L

RCLK

AU

X

D

A

T

A

1

AU

X

D

A

T

A

2

AU

X

D

A

T

A

3

DRx

RFSx

RCLKx

TCLKx

DTx

AUX DAC

(SLAVE)

DIN

LRCLK

BCLK

DAUXDATA

AUX DAC

(SLAVE)

DIN

LRCLK

BCLK

DAUXDATA

Figure 14. Dual AD1838A Cascade

AD1838A NO. 1 DACs

L1

L2

L3

R1

R2

R3

AD1838A NO. 2 DACs

L1

L2

L3

R1

R2

R3

RFSx

DTx

AD1838A NO. 1 ADCs

L1

L2

L3

L4

R1

R2

R3

R4

AD1838A NO. 2 ADCs

L1

L2

L3

L4

R1

R2

R3

R4

DRx

256 BCLKs

MSB

MSB – 1

LSB

32 ABCLKs

BCLK

DTx

MSB

MSB – 1

LSB

DRx

DON’ T CARE

L4

R4

L4

R4

Figure 15. Dual AD1838A Cascade Timing

相关PDF资料 |

PDF描述 |

|---|---|

| AD1835AASZ-REEL | IC CODEC 2ADC/8DAC 24BIT 52MQFP |

| ADAV803ASTZ-REEL | IC CODEC AUDIO R-DVD 3.3V 64LQFP |

| AD1939YSTZRL | IC CODEC 24BIT ADC/DAC 64-LQFP |

| AD1937WBSTZ-RL | IC CODEC 4/ADC DIFF OUT 64-LQFP |

| AD1938WBSTZ-RL | IC CODEC 24BIT 4ADC/8DAC 48LQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD1838AS | 制造商:Analog Devices 功能描述:Audio Codec 2ADC / 6DAC 24-Bit 52-Pin MQFP 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| AD1838AS-REEL | 制造商:Analog Devices 功能描述:Audio Codec 2ADC / 6DAC 24-Bit 52-Pin MQFP T/R 制造商:Rochester Electronics LLC 功能描述:- Tape and Reel |

| AD1839 | 制造商:AD 制造商全称:Analog Devices 功能描述:2 ADC, 6 DAC, 96 kHz, 24-Bit sigma-delta Codec |

| AD1839A | 制造商:AD 制造商全称:Analog Devices 功能描述:2 ADC, 6 DAC, 96 kHz, 24-Bit Sigma-Delta Codec |

| AD1839AAS | 制造商:Analog Devices 功能描述:Audio Codec 2ADC / 6DAC 24-Bit 52-Pin MQFP 制造商:Rochester Electronics LLC 功能描述:HIGH PERFORMANCE CODEC I.C. - Bulk 制造商:Analog Devices 功能描述:IC CODEC SMD 1839 MQFP52 |

发布紧急采购,3分钟左右您将得到回复。