参数资料

| 型号: | AD1955ARSZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 5/24页 |

| 文件大小: | 0K |

| 描述: | IC DAC AUDIO MULTIBIT 28-SSOP |

| 产品培训模块: | Data Converter Fundamentals DAC Architectures |

| 标准包装: | 47 |

| 位数: | 16,24 |

| 数据接口: | 串行 |

| 转换器数目: | 2 |

| 电压电源: | 模拟和数字 |

| 功率耗散(最大): | 210mW |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 28-SSOP(0.209",5.30mm 宽) |

| 供应商设备封装: | 28-SSOP |

| 包装: | 管件 |

| 输出数目和类型: | 4 电流,单极 |

| 采样率(每秒): | 192k |

| 产品目录页面: | 781 (CN2011-ZH PDF) |

| 配用: | EVAL-AD1955EBZ-ND - BOARD EVAL FOR AD1955 |

REV. 0

AD1955

–13–

Serial Data Format in External Digital Filter Mode

In the External Digital Filter Mode, the AD1955 will accept

up to 24-bit serial, twos complement, MSB-first data from an

external digital filter, an HDCD decoder, or a general-purpose

DSP. If the External Digital Filter Mode is selected by Control

Register 0, Bits 12 and 13, Pin 2 to Pin 5 are assigned as the word

clock input (EF_WCLK, Pin 2), bit clock input (EF_BCLK,

Pin 3), left channel data input (EF_LDATA, Pin 4), and right

channel data input (EF_RDATA, Pin 5), respectively, to accept

8fS (48 kHz), 4fS (96 kHz), or 2fS (196 kHz) oversampled data.

Left and right channel data should be valid on the rising edge

of EF_BCLK. The mode can be set to Left- or Right-Justified.

A burst mode BCLK can be used in Left-Justified Mode.

Serial Data Format in SACD Mode

In the SACD Mode, the AD1955 supports both normal mode

or phase modulation mode, which are selected by Control

Register 1, Bit 6. If normal mode is selected, DSD_SCLK,

DSD_LDATA, and DSD_RDATA are used to interface with

DSD decoder chip. In this mode, the DSD data is clocked in

the AD1955 using the rising edge of DSD_SCLK with a 64fS

rate, 2.8224 MHz. DSD_PHASE pin should be connected LOW.

If Phase Modulation Mode is selected, the DSD_PHASE pin is

also used to interface with the DSD decoder. In this mode, a

64fS DSD_PHASE signal is used as a reference signal to receive

the data from the decoder. The DSD data is clocked into the

AD1955 with a 128fS DSD_SCLK.

The AD1955 can operate as a master or slave device. In Master

Mode, the AD1955 will output DSD_SCLK and DSD_PHASE

(if in Phase Modulation Mode) to a DSD decoder and will

support Normal Mode and Phase Modulation Mode 0. In Slave

Mode, the AD1955 will accept DSD_SCLK and DSD_PHASE

(if in Phase Modulation Mode) from a DSD decoder and sup-

ports all of the normal and phase modulation modes.

When the SACD Port is not being used, the SACD pins (Pins

6, 7, 8, and 9) should be tied to a valid logic level. Please note

that there are weak pull-ups (0.6 mA typical) on DSD_SCLK

and DSD_PHASE.

Master Clock

The AD1955 must be set to the proper sample rate and master

clock rate using Control Registers 0 and 1. The allowable master

clock frequencies for each interpolation mode are shown below.

In the External Filter Mode, the AD1955 accepts master clock

frequencies depending on the input sample rate as shown below.

In the SACD Mode, the AD1955 accepts a 256fS, 512fS, or

768fS Master Clock, where fS is nominally 44.1 kHz. In Slave

Mode, by default, the rising edge of DSD_SCLK should coincide

with the rising edge of MCLK. Control Register 1, Bit 2 should

be set to 1 if the rising edge of DSD_SCLK coincides with the

falling edge of MCLK. In Master Mode this bit can be used to

select the MCLK edge used to generate the DSD clock outputs.

Zero Detection

When the AD1955 detects that the audio input data is continu-

ously zero during 1024 LRCLK periods in PCM Mode or 8192

LRCLK periods in 8fS External Digital Filter Mode, ZEROL

(Pin 21) or ZEROR (Pin 20) is set to active.

When the AD1955 is in SACD Mode, it will detect an SACD

mute pattern. If the input bit stream shows a mute pattern for

about 22 ms, the AD1955 will set ZEROL (Pin 21) or ZEROR

(Pin 20) to active. The outputs can be set to active high or low

using Control Register 1, Bit 8.

Reset/Power-Down

The AD1955 will be reset when the

PD/RST pin is set low. The

part may be powered down using Bit 15, Control Register 0.

Audio Outputs

Active I/V converters should be used, which will hold the DAC

outputs at a constant voltage level. Passive I/V conversion should

not be used, since the DAC performance will be seriously degraded.

For best THD + N performance over temperature, a reference

voltage of 2.80 V should be used with the I/V converters. For a

lower parts count, the voltage at FILTR can be used. In this

instance, THD + N performance at high temperature can be

improved by reducing IREF, with an attendant reduction in gain

(linear dependence) and DNR/SNR (square-root dependence).

The AD1955 audio outputs sink a current proportional to the

input signal, superimposed on a steady bias current. The cur-

rent-to-voltage (I/V) converters used need to be able to supply

this bias current, as well as the signal current, or a resistor or

current source can be used to a positive voltage to null this

current in order to center the range of the I/V converters.

If pull-up resistors are used to bring the output of the I/V convert-

ers to 0 V for maximum headroom and THD balance, as shown

in the applications circuits, the following equation can be used:

RV

V

I

V

R

PULLUP

SUPPLY

BIAS

I V

=

[]

+

[]

–

()

/

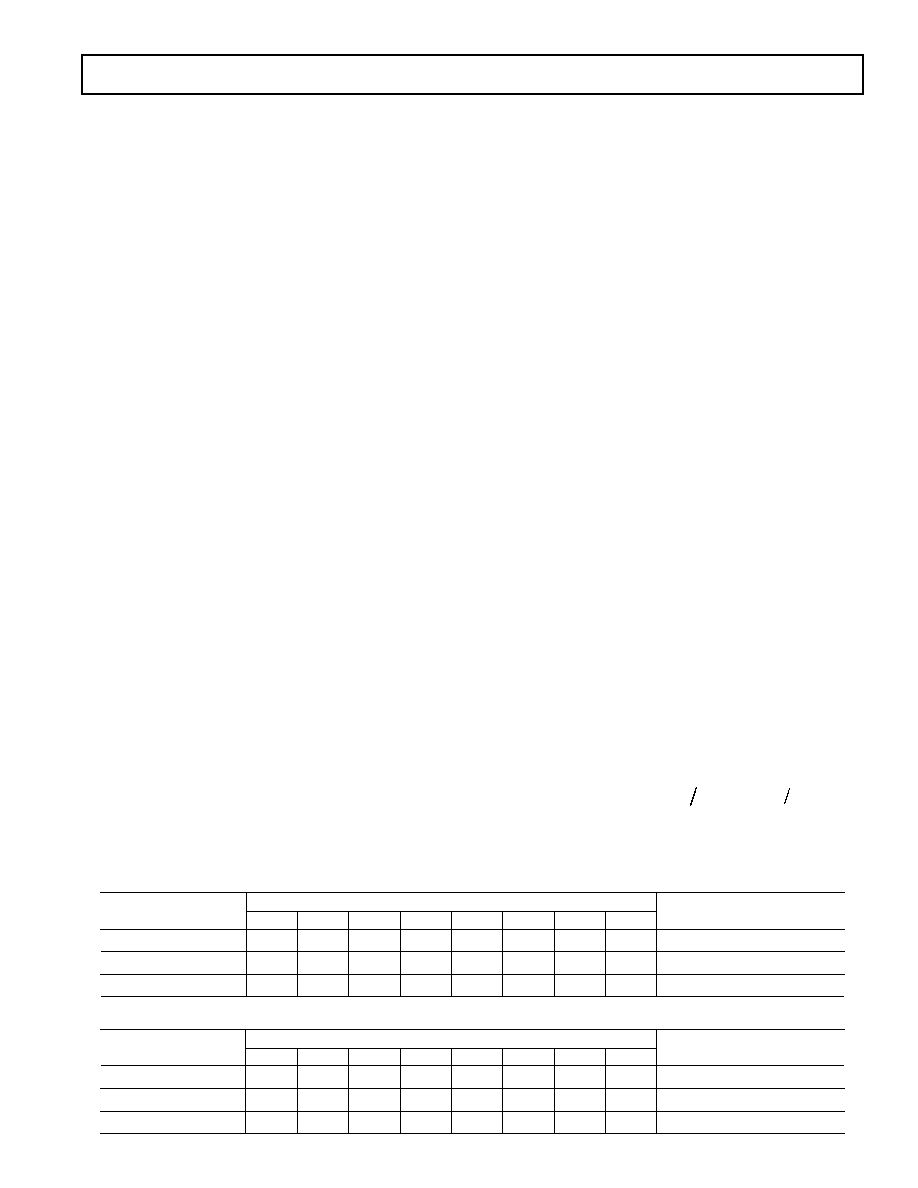

PCM Mode

Allowable Master Clock Frequencies (

fS)Nominal Input

Interpolation Mode

64

96

128

192

256

384

512

768

Sample Rate (kHz)

48 kHz (INT

8×) Mode

32, 44.1, 48

96 kHz (INT

4×) Mode

88.2, 96

192 kHz (INT

2×) Mode

176.4, 192

External Filter Mode

Allowable Master Clock Frequencies (

fS)Nominal Input Sample Rate

Input Sample Rate

64

96

128

192

256

384

512

768

(to External Filter) (kHz)

8

× fS

32, 44.1, 48

4

× fS

88.2, 96

2

× f

S

176.4, 192

相关PDF资料 |

PDF描述 |

|---|---|

| ICS870919BRI-01LFT | IC CLK GENERATOR LVCMOS 28QSOP |

| LTC1446IN8#PBF | IC D/A CONV 12BIT R-R DUAL 8-DIP |

| VI-B4D-MY-F3 | CONVERTER MOD DC/DC 85V 50W |

| LTC1446LCS8#PBF | IC D/A CONV 12BIT R-R DUAL 8SOIC |

| VE-B4W-MV-F4 | CONVERTER MOD DC/DC 5.5V 150W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD1955ARSZRL | 功能描述:IC DAC AUDIO 16-24BIT 28SSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:- 标准包装:47 系列:- 设置时间:2µs 位数:14 数据接口:并联 转换器数目:1 电压电源:单电源 功率耗散(最大):55µW 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:管件 输出数目和类型:1 电流,单极;1 电流,双极 采样率(每秒):* |

| AD1955YRS | 制造商:AD 制造商全称:Analog Devices 功能描述:High Performance Multibit DAC with SACD Playback |

| AD1955YRSRL | 制造商:AD 制造商全称:Analog Devices 功能描述:High Performance Multibit DAC with SACD Playback |

| AD1958 | 制造商:AD 制造商全称:Analog Devices 功能描述:PLL/Multibit DAC |

| AD1958YRS | 制造商:Rochester Electronics LLC 功能描述:HIGH PERFORMANCE PLL/MULTIBIT DAC - Bulk 制造商:Analog Devices 功能描述: |

发布紧急采购,3分钟左右您将得到回复。