- 您现在的位置:买卖IC网 > PDF目录8683 > AD5322BRMZ-REEL7 (Analog Devices Inc)IC DAC 12BIT DUAL 10MSOP T/R PDF资料下载

参数资料

| 型号: | AD5322BRMZ-REEL7 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 23/24页 |

| 文件大小: | 0K |

| 描述: | IC DAC 12BIT DUAL 10MSOP T/R |

| 产品培训模块: | Data Converter Fundamentals DAC Architectures |

| 标准包装: | 1,000 |

| 设置时间: | 6µs |

| 位数: | 12 |

| 数据接口: | 串行 |

| 转换器数目: | 2 |

| 电压电源: | 单电源 |

| 功率耗散(最大): | 2.5mW |

| 工作温度: | -40°C ~ 105°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 10-TFSOP,10-MSOP(0.118",3.00mm 宽) |

| 供应商设备封装: | 10-MSOP |

| 包装: | 带卷 (TR) |

| 输出数目和类型: | 2 电压,单极;2 电压,双极 |

| 采样率(每秒): | 125k |

AD5302/AD5312/AD5322

Rev. D | Page 8 of 24

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

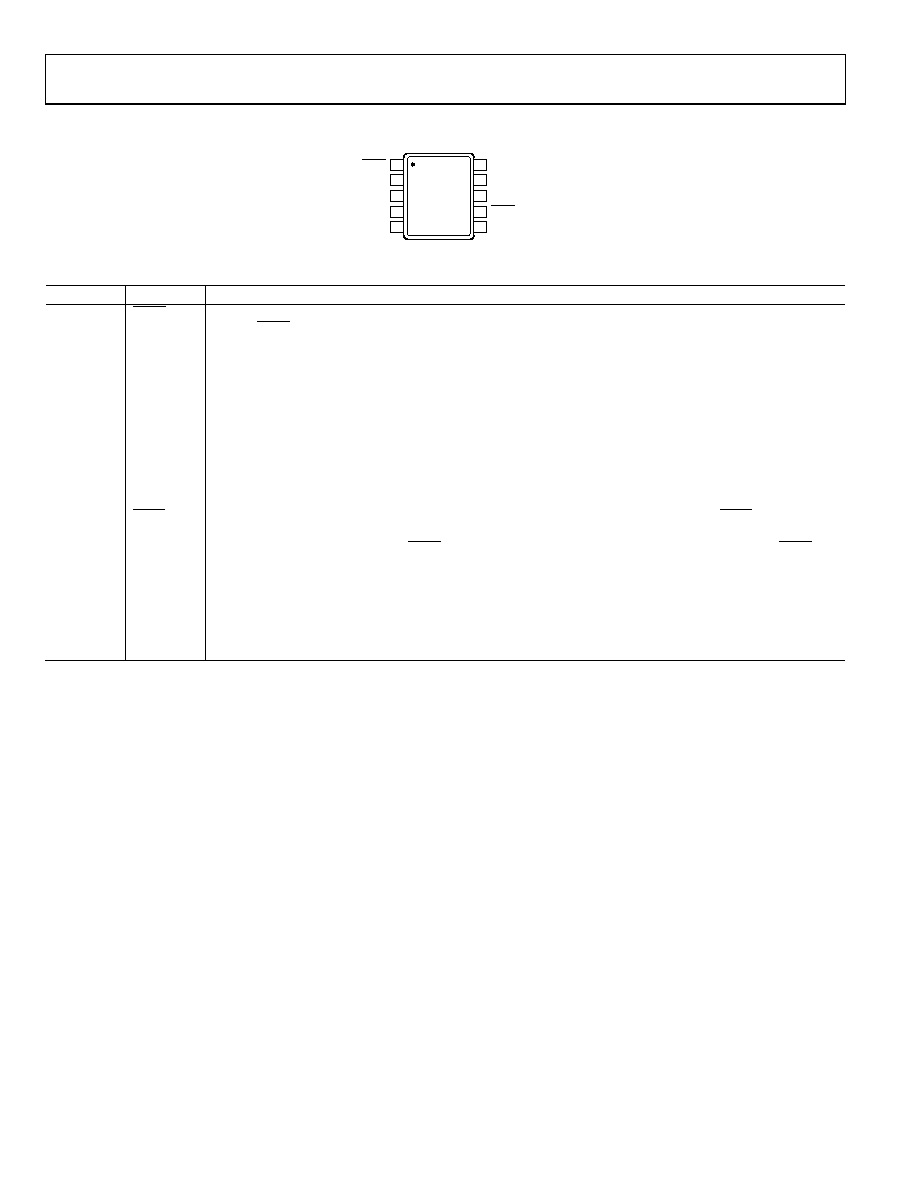

LDAC 1

VDD 2

VREFB 3

VREFA 4

VOUTA 5

GND

10

DIN

9

SCLK

8

SYNC

7

VOUTB

6

AD5302/

AD5312/

AD5322

TOP VIEW

(Not to Scale)

00

92

8-

00

3

Figure 5. Pin Configuration

Table 5. Pin Function Descriptions

Pin No.

Mnemonic

Description

1

LDAC

Active Low Control Input. This pin transfers the contents of the input registers to their respective DAC registers.

Pulsing LDAC low allows either or both DAC registers to be updated if the input registers have new data. This

allows simultaneous updating of both DAC outputs.

2

VDD

Power Supply Input. The parts can be operated from 2.5 V to 5.5 V, and the supply should be decoupled to GND.

3

VREFB

Reference Input Pin for DAC B. This is the reference for DAC B. It can be configured as a buffered or an

unbuffered input, depending on the BUF bit in the control word of DAC B. It has an input range of 0 V to VDD in

unbuffered mode and 1 V to VDD in buffered mode.

4

VREFA

Reference Input Pin for DAC A. This is the reference for DAC A. It can be configured as a buffered or an

unbuffered input depending on the BUF bit in the control word of DAC A. It has an input range of 0 V to VDD in

unbuffered mode and 1 V to VDD in buffered mode.

5

VOUTA

Buffered Analog Output Voltage from DAC A. The output amplifier has rail-to-rail operation.

6

VOUTB

Buffered Analog Output Voltage from DAC B. The output amplifier has rail-to-rail operation.

7

SYNC

Active Low Control Input. This is the frame synchronization signal for the input data. When SYNC goes low, it

powers on the SCLK and DIN buffers and enables the input shift register. Data is transferred in on the falling

edges of the following 16 clocks. If SYNC is taken high before the 16th falling edge, the rising edge of SYNC acts

as an interrupt and the write sequence is ignored by the device.

8

SCLK

Serial Clock Input. Data is clocked into the input shift register on the falling edge of the serial clock input. Data

can be transferred at rates up to 30 MHz. The SCLK input buffer is powered down after each write cycle.

9

DIN

Serial Data Input. This device has a 16-bit input shift register. Data is clocked into the register on the falling

edge of the serial clock input. The DIN input buffer is powered down after each write cycle.

10

GND

Ground Reference Point for All Circuitry on the Part.

相关PDF资料 |

PDF描述 |

|---|---|

| V375A24H400BL2 | CONVERTER MOD DC/DC 24V 400W |

| NB3N106KMNR2G | IC FANOUT BUFFER 1:6 HCSL 24QFN |

| NB3N121KMNR2G | IC FANOUT BUFFER 1:21 52QFN |

| AD9740ACPZRL7 | IC DAC 10BIT 210MSPS 32-LFCSP |

| NB7VQ58MMNTXG | IC CLOCK/DATA MUX 2:1 7GHZ 16QFN |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD5323 | 制造商:AD 制造商全称:Analog Devices 功能描述:2.5 V to 5.5 V, 500 uA, Parallel Interface Quad Voltage-Output 8-/10-/12-Bit DACs |

| AD5323ARU | 制造商:Analog Devices 功能描述:DAC 2-CH Resistor-String 12-bit 16-Pin TSSOP 制造商:Rochester Electronics LLC 功能描述:DUAL 12-BIT VOLTAGE OUT DAC I.C. - Bulk |

| AD5323ARU-REEL7 | 制造商:Analog Devices 功能描述:DAC 2-CH Resistor-String 12-bit 16-Pin TSSOP T/R 制造商:Analog Devices 功能描述:DAC 2CH RES-STRING 12-BIT 16TSSOP - Tape and Reel 制造商:Rochester Electronics LLC 功能描述:DUAL 12-BIT VOLTAGE OUT DAC I.C. - Tape and Reel |

| AD5323ARUZ | 功能描述:IC DAC 12BIT DUAL R-R 16-TSSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:- 标准包装:47 系列:- 设置时间:2µs 位数:14 数据接口:并联 转换器数目:1 电压电源:单电源 功率耗散(最大):55µW 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:管件 输出数目和类型:1 电流,单极;1 电流,双极 采样率(每秒):* |

发布紧急采购,3分钟左右您将得到回复。