- 您现在的位置:买卖IC网 > PDF目录8751 > AD5424YRUZ-REEL (Analog Devices Inc)IC DAC 8BIT MULTIPLYING 16-TSSOP PDF资料下载

参数资料

| 型号: | AD5424YRUZ-REEL |

| 厂商: | Analog Devices Inc |

| 文件页数: | 17/29页 |

| 文件大小: | 0K |

| 描述: | IC DAC 8BIT MULTIPLYING 16-TSSOP |

| 产品培训模块: | Data Converter Fundamentals DAC Architectures |

| 标准包装: | 2,500 |

| 设置时间: | 30ns |

| 位数: | 8 |

| 数据接口: | 并联 |

| 转换器数目: | 1 |

| 电压电源: | 单电源 |

| 功率耗散(最大): | 25µW |

| 工作温度: | -40°C ~ 125°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 16-TSSOP(0.173",4.40mm 宽) |

| 供应商设备封装: | 16-TSSOP |

| 包装: | 带卷 (TR) |

| 输出数目和类型: | 2 电流,单极;2 电流,双极 |

| 采样率(每秒): | 20.4M |

| 配用: | EVAL-AD5424EBZ-ND - BOARD EVALUATION FOR AD5424 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页当前第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页

Data Sheet

AD5424/AD5433/AD5445

Rev. D | Page 23 of 28

Provided the DAC switches are driven from true wideband

low impedance sources (VIN and AGND), they settle quickly.

Consequently, the slew rate and settling time of a voltage

switching DAC circuit is determined largely by the output op

amp. To obtain minimum settling time in this configuration, it

is important to minimize capacitance at the VREF node (voltage

output node in this application) of the DAC. This is done by using

low inputs capacitance buffer amplifiers and careful board design.

Most single-supply circuits include ground as part of the analog

signal range, which in turns requires an amplifier that can handle

rail-to-rail signals. There is a large range of single-supply

amplifiers available from Analog Devices.

PARALLEL INTERFACE

of an 8-, 10-, or 12-bit parallel word. Control lines CS and R/W

allow data to be written to or read from the DAC register. A

write event takes place when CS and R/W are brought low, data

available on the data lines fills the shift register, and the rising

edge of CS latches the data and transfers the latched data-word

to the DAC register. The DAC latches are not transparent, thus

a write sequence must consist of a falling and rising edge on CS

to ensure that data is loaded to the DAC register and its analog

equivalent is reflected on the DAC output.

A read event takes place when R/W is held high and CS is

brought low. New data is loaded from the DAC register back to

the input register and out onto the data line where it can be read

back to the controller for verification or diagnostic purposes.

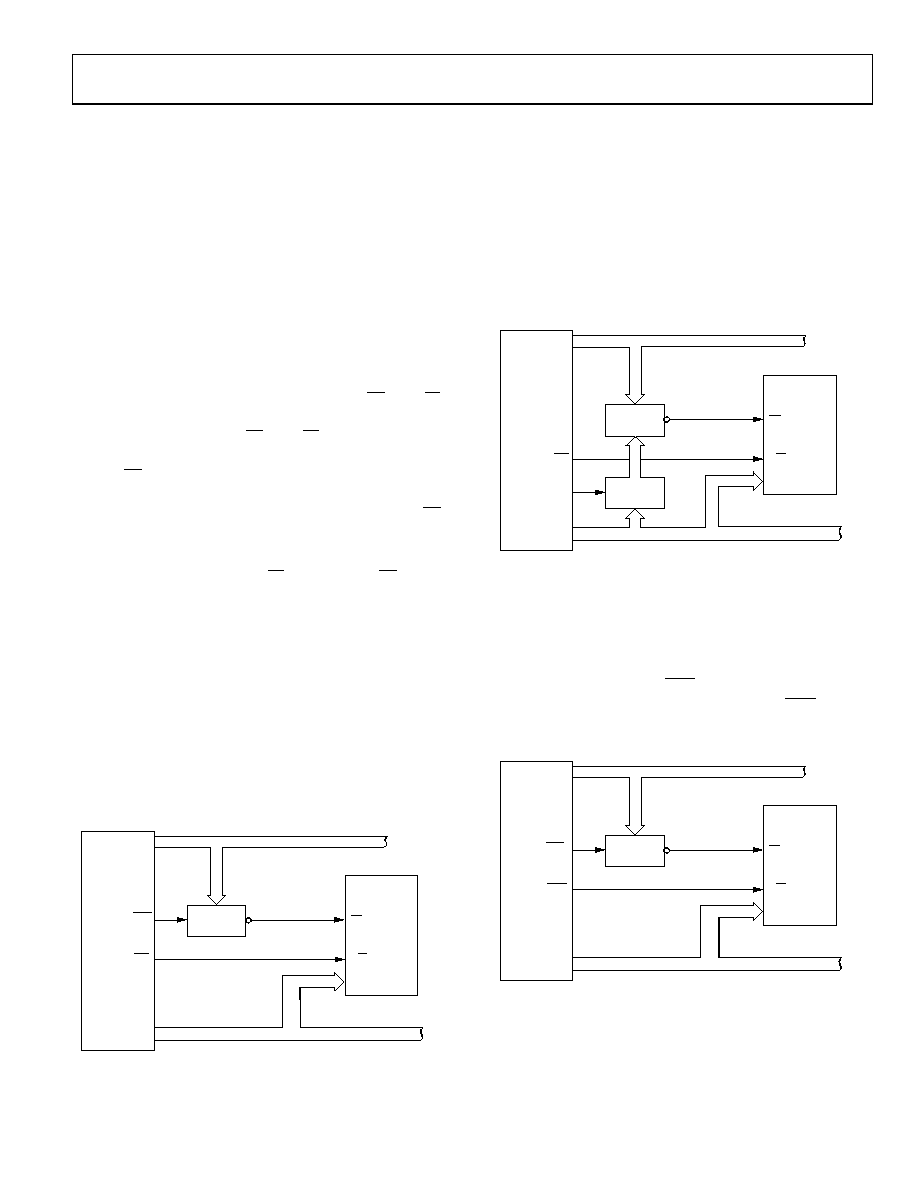

MICROPROCESSOR INTERFACING

the ADSP-21xx series of DSPs as a memory-mapped device. A

single wait state may be necessary to interface the AD5424/

speed of the DSP. The wait state can be programmed via the

data memory wait state control register of the ADSP-21xx

(see the ADSP-21xx family user’s manual for details).

03160-056

R/W

DB0 TO DB11

AD5424/

AD5433/

AD5445*

ADDRESS

DECODER

CS

DATA 0 TO

DATA 23

ADDRESS BUS

ADDR0 TO

ADRR13

ADSP-21xx*

DATA BUS

DMS

WR

*ADDITIONAL PINS OMITTED FOR CLARITY

AD5445 and the 8xC51 family of DSPs. To facilitate external

data memory access, the address latch enable (ALE) mode is

enabled. The low byte of the address is latched with this output

pulse during access to external memory. AD0 to AD7 are the

multiplexed low order addresses and data bus and require

strong internal pull-ups when emitting 1s. During access to

external memory, A8 to A15 are the high order address bytes.

Since these ports are open drained, they also require strong

internal pull-ups when emitting 1s.

03160-063

R/W

DB0 TO DB11

AD5424/

AD5433/

AD5445*

ADDRESS

DECODER

CS

AD0 TO AD7

ADDRESS BUS

A8 TO A15

8051*

DATA BUS

WR

*ADDITIONAL PINS OMITTED FOR CLARITY

8-BIT

LATCH

ALE

asynchronous memory write cycle of the processor drives the

digital inputs of the DAC. The AMSx line is actually four memory

select lines. Internal ADDR lines are decoded into AMS3-0, these

lines are then inserted as chip selects. The rest of the interface is

a standard handshaking operation.

03160-057

R/W

DB0 TO DB11

AD5424/

AD5433/

AD5445*

ADDRESS

DECODER

CS

DATA 0 TO

DATA 23

ADDRESS BUS

ADDR1 TO

ADRR19

ADSP-BF5xx

DATA BUS

AMSx

AWE

*ADDITIONAL PINS OMITTED FOR CLARITY

相关PDF资料 |

PDF描述 |

|---|---|

| ICS8535AGI-01LF | IC CLOCK BUFFER MUX 2:4 20-TSSOP |

| VE-25W-MW-F3 | CONVERTER MOD DC/DC 5.5V 100W |

| VE-JNH-MZ-F1 | CONVERTER MOD DC/DC 52V 25W |

| VE-25W-MW-F2 | CONVERTER MOD DC/DC 5.5V 100W |

| VE-25W-MW-F1 | CONVERTER MOD DC/DC 5.5V 100W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD5424YRUZ-REEL7 | 功能描述:IC DAC 8BIT MULTIPLYING 16-TSSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:- 产品培训模块:Data Converter Fundamentals DAC Architectures 设计资源:Unipolar, Precision DC Digital-to-Analog Conversion using AD5450/1/2/3 8-14-Bit DACs (CN0052) Precision, Bipolar, Configuration for AD5450/1/2/3 8-14bit Multiplying DACs (CN0053) AC Signal Processing Using AD5450/1/2/3 Current Output DACs (CN0054) Programmable Gain Element Using AD5450/1/2/3 Current Output DAC Family (CN0055) Single Supply Low Noise LED Current Source Driver Using a Current Output DAC in the Reverse Mode (CN0139) 标准包装:10,000 系列:- 设置时间:- 位数:12 数据接口:DSP,MICROWIRE?,QSPI?,串行,SPI? 转换器数目:1 电压电源:单电源 功率耗散(最大):- 工作温度:-40°C ~ 125°C 安装类型:表面贴装 封装/外壳:SOT-23-8 薄型,TSOT-23-8 供应商设备封装:TSOT-23-8 包装:带卷 (TR) 输出数目和类型:1 电流,单极;1 电流,双极 采样率(每秒):2.7M |

| AD5425 | 制造商:AD 制造商全称:Analog Devices 功能描述:8-Bit, High Bandwidth Multiplying DAC with Serial Interface |

| AD5425BRM | 制造商:Analog Devices 功能描述:DAC 1CH R-2R 8BIT 10PIN USOIC - Bulk |

| AD5425YRM | 功能描述:IC DAC MULTIPLYING 8BIT 10-MSOP RoHS:否 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:- 产品培训模块:LTC263x 12-, 10-, and 8-Bit VOUT DAC Family 特色产品:LTC2636 - Octal 12-/10-/8-Bit SPI VOUT DACs with 10ppm/°C Reference 标准包装:91 系列:- 设置时间:4µs 位数:10 数据接口:MICROWIRE?,串行,SPI? 转换器数目:8 电压电源:单电源 功率耗散(最大):2.7mW 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:14-WFDFN 裸露焊盘 供应商设备封装:14-DFN-EP(4x3) 包装:管件 输出数目和类型:8 电压,单极 采样率(每秒):* |

| AD5425YRM-REEL | 功能描述:IC DAC 8BIT MULTIPLYING 10-MSOP RoHS:否 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:- 产品培训模块:Data Converter Fundamentals DAC Architectures 设计资源:Unipolar, Precision DC Digital-to-Analog Conversion using AD5450/1/2/3 8-14-Bit DACs (CN0052) Precision, Bipolar, Configuration for AD5450/1/2/3 8-14bit Multiplying DACs (CN0053) AC Signal Processing Using AD5450/1/2/3 Current Output DACs (CN0054) Programmable Gain Element Using AD5450/1/2/3 Current Output DAC Family (CN0055) Single Supply Low Noise LED Current Source Driver Using a Current Output DAC in the Reverse Mode (CN0139) 标准包装:10,000 系列:- 设置时间:- 位数:12 数据接口:DSP,MICROWIRE?,QSPI?,串行,SPI? 转换器数目:1 电压电源:单电源 功率耗散(最大):- 工作温度:-40°C ~ 125°C 安装类型:表面贴装 封装/外壳:SOT-23-8 薄型,TSOT-23-8 供应商设备封装:TSOT-23-8 包装:带卷 (TR) 输出数目和类型:1 电流,单极;1 电流,双极 采样率(每秒):2.7M |

发布紧急采购,3分钟左右您将得到回复。