参数资料

| 型号: | AD5764RCSUZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 19/32页 |

| 文件大小: | 0K |

| 描述: | IC DAC QUAD 16BIT VOUT 32-TQFP |

| 产品培训模块: | Data Converter Fundamentals DAC Architectures |

| 产品变化通告: | AD5764(R), AD5744R Product Change 04/Sept/2009 |

| 设计资源: | High Accuracy, Bipolar Voltage Output Digital-to-Analog Conversion Using AD5764 (CN0006) |

| 标准包装: | 1 |

| 设置时间: | 8µs |

| 位数: | 16 |

| 数据接口: | DSP,MICROWIRE?,QSPI?,串行,SPI? |

| 转换器数目: | 4 |

| 电压电源: | 双 ± |

| 功率耗散(最大): | 275 mW |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 32-TQFP |

| 供应商设备封装: | 32-TQFP(7x7) |

| 包装: | 托盘 |

| 输出数目和类型: | 4 电压,双极 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页当前第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页

AD5764R

Data Sheet

Rev. D | Page 26 of 32

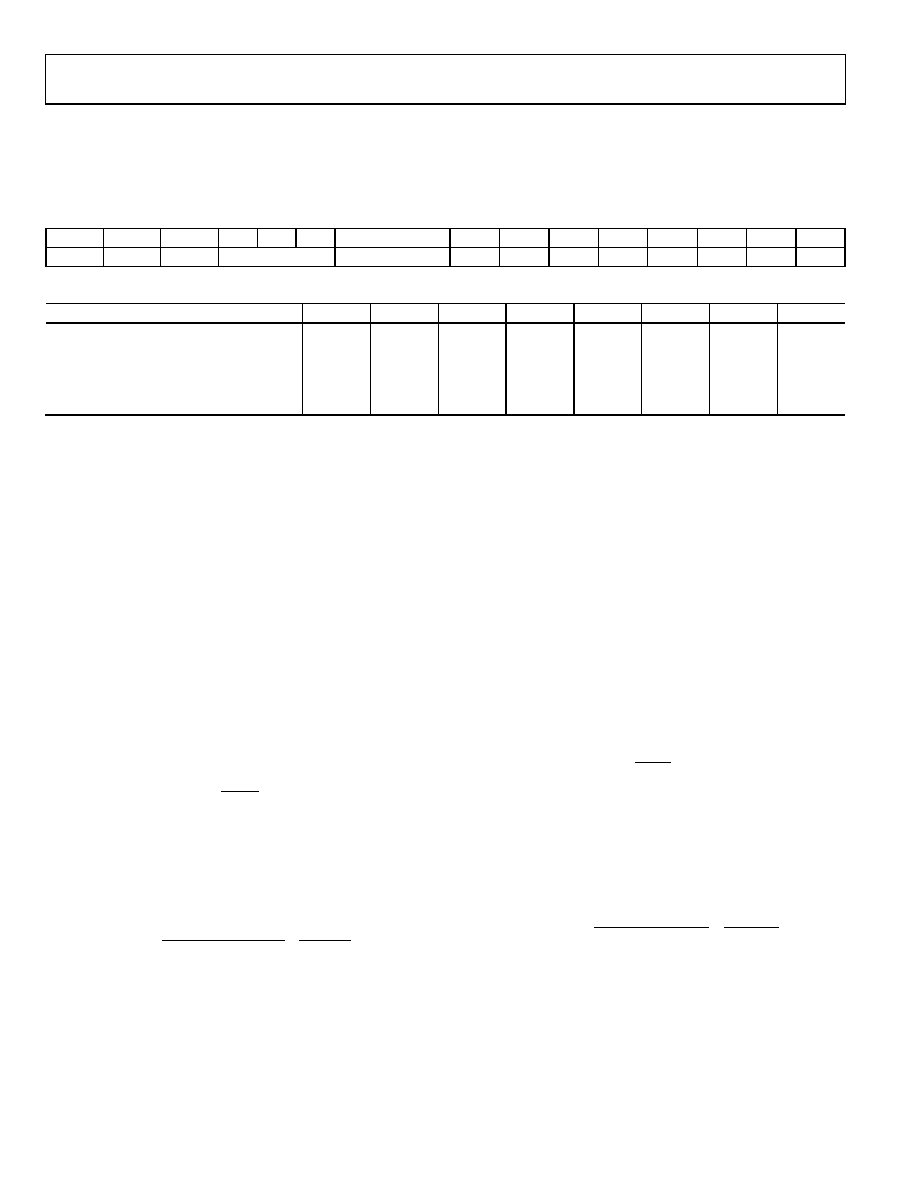

OFFSET REGISTER

The offset register is addressed by setting the three REG bits to 101. The DAC address bits select the DAC channel with which the data

transfer takes place (see Table 10). The AD5764R offset register is an 8-bit register that allows the user to adjust the offset of each channel

by 16 LSBs to +15.875 LSBs in steps of one-eighth LSB, as shown in Table 18 and Table 19. The offset register coding is twos complement.

Table 18. Programming the Offset Register

REG2

REG1

REG0

A2

A1

A0

DB15 to DB8

DB7

DB6

DB5

DB4

DB3

DB2

DB1

DB0

1

0

1

DAC address

Don’t care

OF7

OF6

OF5

OF4

OF3

OF2

OF1

OF0

Table 19. Offset Register Options

Offset Adjustment

OF7

OF6

OF5

OF4

OF3

OF2

OF1

OF0

+15.875 LSBs

0

1

+15.75 LSBs

0

1

0

No Adjustment (Default)

0

15.875 LSBs

1

0

1

16 LSBs

1

0

OFFSET AND GAIN ADJUSTMENT WORKED

EXAMPLE

Using the information provided in the Offset Register section,

the following worked examples demonstrate how the AD5764R

functions can be used to eliminate both offset and gain errors.

Because the AD5764R is factory calibrated, offset and gain errors

should be negligible. However, errors can be introduced by the

system within which the AD5764R is operating. For example,

a voltage reference value that is not equal to 5 V introduces

a gain error. An output range of ±10 V and twos complement

data coding are assumed.

Removing Offset Error

The AD5764R can eliminate an offset error in the range of

4.88 mV to +4.84 mV with a step size of one-eighth of a

16-bit LSB.

1.

Calculate the step size of the offset adjustment, using the

following equation:

Offset Adjust Step Size =

8

2

20

16 ×

= 38.14 V

2.

Measure the offset error by programming 0x0000 to the

data register and measuring the resulting output voltage.

For this example, the measured value is 614 V.

3.

Determine how many offset adjustment steps this value

represents, using the following equation:

Number of Steps =

V

14

.

38

V

614

=

Size

Step

Offset

Value

Offset

Measured

= 16 Steps

The offset error measured is positive; therefore, a negative

adjustment of 16 steps is required. The offset register is

eight bits wide, and the coding is twos complement.

The required offset register value can be calculated as follows:

1.

Convert the adjustment value to binary: 00010000.

2.

Convert this binary value to a negative twos complement

number by inverting all bits and adding 1: 11110000.

3.

Program this value, 11110000, to the offset register.

Note that this twos complement conversion is not necessary in

the case of a positive offset adjustment. The value to be pro-

grammed to the offset register is simply the binary representation

of the adjustment value.

Removing Gain Error

The AD5764R can eliminate a gain error at negative full-scale

output in the range of 9.77 mV to +9.46 mV with a step size of

one-half of a 16-bit LSB.

1.

Calculate the step size of the gain adjustment, using the

following equation:

Gain Adjust Step Size =

2

20

16 ×

= 152.59 V

2.

Measure the gain error by programming 0x8000 to the

data register and measuring the resulting output voltage.

The gain error is the difference between this value and 10 V.

For this example, the gain error is 1.2 mV.

3.

Determine how many gain adjustment steps this value

represents, using the following equation:

Number of Steps =

V

59

.

152

mV

2

.

1

=

Size

Step

Gain

Value

Gain

Measured

= 8 Steps

The gain error measured is negative (in terms of magnitude).

Therefore, a positive adjustment of eight steps is required. The

gain register is six bits wide, and the coding is twos complement.

The required gain register value can be determined as follows:

1.

Convert the adjustment value to binary: 001000.

2.

Program this binary number to the gain register.

相关PDF资料 |

PDF描述 |

|---|---|

| MS27497E16F26SLC | CONN HSG RCPT 26POS WALL MT SCKT |

| VI-21H-MY-F2 | CONVERTER MOD DC/DC 52V 50W |

| VE-23P-MY-F4 | CONVERTER MOD DC/DC 13.8V 50W |

| VI-21F-MY-F4 | CONVERTER MOD DC/DC 72V 50W |

| MS27505E17B35BC | CONN HSG RCPT 55POS BOX MT SCKT |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD5764RCSUZ-REEL7 | 功能描述:IC DAC QUAD 16BIT VOUT 32-TQFP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1,000 系列:- 设置时间:1µs 位数:8 数据接口:串行 转换器数目:8 电压电源:双 ± 功率耗散(最大):941mW 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:24-SOIC(0.295",7.50mm 宽) 供应商设备封装:24-SOIC W 包装:带卷 (TR) 输出数目和类型:8 电压,单极 采样率(每秒):* |

| AD5764SSUZ-EP-RL7 | 功能描述:16 Bit Digital to Analog Converter 4 32-TQFP (7x7) 制造商:analog devices inc. 系列:iCMOS? 包装:剪切带(CT) 零件状态:有效 位数:16 数模转换器数:4 建立时间:10μs 输出类型:Voltage - Buffered 差分输出:无 数据接口:SPI,DSP 参考类型:外部 电压 - 电源,模拟:±11.4 V ~ 16.5 V 电压 - 电源,数字:2.7 V ~ 5.25 V INL/DNL(LSB):±2(最大),±1(最大) 架构:R-2R 工作温度:-55°C ~ 125°C 封装/外壳:32-TQFP 供应商器件封装:32-TQFP(7x7) 标准包装:1 |

| AD5765 | 制造商:AD 制造商全称:Analog Devices 功能描述:Complete Quad, 16-Bit, High Accuracy, Serial Input, ±5V DACs |

| AD5765BSUZ | 功能描述:IC DAC 16BIT +/-5V QUAD 2LSB 32L RoHS:是 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:- 产品培训模块:Data Converter Fundamentals DAC Architectures 标准包装:750 系列:- 设置时间:7µs 位数:16 数据接口:并联 转换器数目:1 电压电源:双 ± 功率耗散(最大):100mW 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-LCC(J 形引线) 供应商设备封装:28-PLCC(11.51x11.51) 包装:带卷 (TR) 输出数目和类型:1 电压,单极;1 电压,双极 采样率(每秒):143k |

| AD5765BSUZ-REEL7 | 功能描述:IC DAC 16BIT 5V QUAD 32-TQFP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:- 产品培训模块:Data Converter Fundamentals DAC Architectures 标准包装:750 系列:- 设置时间:7µs 位数:16 数据接口:并联 转换器数目:1 电压电源:双 ± 功率耗散(最大):100mW 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-LCC(J 形引线) 供应商设备封装:28-PLCC(11.51x11.51) 包装:带卷 (TR) 输出数目和类型:1 电压,单极;1 电压,双极 采样率(每秒):143k |

发布紧急采购,3分钟左右您将得到回复。