- 您现在的位置:买卖IC网 > PDF目录373890 > AD6623 (Analog Devices, Inc.) 4-Channel, 104 MSPS Digital Transmit Signal Processor TSP PDF资料下载

参数资料

| 型号: | AD6623 |

| 厂商: | Analog Devices, Inc. |

| 英文描述: | 4-Channel, 104 MSPS Digital Transmit Signal Processor TSP |

| 中文描述: | 4通道,104 MSPS的数字传输信号处理器判刑 |

| 文件页数: | 37/40页 |

| 文件大小: | 381K |

| 代理商: | AD6623 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页当前第37页第38页第39页第40页

REV. 0

AD6623

–37–

Time Restriction CMEM Restriction

N

L

RCF

RCF

≤

×

min

1

2

,16

256

(31)

DMEM Restriction

where:

L

L

L

L

M

N

f

f

RCF

CIC

CIC

CIC

TSP

CLK

IN

=

×

×

=

×

5

2

2

(32)

De-interleaving the input data into multiple TSPs extends the

time restriction and may possibly extend the DMEM restriction,

but will not extend the CMEM restriction. Deinterleaving the

input stream to multiple TSPs divides the input sample rate to

each TSP by the number of TSPs used (N

TSP

). To keep the output

rate fixed, L must be increased by a factor of N

CH

, which extends

the time restriction. This increase in L may be achieved by increas-

ing

any one or more of L

RCF

, L

CIC5

, or L

CIC2

within their normal

limits. Achieving a larger L by increasing L

RCF

instead of L

CIC5

or L

CIC2

will relieves the DMEM restriction as well.

In a UMTS example, N

TSP

= 4, f

CLK

= 76.8 MHz, and f

IN

=

3.84 MHz, resulting in L = 80. Factoring L into L

RCF

= 10,

L

CIC

= 8, and L

CIC2

= 1 results in a maximum N

RCF

= 40 due to

the time restriction. Figure 37 shows an example RCF impulse

response which has a frequency response as shown in Figure 38

from 0 Hz to 7.68 MHz (f

IN

L

RCF

/N

TSP

). The composite RCF

and CIC frequency response is shown in Figure 38, on the same

frequency scale. This figure demonstrates a good approximation

to a root-raised-cosine with a roll-off factor of 0.22, a passband

ripple of 0.1 dB, and a stopband ripple better than

–

70 dB until

the lobe of the first image which peaks at

–

60 dB about 7.68 MHz

from the carrier center. This lobe could be reduced by shifting

more of the interpolation towards the RCF, but that would

sacrifice near in performance. As shown, the first image can be

easily rejected by an analog filter further up the signal path.

Scaling must be considered as normal with an interpolation

factor of L, to guarantee no overflow in the RCF, CIC, or NCOs.

The output level at the summation port should be calculated

using an interpolation factor of L/N

TSP

.

Programming Multiple TSPs

Configuring the TSPs for de-interleaved operation is straight

forward. All the Channel Registers and the CMEM of each TSP

are programmed identically, except the Start Hold-Off Counters

and NCO Phase Offset.

In order to separate the input timing to each TSP, the Hold-Off

Counters must be used to start each TSP successively in response

to a common Start SYNC. The Start SYNC may originate from

the SYNC pin or the MicroPort. Each subsequent TSP must have

a Hold-Off Counter value L/N

TSP

larger than its predecessor

’

s.

If the TSPs are located on cascaded

AD6623s, the Hold-Off

Counters of the upstream device should

be incremented by an

additional one.

In the UMTS example, L = 80 and N

TSP

= 4, so to respond as

quickly as possible to a Start SYNC, the Hold-Off Counter

values should be 1, 21, 41, and 61.

Driving Multiple TSP Serial Ports

When configured properly, the AD6623 will drive each SDFO

out of phase. Each new piece of data should be driven only into

the TSP that pulses its SDFO pin at that time.

In the UMTS example in Figure 35, L = 80 and N

TSP

= 4, so

each serial port need only accept every fourth input sample.

Each serial port is shifting at peak capacity, so sample 1, 2, and

3 begin shifting into Serial Ports B, C, and D before sample 0 is

completed into Serial Port A.

SDFOA

SDFOB

SDFOC

SDFOD

0

4

1

5

2

7

6

3

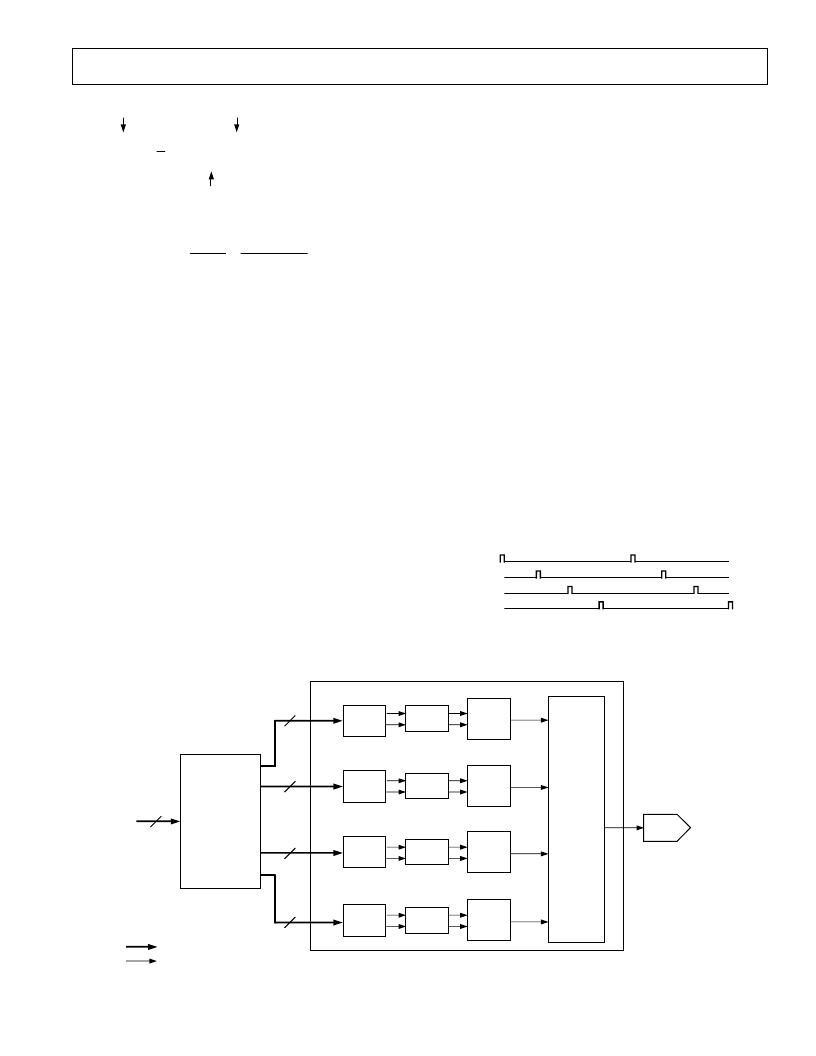

Figure 35. UMTS Example

RAM

COEF

FILTER

CIC

NCO

SUMMATION

BLOCK

CIC

NCO

CIC

NCO

CIC

NCO

DATA

RE-FORMATTER

DAC

RAM

COEF

FILTER

RAM

COEF

FILTER

RAM

COEF

FILTER

76.8 MSAMPLES/SEC

76.8MSPS

76.8MSPS

76.8MSPS

76.8MSPS

9.6MSPS

9.6MSPS

9.6MSPS

9.6MSPS

0.96

MCPS

0.96

MCPS

0.96

MCPS

0.96

MCPS

3.84 MCPS

32

32

32

32

32

I

Q

I

Q

I

Q

I

Q

COMLEX SIGNAL 32 BITS (16, I, 16 Q)

REAL OR IMAGINARY SIGNAL

Figure 36. Summation Block

相关PDF资料 |

PDF描述 |

|---|---|

| AD6623ABC | 4-Channel, 104 MSPS Digital Transmit Signal Processor TSP |

| AD6623AS | 4-Channel, 104 MSPS Digital Transmit Signal Processor TSP |

| AD6623PCB | 4-Channel, 104 MSPS Digital Transmit Signal Processor TSP |

| AD6624AS | Four-Channel, 80 MSPS Digital Receive Signal Processor (RSP) |

| AD6624A | Four-Channel, 100 MSPS Digital Receive Signal Processor (RSP) |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD6623ABC | 制造商:Analog Devices 功能描述:Signal Processor 196-Pin CSP-BGA 制造商:Rochester Electronics LLC 功能描述:4 CHANNEL, 104 MSPS DIGITAL TSP - Bulk |

| AD6623ABCZ | 制造商:Analog Devices 功能描述:Signal Processor 196-Pin CSP-BGA |

| AD6623AS | 制造商:Analog Devices 功能描述:Signal Processor 128-Pin MQFP 制造商:Rochester Electronics LLC 功能描述:4 CHANNEL, 104 MSPS DIGITAL TSP - Bulk |

| AD6623ASZ | 功能描述:IC TSP 4CHAN 104MSPS 128MQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 专用 系列:- 特色产品:NXP - I2C Interface 标准包装:1 系列:- 应用:2 通道 I²C 多路复用器 接口:I²C,SM 总线 电源电压:2.3 V ~ 5.5 V 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:剪切带 (CT) 安装类型:表面贴装 产品目录页面:825 (CN2011-ZH PDF) 其它名称:568-1854-1 |

| AD6623BC/PCB | 制造商:AD 制造商全称:Analog Devices 功能描述:4-Channel, 104 MSPS Digital Transmit Signal Processor TSP |

发布紧急采购,3分钟左右您将得到回复。