参数资料

| 型号: | AD6623ASZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 20/48页 |

| 文件大小: | 0K |

| 描述: | IC TSP 4CHAN 104MSPS 128MQFP |

| 标准包装: | 1 |

| 应用: | 传输信息处理器 |

| 接口: | 串行 |

| 封装/外壳: | 128-BFQFP |

| 供应商设备封装: | 128-MQFP(14x20) |

| 包装: | 托盘 |

| 安装类型: | 表面贴装 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页当前第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页

REV. A

AD6623

–27–

In the complex mode, the NCO serves as a quadrature local oscillator

running at fCLK/2 capable of producing any frequency step between

–fCLK/4 and +fCLK/4 with a resolution of fCLK/2

33 (0.0121 Hz for

fCLK = 104 MHz).

In the real mode, the NCO serves as a quadrature local oscillator

running at fCLK capable of producing any frequency step between

–fCLK/2 and +fCLK/2 with a resolution of fCLK/2

32 (0.0242 Hz for

fCLK = 104 MHz). The quadrature portion of the output is

discarded. Negative frequencies are distinguished from positive

frequencies solely by spectral inversion. The digital IF is calculated

using the equation:

ff

NCO

frequency

IF

NCO

=×

_

2

32

(22)

where:

NCO_frequency is the decimal equivalent of the 32-bit binary

value written to 0xn02,

fIF is the desired intermediate frequency (in Hz), and

fNCO is fCLK/2 (in Hz) for complex outputs and fCLK (in Hz)

for real outputs.

Phase Dither

The AD6623 provides a phase dither option for improving the

spurious performance of the NCO. Phase dither is enabled by

writing a “1” to Bit 3 of Channel Register 0xn01. When phase

dither is enabled, spurs due to phase truncation in the NCO are

randomized. The choice of whether phase dither is used in a system

will ultimately be decided by the system goals and the choice of IF

frequency. The 18 most significant bits of the phase accumulator

are used by the angle to Cartesian conversion. If the NCO frequency

has all zeroes below the 18

th bit, then phase dither has no effect.

If the fraction below the 18

th bit is near a 1/2 or 1/3 of the 18th

bit, then spurs will accumulate separated from the IF by 1/2 or

1/3 of the CLK frequency. The smaller the denominator of this

residual fraction, the larger the spurs due to phase truncation will

be. If the phase truncation spurs are unacceptably high for a given

frequency, then the phase dither can reduce these at the penalty

of a slight elevation in total error energy. If the phase truncation

spurs are small, then phase dither will not be effective in reducing

them further, but a slight elevation in total error energy will occur.

Amplitude Dither

Amplitude dither can also be used to improve spurious performance

of the NCO. Amplitude dither is enabled by writing a “1” to Bit 4

of Channel Register at 0xn01. When enabled, amplitude dither

can reduce spurs due to truncation at the input to the QAM. If

the entire frequency word is close to a fraction that has a small

32

Q

D

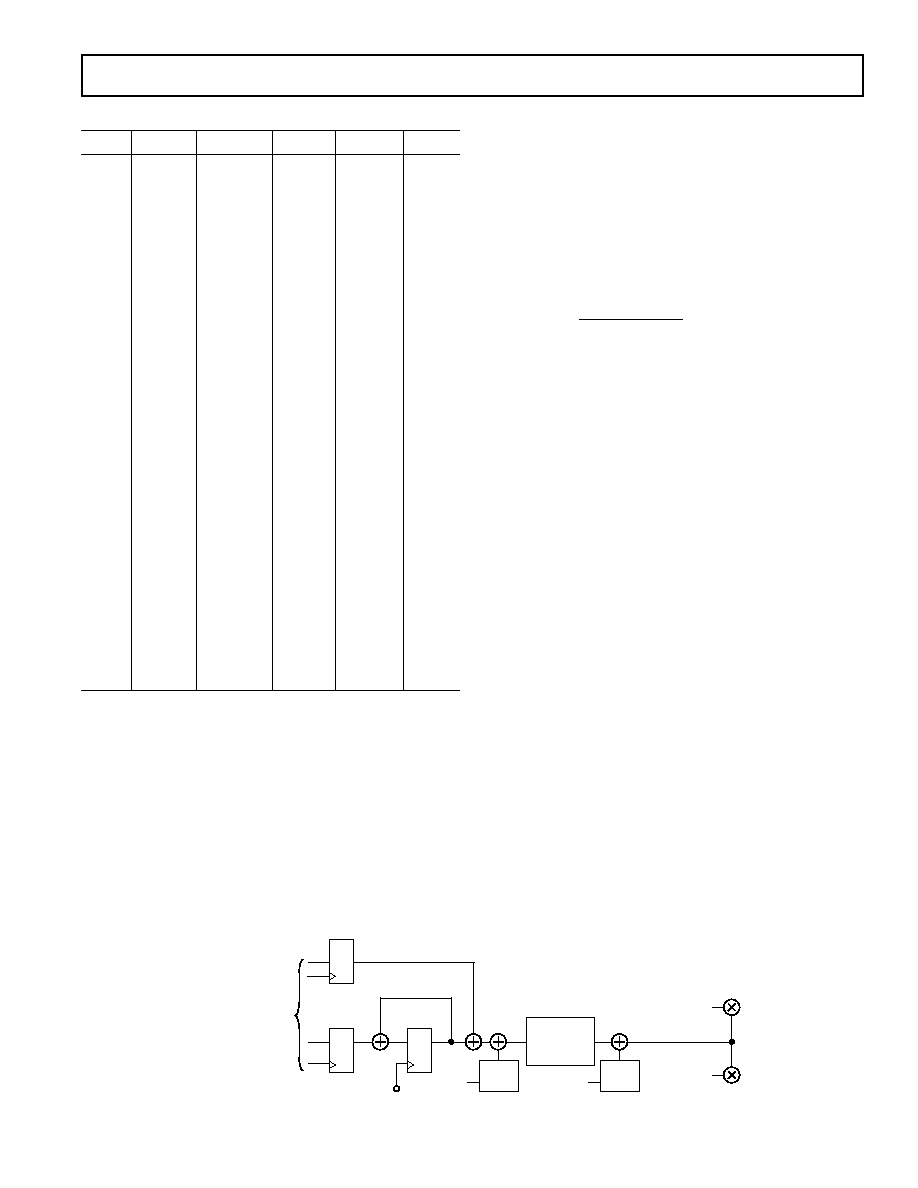

PN

GEN.

NCO

FREQUENCY

WORD

16

PHASE

OFFSET

16

32

Q

D

ANGLE TO

CARTESIAN

CONVERSION

PN

GEN.

I DATA FROM

CIC5

Q DATA FROM

CIC5

I

Q

I, Q

CLK

ON

OFF

ON

OFF

32

MICROPROCESSOR

INTERFACE

Figure 33. Numerically Controlled Oscillator and QAM Mixer

Table XIV. Maximum Bandwidth of Rejection for LrCIC2 Values

LrCIC2

–110 dB

–100 dB

–90 dB

–80 dB

–70 dB

1

Full

2

0.0023

0.0040

0.0072

0.0127

0.0226

3

0.0029

0.0052

0.0093

0.0165

0.0292

4

0.0032

0.0057

0.0101

0.0179

0.0316

5

0.0033

0.0059

0.0105

0.0186

0.0328

6

0.0034

0.0060

0.0107

0.0189

0.0334

7

0.0034

0.0061

0.0108

0.0192

0.0338

8

0.0035

0.0062

0.0109

0.0193

0.0341

9

0.0035

0.0062

0.0110

0.0194

0.0343

10

0.0035

0.0062

0.0110

0.0195

0.0344

11

0.0035

0.0062

0.0110

0.0195

0.0345

12

0.0035

0.0062

0.0111

0.0196

0.0346

13

0.0035

0.0062

0.0111

0.0196

0.0346

14

0.0035

0.0063

0.0111

0.0196

0.0346

15

0.0035

0.0063

0.0111

0.0197

0.0347

16

0.0035

0.0063

0.0111

0.0197

0.0347

17

0.0035

0.0063

0.0111

0.0197

0.0347

18

0.0035

0.0063

0.0111

0.0197

0.0348

19

0.0035

0.0063

0.0111

0.0197

0.0348

20

0.0035

0.0063

0.0111

0.0197

0.0348

21

0.0035

0.0063

0.0111

0.0197

0.0348

22

0.0035

0.0063

0.0111

0.0197

0.0348

23

0.0035

0.0063

0.0111

0.0197

0.0348

24

0.0035

0.0063

0.0112

0.0197

0.0348

25

0.0035

0.0063

0.0112

0.0198

0.0348

26

0.0035

0.0063

0.0112

0.0198

0.0349

27

0.0035

0.0063

0.0112

0.0198

0.0349

28

0.0035

0.0063

0.0112

0.0198

0.0349

29

0.0035

0.0063

0.0112

0.0198

0.0349

30

0.0035

0.0063

0.0112

0.0198

0.0349

31

0.0035

0.0063

0.0112

0.0198

0.0349

32

0.0035

0.0063

0.0112

0.0198

0.0349

NUMERICALLY CONTROLLED OSCILLATOR/TUNER (NCO)

Each channel has a fully independent tuner. The tuner accepts

data from the CIC filter, tunes it to a digital Intermediate

Frequency (IF), and passes the result to a shared summation block.

The tuner consists of a 32-bit quadrature NCO and a Quadrature

Amplitude Mixer (QAM). The NCO serves as a local oscillator and

the QAM translates the interpolated channel data from baseband

to the NCO frequency. The worst case spurious signal from the

NCO is better than –100 dBc for all output frequencies. The tuner

can produce real or complex outputs as requested by the shared

summation block.

相关PDF资料 |

PDF描述 |

|---|---|

| AD6641BCPZRL7-500 | IC IF RCVR 11BIT 200MSPS 56LFCSP |

| AD664BJ | IC DAC 12BIT QUAD MONO 44-JLCC |

| AD667BD | IC DAC 12BIT W/BUFF LTCH 28-CDIP |

| AD669BN | IC DAC 16BIT MONO VREF 28-DIP |

| AD693AE | IC SGNL COND 4-20MA TX 20-CLCC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD6623BC/PCB | 制造商:AD 制造商全称:Analog Devices 功能描述:4-Channel, 104 MSPS Digital Transmit Signal Processor TSP |

| AD6623PCB | 制造商:AD 制造商全称:Analog Devices 功能描述:4-Channel, 104 MSPS Digital Transmit Signal Processor TSP |

| AD6623S/PCB | 制造商:Analog Devices 功能描述:4-CH, 104 MSPS DGTL TRANSMIT SGNL PROCESSOR (TSP) 28SOIC - Bulk |

| AD6624 | 制造商:AD 制造商全称:Analog Devices 功能描述:Four-Channel, 80 MSPS Digital Receive Signal Processor (RSP) |

| AD6624A | 制造商:AD 制造商全称:Analog Devices 功能描述:Four-Channel, 100 MSPS Digital Receive Signal Processor (RSP) |

发布紧急采购,3分钟左右您将得到回复。