- 您现在的位置:买卖IC网 > PDF目录9508 > AD7142ACPZ-1REEL (Analog Devices Inc)IC CAP-TO-DGTL CONV PROG 32LFCSP PDF资料下载

参数资料

| 型号: | AD7142ACPZ-1REEL |

| 厂商: | Analog Devices Inc |

| 文件页数: | 20/73页 |

| 文件大小: | 0K |

| 描述: | IC CAP-TO-DGTL CONV PROG 32LFCSP |

| 标准包装: | 1 |

| 类型: | 电容数字转换器 |

| 分辨率(位): | 16 b |

| 采样率(每秒): | 250k |

| 数据接口: | 串行 |

| 电压电源: | 单电源 |

| 电源电压: | 2.6 V ~ 3.6 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 32-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 32-LFCSP-VQ |

| 包装: | 标准包装 |

| 产品目录页面: | 781 (CN2011-ZH PDF) |

| 其它名称: | AD7142ACPZ-1REELDKR |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页当前第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页

AD7142

Rev. A | Page 26 of 72

INTERRUPT OUTPUT

The AD7142 has an interrupt output that triggers an interrupt

service routine on the host processor. The INT signal is on

Pin 25, and is an open-drain output. There are three types of

interrupt events on the AD7142: a CDC conversion complete

interrupt, a sensor threshold interrupt, and a GPIO interrupt.

Each interrupt has enable and status registers. The conversion

complete and sensor threshold interrupts can be enabled on a

per conversion stage basis. The status registers indicate what

type of interrupt triggered the INT pin. Status registers are

cleared, and the INT signal is reset high, during a read

operation. The signal returns high as soon as the read address

has been set up.

CDC CONVERSION COMPLETE INTERRUPT

The AD7142 interrupt signal asserts low to indicate the

completion of a conversion stage, and new conversion result

data is available in the registers.

The interrupt can be independently enabled for each conversion

stage. Each conversion stage complete interrupt can be enabled via

the STAGE_COMPLETE_EN register (Address 0x007). This

register has a bit that corresponds to each conversion stage. Setting

this bit to 1 enables the interrupt for that stage. Clearing this bit to 0

disables the conversion complete interrupt for that stage.

In normal operation, the AD7142 interrupt is enabled only for the

last stage in a conversion sequence. For example, if there are five

conversion stages, the conversion complete interrupt for STAGE4 is

enabled. INT only asserts when all five conversion stages are

complete, and the host can read new data from all five result

registers. The interrupt is cleared by reading the STAGE_

COMPLETE_STATUS_INT register located at Address 0x00A.

Register 0x00A is the conversion complete interrupt status

register. Each bit in this register corresponds to a conversion

stage. If a bit is set, it means that the conversion complete

interrupt for the corresponding stage was triggered. This

register is cleared on a read, provided the underlying condition

that triggered the interrupt has gone away.

SENSOR TOUCH INTERRUPT

Use the sensor touch interrupt mode to interrupt the host

processor only when the sensor is activated.

Configuring the AD7142 into this mode results in the interrupt

being asserted when the user makes contact with the sensor and

again when the user lifts off the sensor. The second interrupt is

required to alert the host processor that the user is no longer

contacting the sensor.

The registers located at Address 0x005 and Address 0x006 are

used to enable the interrupt output for each stage. The registers

located at Address 0x008 and Address 0x009 are used to read

back the interrupt status for each stage.

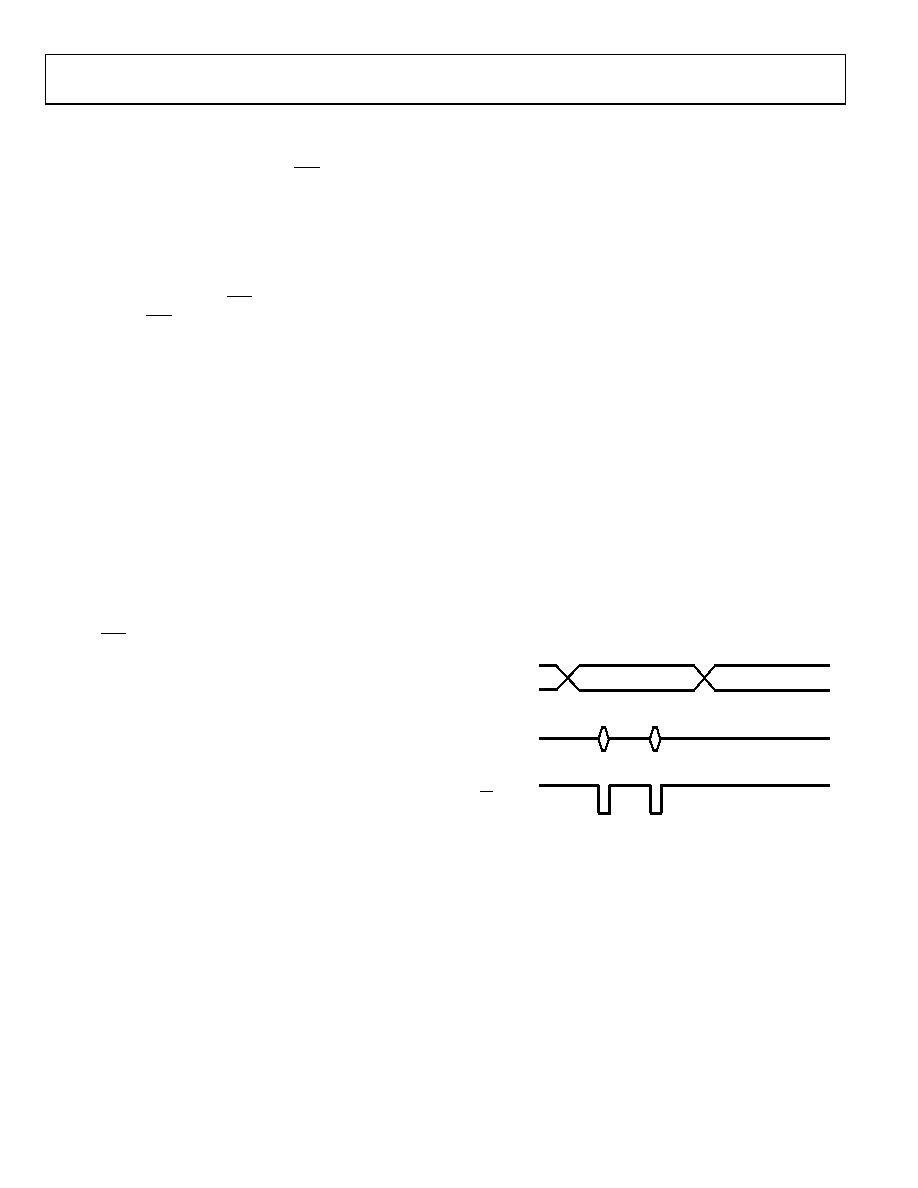

Figure 38 shows the interrupt output timing during contact with

one of the sensors connected to STAGE0 when operating in the

sensor touch interrupt mode. For a low limit configuration, the

interrupt output is asserted as soon as the sensor is contacted and

again after the user has stopped contacting the sensor.

Note: The interrupt output remains low until the host processor

reads back the interrupt status registers located at Address 0x008

and Address 0x009.

The interrupt output is asserted when there is a change in the

threshold status bits. This could indicate that a user is now

touching the sensor(s) for the first time, the number of sensors

being touched has changed, or the user is no longer touching

the sensor(s). Reading the status bits in the interrupt status

register shows the current sensor activations.

4

2

CONVERSION

STAGE

SERIAL

READBACK

NOTES:

1. USER TOUCHING DOWN ON SENSOR

2. ADDRESS 0X008 READ BACK TO CLEAR INTERRUPT

3. USER LIFTING OFF OF SENSOR

4. ADDRESS 0X008 READ BACK TO CLEAR INTERRUPT

STAGE0

STAGE1

INT OUTPUT

05702-

055

Figure 38. Example of Sensor Touch Interrupt

相关PDF资料 |

PDF描述 |

|---|---|

| V110A8M200BL2 | CONVERTER MOD DC/DC 8V 200W |

| CS3106A-24-67P | CONN PLUG 19POS STRAIGHT W/PINS |

| V110A8M200BL | CONVERTER MOD DC/DC 8V 200W |

| MS27497T18F35SC | CONN RCPT 66POS WALL MNT W/SCKT |

| V110A8M200B3 | CONVERTER MOD DC/DC 8V 200W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD7142ACPZ-1REEL1 | 制造商:AD 制造商全称:Analog Devices 功能描述:Programmable Controller for Capacitance Touch Sensors |

| AD7142ACPZ-500RL7 | 功能描述:IC CAP-TO-DGTL CONV PROG 32LFCSP RoHS:是 类别:集成电路 (IC) >> 数据采集 - ADCs/DAC - 专用型 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:50 系列:- 类型:数据采集系统(DAS) 分辨率(位):16 b 采样率(每秒):21.94k 数据接口:MICROWIRE?,QSPI?,串行,SPI? 电压电源:模拟和数字 电源电压:1.8 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:40-WFQFN 裸露焊盘 供应商设备封装:40-TQFN-EP(6x6) 包装:托盘 |

| AD7142ACPZ-500RL71 | 制造商:AD 制造商全称:Analog Devices 功能描述:Programmable Controller for Capacitance Touch Sensors |

| AD7142ACPZ-REEL | 功能描述:IC CAP-TO-DGTL CONV PROG 32LFCSP RoHS:是 类别:集成电路 (IC) >> 数据采集 - ADCs/DAC - 专用型 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:50 系列:- 类型:数据采集系统(DAS) 分辨率(位):16 b 采样率(每秒):21.94k 数据接口:MICROWIRE?,QSPI?,串行,SPI? 电压电源:模拟和数字 电源电压:1.8 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:40-WFQFN 裸露焊盘 供应商设备封装:40-TQFN-EP(6x6) 包装:托盘 |

| AD7142ACPZ-REEL1 | 制造商:AD 制造商全称:Analog Devices 功能描述:Programmable Controller for Capacitance Touch Sensors |

发布紧急采购,3分钟左右您将得到回复。