- 您现在的位置:买卖IC网 > PDF目录10756 > AD73311LARSZ (Analog Devices Inc)IC PROCESSOR FRONT END LP 20SSOP PDF资料下载

参数资料

| 型号: | AD73311LARSZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 28/36页 |

| 文件大小: | 0K |

| 描述: | IC PROCESSOR FRONT END LP 20SSOP |

| 标准包装: | 66 |

| 位数: | 16 |

| 通道数: | 2 |

| 功率(瓦特): | 50mW |

| 电压 - 电源,模拟: | 3V |

| 电压 - 电源,数字: | 3V |

| 封装/外壳: | 20-SSOP(0.209",5.30mm 宽) |

| 供应商设备封装: | 20-SSOP |

| 包装: | 管件 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页当前第28页第29页第30页第31页第32页第33页第34页第35页第36页

AD73311

–34–

REV. B

APPENDIX E

DAC Timing Control Example

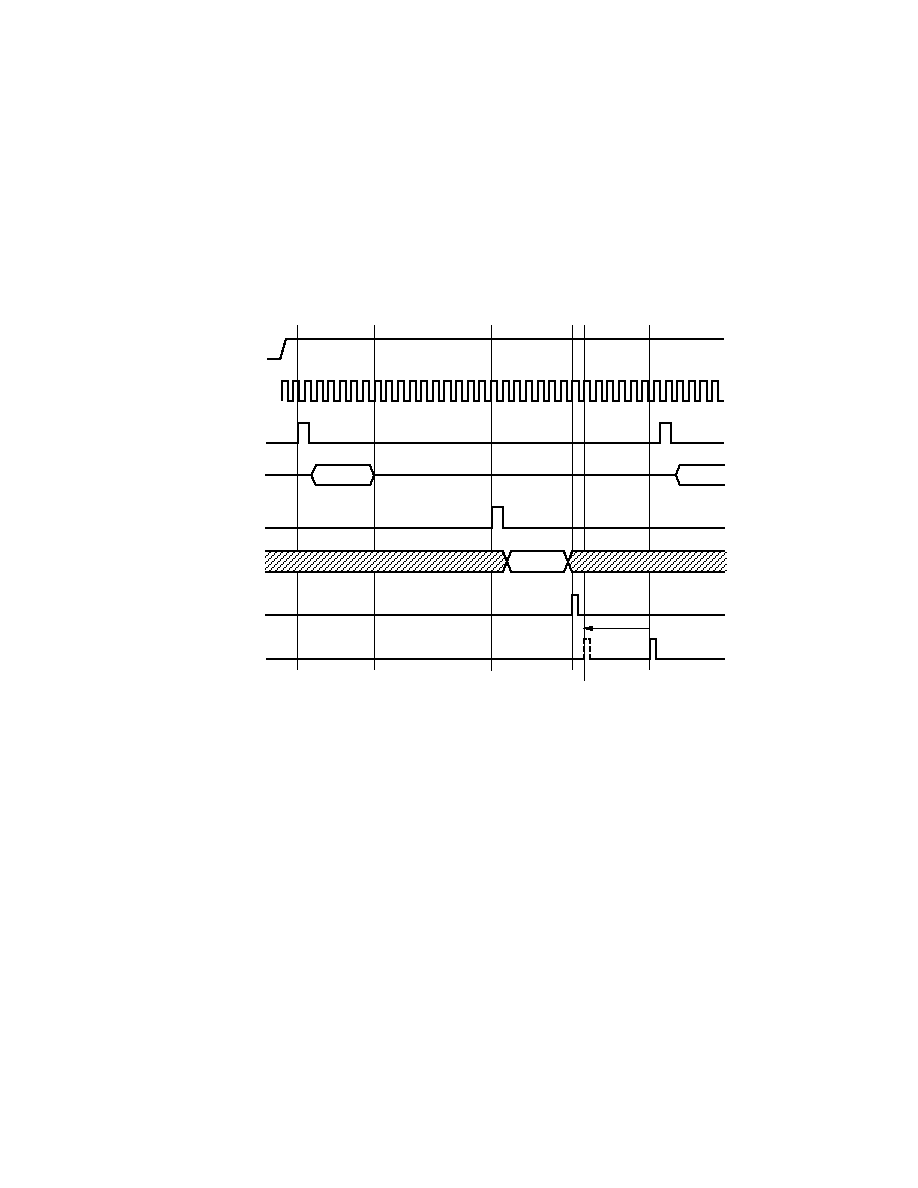

The AD73311’s DAC is loaded from the DAC register contents

just before the ADC register contents are loaded to the serial

register (SDOFS going high). This default DAC load position

can be advanced in time to occur earlier with respect to the

SDOFS going high. Figure 37 shows an example of the ADC

unload and DAC load sequence. At time t1 the SDOFS is raised

to indicate that a new ADC word is ready. Following the SDOFS

pulse, 16 bits of ADC data are clocked out on SDO in the sub-

sequent 16 SCLK cycles finishing at time t2 where the DSP’s

SPORT will have received the 16-bit word. The DSP may

ADC WORD

DAC WORD

SE

SCLK

SDOFS

SDO

SDIFS

SDI

DAC REGISTER

UPDATE

DAC LOAD

FROM DAC REGISTER

t6

t4

t5

t3

t2

t1

Figure 37. DAC Timing Control

process this information and generate a DAC word to be sent to

the AD73311. Time t3 marks the beginning of the sequence of

sending the DAC word to the AD73311. This sequence ends at

time t4 where the DAC register will be updated from the 16 bits

in the AD73311’s serial register. However, the DAC will not be

updated from the DAC register until time t5 which may not be

acceptable in certain applications. In order to reduce this delay

and load the DAC at time t6, the DAC advance register can be

programmed with a suitable setting corresponding to the

required time advance (refer to Table VIII for details of DAC

Timing Control settings).

相关PDF资料 |

PDF描述 |

|---|---|

| VI-B6N-IV-S | CONVERTER MOD DC/DC 18.5V 150W |

| VE-J3B-MY-F1 | CONVERTER MOD DC/DC 95V 50W |

| VE-J34-MY-F4 | CONVERTER MOD DC/DC 48V 50W |

| VE-J5D-MW-F2 | CONVERTER MOD DC/DC 85V 100W |

| VE-J3D-MY-F2 | CONVERTER MOD DC/DC 85V 50W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD73311LARSZ-REEL | 功能描述:IC PROCESSOR FRONT END LP 20SSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模拟前端 (AFE) 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 位数:- 通道数:2 功率(瓦特):- 电压 - 电源,模拟:3 V ~ 3.6 V 电压 - 电源,数字:3 V ~ 3.6 V 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:带卷 (TR) |

| AD73311LARSZ-REEL7 | 功能描述:IC PROCESSOR FRONT END LP 20SSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模拟前端 (AFE) 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 位数:- 通道数:2 功率(瓦特):- 电压 - 电源,模拟:3 V ~ 3.6 V 电压 - 电源,数字:3 V ~ 3.6 V 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:带卷 (TR) |

| AD73311LARU | 制造商:Analog Devices 功能描述:Audio Codec 1ADC / 1DAC 16-Bit 20-Pin TSSOP |

| AD73311LARU-REEL | 制造商:Analog Devices 功能描述:Audio Codec 1ADC / 1DAC 16-Bit 20-Pin TSSOP T/R |

| AD73311LARU-REEL7 | 制造商:Analog Devices 功能描述:Audio Codec 1ADC / 1DAC 16-Bit 20-Pin TSSOP T/R |

发布紧急采购,3分钟左右您将得到回复。