- 您现在的位置:买卖IC网 > PDF目录10756 > AD73311LARSZ (Analog Devices Inc)IC PROCESSOR FRONT END LP 20SSOP PDF资料下载

参数资料

| 型号: | AD73311LARSZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 9/36页 |

| 文件大小: | 0K |

| 描述: | IC PROCESSOR FRONT END LP 20SSOP |

| 标准包装: | 66 |

| 位数: | 16 |

| 通道数: | 2 |

| 功率(瓦特): | 50mW |

| 电压 - 电源,模拟: | 3V |

| 电压 - 电源,数字: | 3V |

| 封装/外壳: | 20-SSOP(0.209",5.30mm 宽) |

| 供应商设备封装: | 20-SSOP |

| 包装: | 管件 |

第1页第2页第3页第4页第5页第6页第7页第8页当前第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页

AD73311

–17–

REV. B

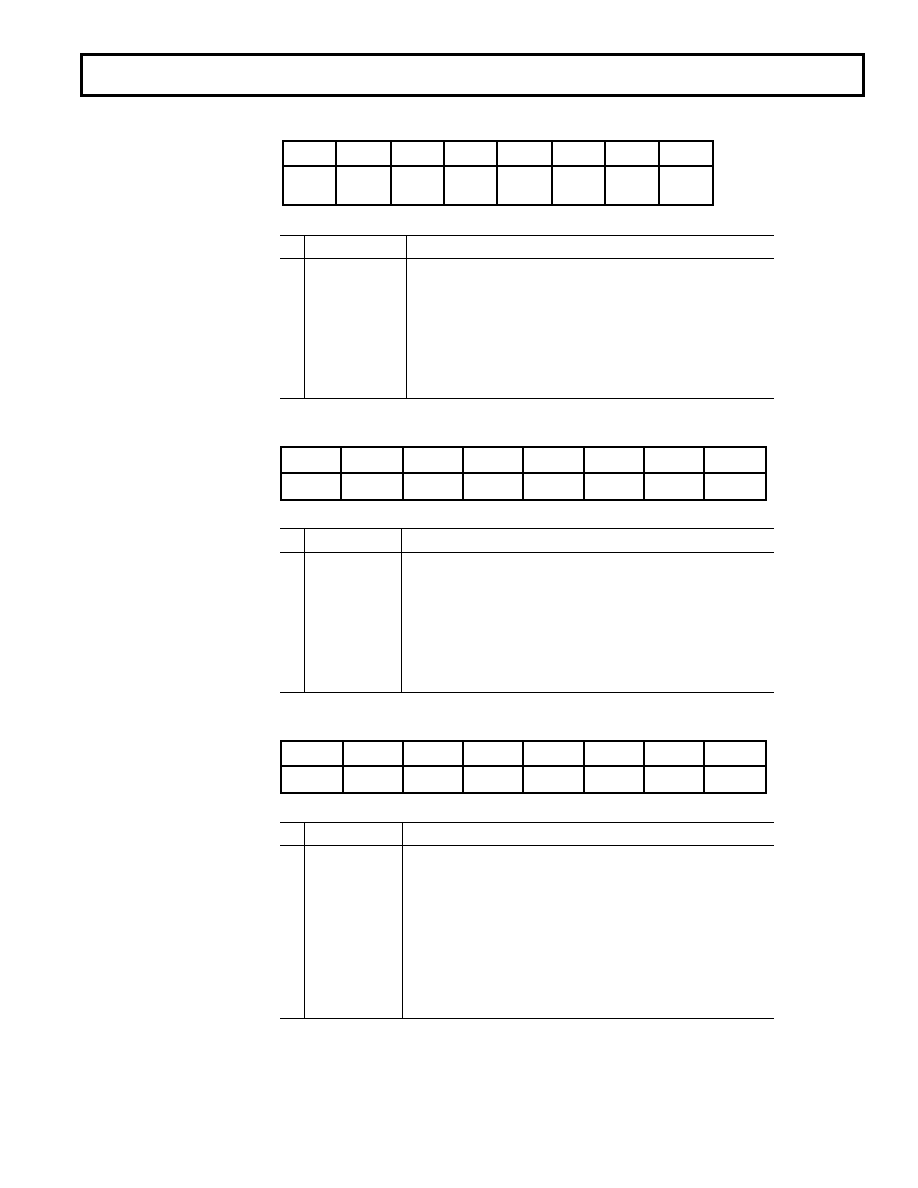

Table XI. Control Register A Description

CONTROL REGISTER A

765

432

10

RESET

DC2

DC1

DC0

DLB

ALB

MM

DATA/

PGM

Bit

Name

Description

0

DATA/

PGM

Operating Mode (0 = Program; 1 = Data Mode)

1

MM

Mixed Mode (0 = Off; 1 = Enabled)

2

ALB

Analog Loop-Back Mode (0 = Off; 1 = Enabled)

3

DLB

Digital Loop-Back Mode (0 = Off; 1 = Enabled)

4

DC0

Device Count (Bit 0)

5

DC1

Device Count (Bit 1)

6

DC2

Device Count (Bit 2)

7

RESET

Software Reset (0 = Off; 1 = Initiates Reset)

Table XII. Control Register B Description

CONTROL REGISTER B

765

432

10

CEE

MCD2

MCD1

MCD0

SCD1

SCD0

1

Bit

Name

Description

0

Reserved

Must Be Programmed to 1

1

Reserved

Must Be Programmed to 1

2

SCD0

Serial Clock Divider (Bit 0)

3

SCD1

Serial Clock Divider (Bit 1)

4

MCD0

Master Clock Divider (Bit 0)

5

MCD1

Master Clock Divider (Bit 1)

6

MCD2

Master Clock Divider (Bit 2)

7

CEE

Control Echo Enable (0 = Off; 1 = Enabled)

Table XIII. Control Register C Description

CONTROL REGISTER C

765

4321

0

5VEN

RU

PUREF

PUDAC PUADC

0

PU

Bit

Name

Description

0

PU

Power-Up Device (0 = Power Down; 1 = Power On)

1

Reserved

Must Be Programmed to 0

2

Reserved

Must Be Programmed to 0

3

PUADC

ADC Power (0 = Power Down; 1 = Power On)

4

PUDAC

DAC Power (0 = Power Down; 1 = Power On)

5

PUREF

REF Power (0 = Power Down; 1 = Power On)

6

RU

REFOUT Use (0 = Disable REFOUT; 1 = Enable

REFOUT)

7

5VEN

Enable 5 V Operating Mode (0 = Disable 5 V Mode;

1 = Enable 5 V Mode)

相关PDF资料 |

PDF描述 |

|---|---|

| VI-B6N-IV-S | CONVERTER MOD DC/DC 18.5V 150W |

| VE-J3B-MY-F1 | CONVERTER MOD DC/DC 95V 50W |

| VE-J34-MY-F4 | CONVERTER MOD DC/DC 48V 50W |

| VE-J5D-MW-F2 | CONVERTER MOD DC/DC 85V 100W |

| VE-J3D-MY-F2 | CONVERTER MOD DC/DC 85V 50W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD73311LARSZ-REEL | 功能描述:IC PROCESSOR FRONT END LP 20SSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模拟前端 (AFE) 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 位数:- 通道数:2 功率(瓦特):- 电压 - 电源,模拟:3 V ~ 3.6 V 电压 - 电源,数字:3 V ~ 3.6 V 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:带卷 (TR) |

| AD73311LARSZ-REEL7 | 功能描述:IC PROCESSOR FRONT END LP 20SSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模拟前端 (AFE) 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 位数:- 通道数:2 功率(瓦特):- 电压 - 电源,模拟:3 V ~ 3.6 V 电压 - 电源,数字:3 V ~ 3.6 V 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:带卷 (TR) |

| AD73311LARU | 制造商:Analog Devices 功能描述:Audio Codec 1ADC / 1DAC 16-Bit 20-Pin TSSOP |

| AD73311LARU-REEL | 制造商:Analog Devices 功能描述:Audio Codec 1ADC / 1DAC 16-Bit 20-Pin TSSOP T/R |

| AD73311LARU-REEL7 | 制造商:Analog Devices 功能描述:Audio Codec 1ADC / 1DAC 16-Bit 20-Pin TSSOP T/R |

发布紧急采购,3分钟左右您将得到回复。