- 您现在的位置:买卖IC网 > PDF目录10745 > AD73360ASUZ-REEL (Analog Devices Inc)IC ANALOG FRONT END 6CH 44-TQFP PDF资料下载

参数资料

| 型号: | AD73360ASUZ-REEL |

| 厂商: | Analog Devices Inc |

| 文件页数: | 14/35页 |

| 文件大小: | 0K |

| 描述: | IC ANALOG FRONT END 6CH 44-TQFP |

| 标准包装: | 1,500 |

| 位数: | 16 |

| 通道数: | 6 |

| 功率(瓦特): | 80mW |

| 电压 - 电源,模拟: | 2.7 V ~ 3.3 V |

| 电压 - 电源,数字: | 2.7 V ~ 3.3 V |

| 封装/外壳: | 44-TQFP |

| 供应商设备封装: | 44-TQFP(10x10) |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页当前第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页

REV. A

AD73360

–21–

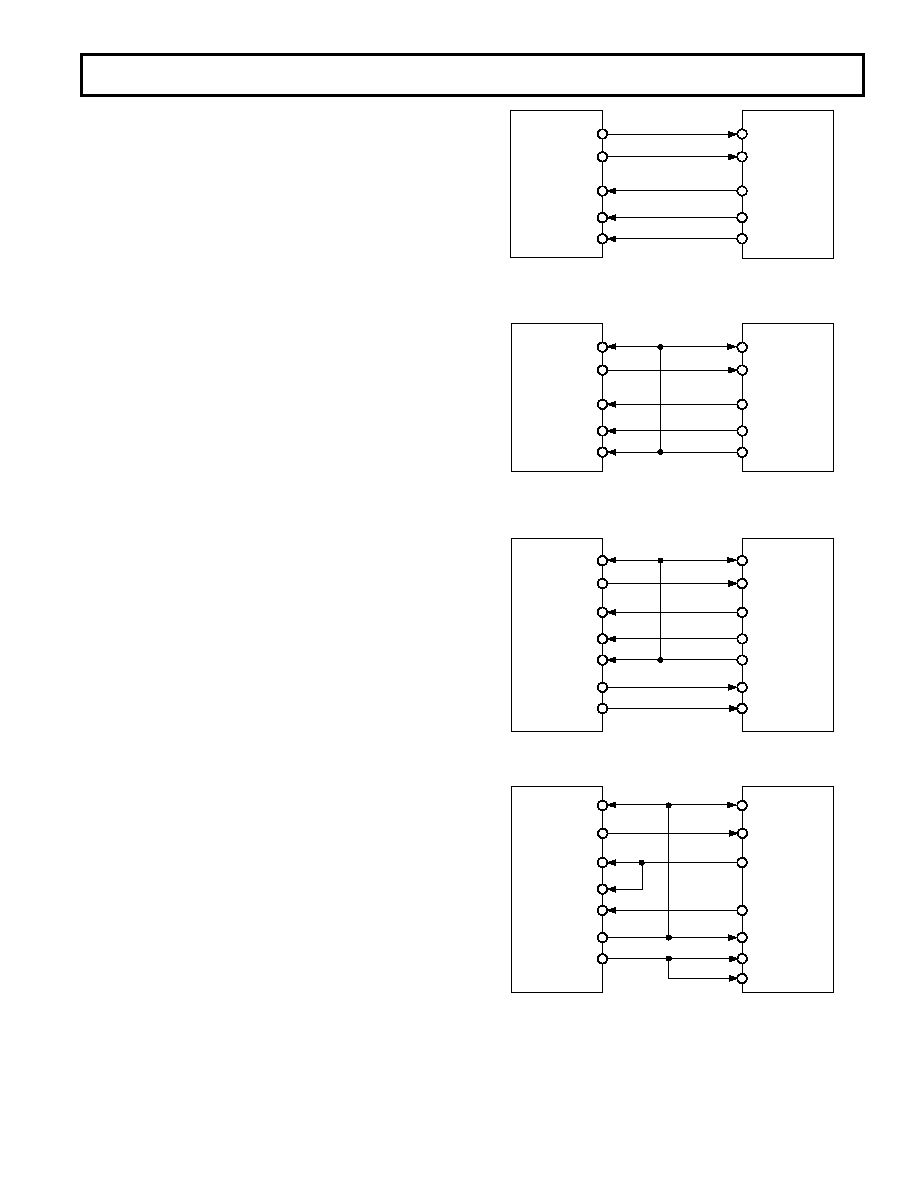

INTERFACING

The AD73360 can be interfaced to most modern DSP engines

using conventional serial port connections and an extra enable

control line. Both serial input and output data use an accompa-

nying frame synchronization signal which is active high one

clock cycle before the start of the 16-bit word or during the last

bit of the previous word if transmission is continuous. The serial

clock (SCLK) is an output from the AD73360 and is used to

define the serial transfer rate to the DSP’s Tx and Rx ports.

Two primary configurations can be used: the first is shown in

Figure 11 where the DSP’s Tx data, Tx frame sync, Rx data and

Rx frame sync are connected to the AD73360’s SDI, SDIFS,

SDO and SDOFS respectively. This configuration, referred to

as indirectly coupled or nonframe sync loop-back, has the effect

of decoupling the transmission of input data from the receipt of

output data. When programming the DSP serial port for this

configuration, it is necessary to set the Rx frame sync as an

input to the DSP and the Tx frame sync as an output generated

by the DSP. This configuration is most useful when operating in

mixed mode, as the DSP has the ability to decide how many

words can be sent to the AD73360(s). This means that full con-

trol can be implemented over the device configuration in a given

sample interval. The second configuration (shown in Figure 12)

has the DSP’s Tx data and Rx data connected to the AD73360’s

SDI and SDO, respectively, while the DSP’s Tx and Rx frame

syncs are connected to the AD73360’s SDIFS and SDOFS. In

this configuration, referred to as directly coupled or frame sync

loop-back, the frame sync signals are connected together and

the input data to the AD73360 is forced to be synchronous with

the output data from the AD73360. The DSP must be pro-

grammed so that both the Tx and Rx frame syncs are inputs as

the AD73360’s SDOFS will be input to both. This configura-

tion guarantees that input and output events occur simulta-

neously and is the simplest configuration for operation in normal

Data Mode. Note that when programming the DSP in this

configuration it is advisable to preload the Tx register with the

first control word to be sent before the AD73360 is taken out of

reset. This ensures that this word will be transmitted to coincide

with the first output word from the device(s).

Digital Interfacing

The AD73360 is designed to easily interface to most common

DSPs. The SCLK, SDO, SDOFS, SDI and SDIFS must be

connected to the SCLK, DR, RFS, DT and TFS pins of the

DSP respectively. The SE pin may be controlled from a parallel

output pin or flag pin such as FL0–2 on the ADSP-21xx (or XF

on the TMS320C5x) or, where SPORT power-down is not

required, it can be permanently strapped high using a suitable

pull-up resistor. The

RESET pin may be connected to the sys-

tem hardware reset structure or it may also be controlled using a

dedicated control line. In the event of tying it to the global

system reset, it is necessary to operate the device in mixed

mode, which allows a software reset, otherwise there is no con-

venient way of resetting the device. Figures 11 and 12 show

typical connections to an ADSP-2181 while Figures 13 and 14

show typical connections to an ADSP-21xx and a TMS320C5x,

respectively.

TFS

DT

SCLK

DR

RFS

ADSP-21xx

DSP

AD73360

SDIFS

SDI

SCLK

SDO

SDOFS

Figure 11. Indirectly Coupled or Nonframe Sync Loop-

Back Configuration

TFS

DT

SCLK

DR

RFS

ADSP-21xx

DSP

AD73360

SDIFS

SDI

SCLK

SDO

SDOFS

Figure 12. Directly Coupled or Frame Sync Loop-

Back Configuration

TFS

DT

SCLK

DR

RFS

ADSP-21xx

DSP

AD73360

ANALOG

FRONT-END

SDIFS

SDI

SCLK

SDO

SDOFS

FL0

FL1

RESET

SE

Figure 13. AD73360 Connected to ADSP-21xx

FSX

DX

CLKX

CLKR

DR

TMS320C5x

DSP

AD73360

ANALOG

FRONT-END

SDIFS

SDI

SCLK

SDO

SDOFS

FSR

XF

RESET

SE

Figure 14. AD73360 Connected to TMS320C5x

相关PDF资料 |

PDF描述 |

|---|---|

| AD73360LARZ-REEL7 | IC PROCESSOR FRONTEND 6CH 28SOIC |

| MAX965EUA+ | IC COMPARATOR R-R 8-UMAX |

| MAX966ESA+ | IC COMPARATOR R-R 8-SOIC |

| VE-JN4-MY-F1 | CONVERTER MOD DC/DC 48V 50W |

| MAX965ESA+ | IC COMPARATOR R-R 8-SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD73360EZEVAL | 制造商:AD 功能描述:73360 ANALOG DEVICE S7L3A |

| AD73360EZ-EVAL | 制造商:AD 功能描述:73360 ANALOG DEVICE S7L3A |

| AD73360L | 制造商:AD 制造商全称:Analog Devices 功能描述:Six-Input Channel Analog Front End |

| AD73360LAR | 制造商:Analog Devices 功能描述:AFE General Purpose 6ADC 16-Bit 3.3V 28-Pin SOIC W 制造商:Analog Devices 功能描述:IC 16-BIT ADC |

| AD73360LAR-REEL | 制造商:Analog Devices 功能描述:AFE General Purpose 6ADC 16-Bit 3.3V 28-Pin SOIC W T/R 制造商:Analog Devices 功能描述:AFE GEN PURPOSE 6ADC 16BIT 3.3V/3.3V/3.3V 28SOIC W - Tape and Reel |

发布紧急采购,3分钟左右您将得到回复。