- 您现在的位置:买卖IC网 > PDF目录10745 > AD73360LARZ-REEL7 (Analog Devices Inc)IC PROCESSOR FRONTEND 6CH 28SOIC PDF资料下载

参数资料

| 型号: | AD73360LARZ-REEL7 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 11/35页 |

| 文件大小: | 0K |

| 描述: | IC PROCESSOR FRONTEND 6CH 28SOIC |

| 标准包装: | 400 |

| 位数: | 16 |

| 通道数: | 6 |

| 功率(瓦特): | 80mW |

| 电压 - 电源,模拟: | 3V |

| 电压 - 电源,数字: | 3V |

| 封装/外壳: | 28-SOIC(0.295",7.50mm 宽) |

| 供应商设备封装: | 28-SOIC W |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页当前第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页

REV. A

AD73360

–19–

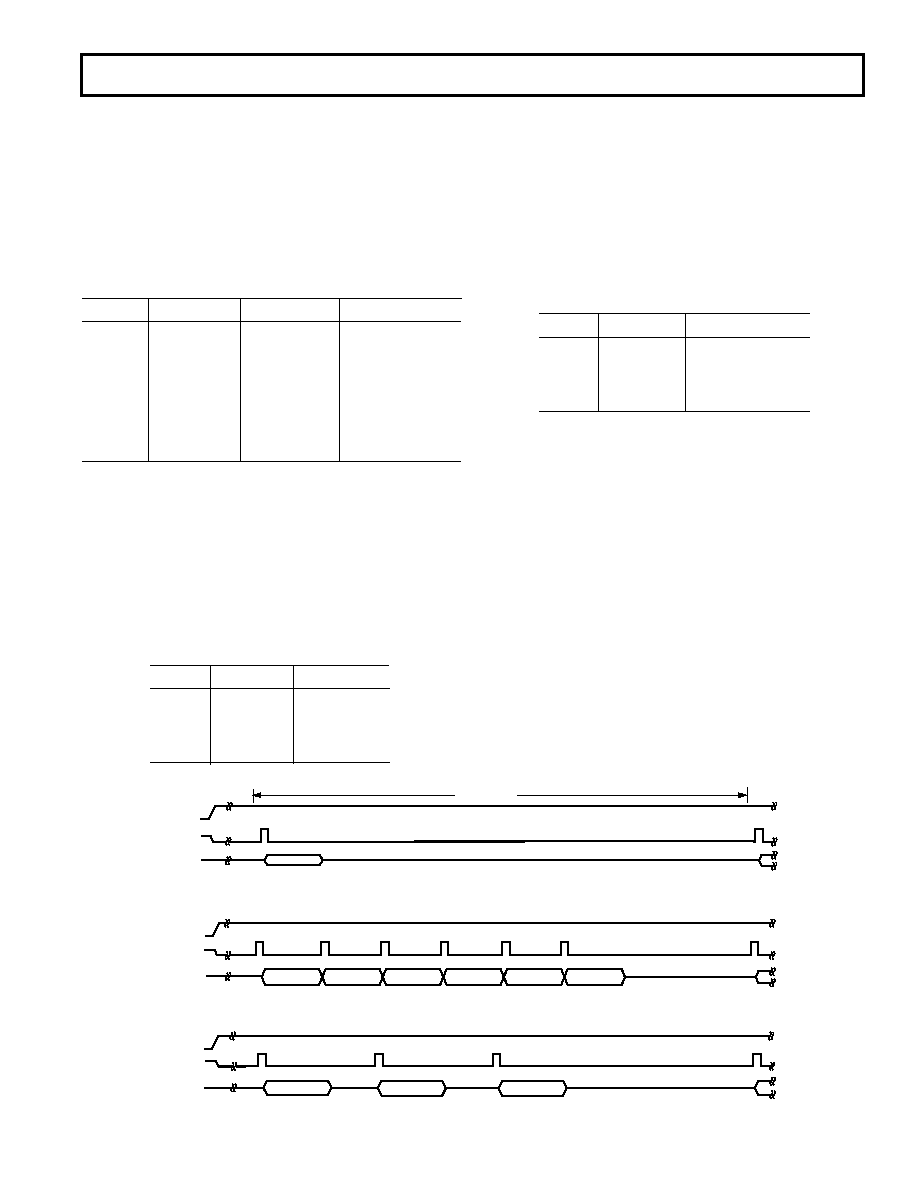

Master Clock Divider

The AD73360 features a programmable master clock divider

that allows the user to reduce an externally available master

clock, at pin MCLK, by one of the ratios 1, 2, 3, 4 or 5 to pro-

duce an internal master clock signal (DMCLK) that is used to

calculate the sampling and serial clock rates. The master clock

divider is programmable by setting CRB:4-6. Table XV shows

the division ratio corresponding to the various bit settings. The

default divider ratio is divide-by-one.

Table XV. DMCLK (Internal) Rate Divider Settings

MCD2

MCD1

MCD0

DMCLK Rate

0

MCLK

0

1

MCLK/2

0

1

0

MCLK/3

0

1

MCLK/4

1

0

MCLK/5

1

0

1

MCLK

1

0

MCLK

1

MCLK

Serial Clock Rate Divider

The AD73360 features a programmable serial clock divider that

allows users to match the serial clock (SCLK) rate of the data to

that of the DSP engine or host processor. The maximum SCLK

rate available is DMCLK and the other available rates are:

DMCLK/2, DMCLK/4 and DMCLK/8. The slowest rate

(DMCLK/8) is the default SCLK rate. The serial clock divider

is programmable by setting bits CRB:2–3. Table XVI shows the

serial clock rate corresponding to the various bit settings.

Table XVI. SCLK Rate Divider Settings

SCD1

SCD0

SCLK Rate

0

DMCLK/8

0

1

DMCLK/4

1

0

DMCLK/2

1

DMCLK

Decimation Rate Divider

The AD73360 features a programmable decimation rate divider

that allows users flexibility in matching the AD73360’s ADC

sample rates to the needs of the DSP software. The maximum

sample rate available is DMCLK/256 and the other available

rates are: DMCLK/512, DMCLK/1024 and DMCLK/2048.

The slowest rate (DMCLK/2048) is the default sample rate.

The sample rate divider is programmable by setting bits CRB:0-1.

Table XVII shows the sample rate corresponding to the various

bit settings.

Table XVII. Decimation Rate Divider Settings

DR1

DR0

Sample Rate

0

DMCLK/2048

0

1

DMCLK/1024

1

0

DMCLK/512

1

DMCLK/256

OPERATION

General Description

The AD73360 inputs and outputs data in a Time Division

Multiplexing (TDM) format. When data is being read from the

AD73360 each channel has a fixed time slot in which its data is

transmitted. If a channel is not powered up, no data is transmit-

ted during the allocated time slot and the SDO line will be

three-stated. When the AD73360 is first powered up or reset it

will be set to Program Mode and will output an SDOFS. After a

reset the SDOFS will be asserted once every sample period

(125

s assuming 16.384 MHz master clock). If the AD73360 is

configured in Frame Sync Loop-Back Mode, one control word

can be transmitted after each SDOFS pulse. Figure 10a shows

the SDO and SDOFS lines after a reset. The serial data sent by

SDO will not contain valid ADC data until the AD73360 is put

into Data Mode or Mixed Mode. Control Registers D through

F allow channels to be powered up individually. This gives

greater flexibility and control over power consumption. Figure

10b shows the SDOFS and SDO of the AD73360 when all

channels are powered up and Figure 10c shows SDOFS and

SDO with channels 1, 3 and 5 powered up.

SDOFS

SDO

SE

1/FSAMPLE

Figure 10a. Output Timing After Reset (Program Mode)

SDOFS

SDO

SE

CHANNEL 1

CHANNEL 2

CHANNEL 3

CHANNEL 4

CHANNEL 5

CHANNEL 6

Figure 10b. Output Timing: All Channels Powered Up (Data/Mixed Mode)

SDOFS

SDO

SE

CHANNEL 5

CHANNEL 1

CHANNEL 3

Figure 10c. Output Timing: Channels 1, 3 and 5 Powered Up (Data/Mixed Mode)

相关PDF资料 |

PDF描述 |

|---|---|

| MAX965EUA+ | IC COMPARATOR R-R 8-UMAX |

| MAX966ESA+ | IC COMPARATOR R-R 8-SOIC |

| VE-JN4-MY-F1 | CONVERTER MOD DC/DC 48V 50W |

| MAX965ESA+ | IC COMPARATOR R-R 8-SOIC |

| VE-JN3-MY-F4 | CONVERTER MOD DC/DC 24V 50W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD7339 | 制造商:AD 制造商全称:Analog Devices 功能描述:5 V Integrated High Speed ADC/Quad DAC System |

| AD7339BS | 制造商:Analog Devices 功能描述:Data Acquisition System Single ADC Quad DAC 8-Bit 52-Pin MQFP |

| AD7339BS-REEL | 制造商:Analog Devices 功能描述:Data Acquisition System Single ADC Quad DAC 8-Bit 52-Pin MQFP T/R |

| AD7339BSZ-REEL | 功能描述:IC ADC/QUAD DAC 5V W/REF 52-MQFP RoHS:是 类别:集成电路 (IC) >> 数据采集 - ADCs/DAC - 专用型 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:50 系列:- 类型:数据采集系统(DAS) 分辨率(位):16 b 采样率(每秒):21.94k 数据接口:MICROWIRE?,QSPI?,串行,SPI? 电压电源:模拟和数字 电源电压:1.8 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:40-WFQFN 裸露焊盘 供应商设备封装:40-TQFN-EP(6x6) 包装:托盘 |

| AD734 | 制造商:AD 制造商全称:Analog Devices 功能描述:10 MHz, 4-Quadrant Multiplier/Divider |

发布紧急采购,3分钟左右您将得到回复。