参数资料

| 型号: | AD7609BSTZ-RL |

| 厂商: | Analog Devices Inc |

| 文件页数: | 5/36页 |

| 文件大小: | 0K |

| 描述: | IC DAS W/ADC 18BIT 8CH 64LQFP |

| 标准包装: | 1,500 |

| 类型: | 数据采集系统(DAS),ADC |

| 分辨率(位): | 18 b |

| 采样率(每秒): | 200k |

| 数据接口: | DSP,MICROWIRE?,并联,QSPI?,串行,SPI? |

| 电压电源: | 模拟和数字 |

| 电源电压: | 2.3 V ~ 5 V,4.75 V ~ 5.25 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 64-LQFP |

| 供应商设备封装: | 64-LQFP(10x10) |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页当前第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页

Data Sheet

AD7609

Rev. A | Page 13 of 36

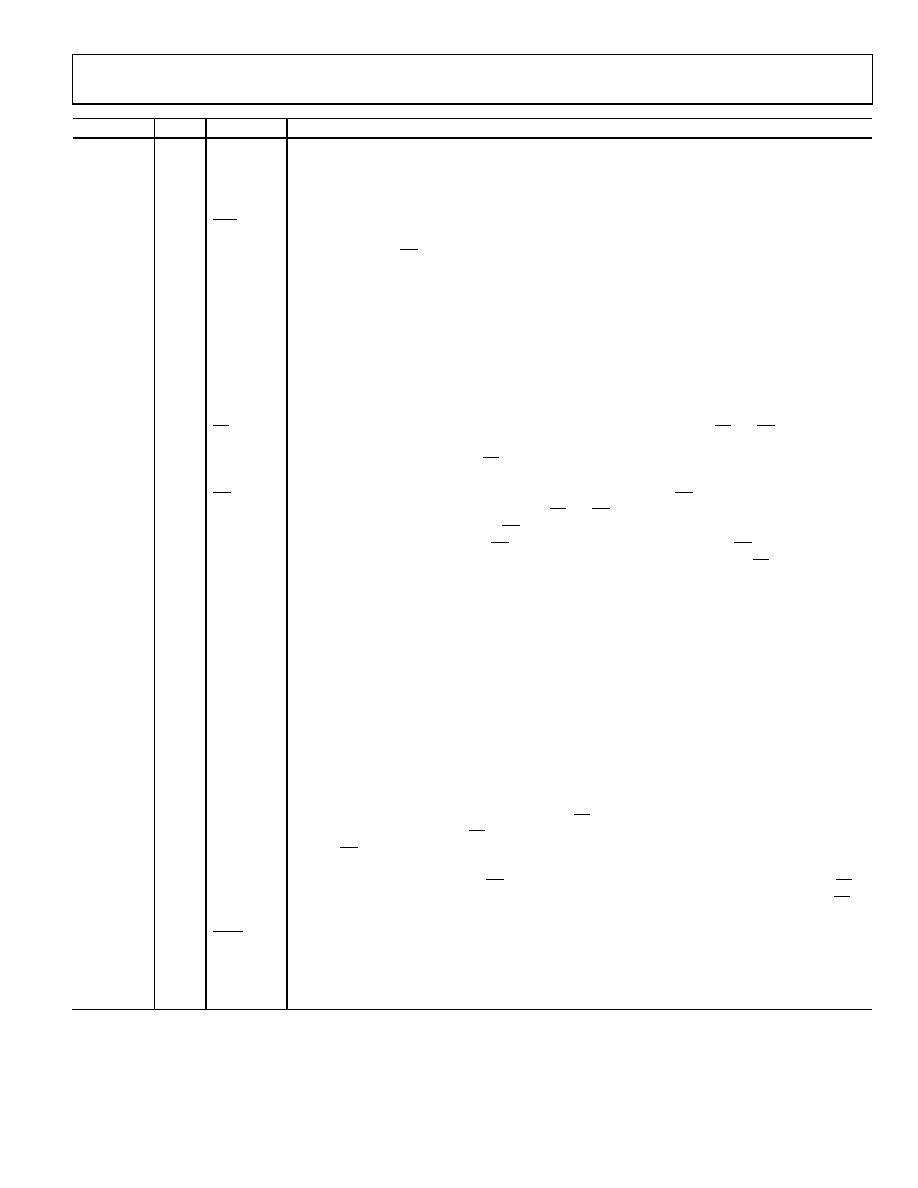

Pin No.

Type1

Mnemonic

Description

8

DI

RANGE

Analog Input Range Selection. Logic input. The polarity on this pin determines the input range of the

analog input channels. If this pin is tied to a logic high, the analog input range is ±10 V for all

channels. If this pin is tied to a logic low, the analog input range is ±5 V for all channels. A logic

change on this pin has an immediate effect on the analog input range. Changing this pin during a

conversion is not recommended. See the Analog Input section for more details.

6

DI

PAR/

SER SEL

Parallel/Serial Interface Selection Input. Logic input. If this pin is tied to a logic low, the parallel

interface is selected. If this pin is tied to a logic high, the serial interface is selected.

In serial mode, the RD/SCLK pin functions as the serial clock input. The DB7/DOUTA and DB8/DOUTB pins

function as serial data outputs.

When the serial interface is selected, the DB[15:9] and DB[6:0] pins should be tied to AGND.

9, 10

DI

CONVST A,

CONVST B

Conversion Start Input A, Conversion Start Input B. Logic inputs. These logic inputs are used to initiate

conversions on the analog input channels. For simultaneous sampling of all input channels, CONVST A

and CONVST B can be shorted together and a single conversion start signal applied. Alternatively,

CONVST A can be used to initiate simultaneous sampling for V1, V2, V3, and V4, and CONVST B can be

used to initiate simultaneous sampling on the other analog inputs (V5, V6, V7, and V8). This is only

possible when oversampling is not switched on. When the CONVST A or CONVST B pin transitions

from low to high, the front-end track-and-hold circuitry for their respective analog inputs is set to

hold. This function allows a phase delay to be created inherently between the sets of analog inputs.

13

DI

CS

Chip Select. This active low logic input frames the data transfer. When both CS and RD are logic low in

parallel mode, the output bus (DB[15:0]) is enabled and the conversion result is output on the parallel

data bus lines. In serial mode, the CS is used to frame the serial read transfer and clocks out the MSB

of the serial output data.

12

DI

RD/SCLK

Parallel Data Read Control Input When Parallel Interface is Selected (RD)/Serial Clock Input When

Serial Interface is Selected (SCLK). When both CS and RD are logic low in parallel mode, the output

bus is enabled. In parallel mode, two RD pulses are required to read the full 18 bits of conversion

results from each channel. The first RD pulse outputs DB[17:2], and the second RD pulses outputs

DB[1:0]. In serial mode, this pin acts as the serial clock input for data transfers. The CS falling edge

takes the data output lines, DOUTA and DOUTB, out of three-state and clocks out the MSB of the

conversion result. The rising edge of SCLK clocks all subsequent data bits onto the serial data

14

DO

BUSY

Busy Output. This pin transitions to a logic high after both CONVST A and CONVST B rising edges and

indicates that the conversion process has started. The BUSY output remains high until the conversion

process for all channels is complete. The falling edge of BUSY signals that the conversion data is being

latched into the output data registers and will be available to be read after a time, t4. Any data read

while BUSY is high should be complete before the falling edge of BUSY occurs. Rising edges on

CONVST A or CONVST B have no effect while the BUSY signal is high.

11

DI

RESET

Reset Input. When set to logic high, the rising edge of RESET resets the AD7609. The part must receive

a RESET pulse after power-up. To achieve the specified performance after the RESET signal, the tWAKE_UP

SHUTDOWN

time should elapse between power-on and the RESET pulse. The RESET high pulse should be

typically 100 ns wide. If a RESET pulse is applied during a conversion, the conversion is aborted. If a

RESET pulse is applied during a read, the contents of the output registers reset to all zeros.

15

DO

FRSTDATA

Digital Output. The FRSTDATA output signal indicates when the first channel, V1, is being read back

on either the parallel or serial interface. When the CS input is high, the FRSTDATA output pin is in

three-state. The falling edge of CS takes FRSTDATA out of three-state. In parallel mode, the falling

edge of RD corresponding to the result of V1 then sets the FRSTDATA pin high, indicating that the

result from V1 is available on the output data bus. The FRSTDATA output returns to a logic low

following the third falling edge of RD. In serial mode, FRSTDATA goes high on the falling edge of CS

as this clocks out the MSB of V1 on DOUTA. It returns low on the 18th SCLK falling edge after the CS

falling edge. See the Conversion Control section for more details.

7

DI

STBY

Standby Mode Input. This pin is used to place the AD7609 into one of two power-down modes:

standby mode or shutdown mode. The power-down mode entered depends on the state of the

RANGE pin, as shown in Table 8. When in standby mode, all circuitry except the on-chip reference,

regulators, and regulator buffers is powered down. When in shutdown mode, all circuitry is

powered down.

相关PDF资料 |

PDF描述 |

|---|---|

| AD760AQ | IC DAC 16BIT W/AMP SRL 28-CDIP |

| AD766AN | IC DAC 16BIT W/REF DSP 16-DIP |

| AD767BD | IC DAC 12BIT W/AMP 24-CDIP |

| AD768AR | IC DAC 16BIT 30MSPS 28-SOIC |

| AD7724ASTZ | IC MOD SIGMA-DELTA DUAL 48LQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD760AN | 制造商:未知厂家 制造商全称:未知厂家 功能描述:16-Bit Digital-to-Analog Converter |

| AD760AP | 制造商:未知厂家 制造商全称:未知厂家 功能描述:16-Bit Digital-to-Analog Converter |

| AD760AQ | 功能描述:IC DAC 16BIT W/AMP SRL 28-CDIP RoHS:否 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:DACPORT® 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:50 系列:- 设置时间:4µs 位数:12 数据接口:串行 转换器数目:2 电压电源:单电源 功率耗散(最大):- 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:8-TSSOP,8-MSOP(0.118",3.00mm 宽) 供应商设备封装:8-uMAX 包装:管件 输出数目和类型:2 电压,单极 采样率(每秒):* 产品目录页面:1398 (CN2011-ZH PDF) |

| AD760SQ | 制造商:未知厂家 制造商全称:未知厂家 功能描述:16-Bit Digital-to-Analog Converter |

| AD7610 | 制造商:AD 制造商全称:Analog Devices 功能描述:14-Bit, 1 MSPS, Differential, Programmable Input PulSAR ADC |

发布紧急采购,3分钟左右您将得到回复。