- 您现在的位置:买卖IC网 > PDF目录1982 > AD7699BCPZRL7 (Analog Devices Inc)IC ADC 8CH 16BIT 500KSPS 20LFCSP PDF资料下载

参数资料

| 型号: | AD7699BCPZRL7 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 16/28页 |

| 文件大小: | 0K |

| 描述: | IC ADC 8CH 16BIT 500KSPS 20LFCSP |

| 标准包装: | 1,500 |

| 位数: | 16 |

| 采样率(每秒): | 500k |

| 数据接口: | DSP,MICROWIRE?,QSPI?,串行,SPI? |

| 转换器数目: | 1 |

| 功率耗散(最大): | 32mW |

| 电压电源: | 模拟和数字 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 20-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 20-LFCSP-VQ |

| 包装: | 带卷 (TR) |

| 输入数目和类型: | 8 个单端,单极;4 个差分,单极;4 个差分,双极;4 个伪差分,双极 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页当前第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页

Data Sheet

AD7699

Rev.

| Page 23 of 28

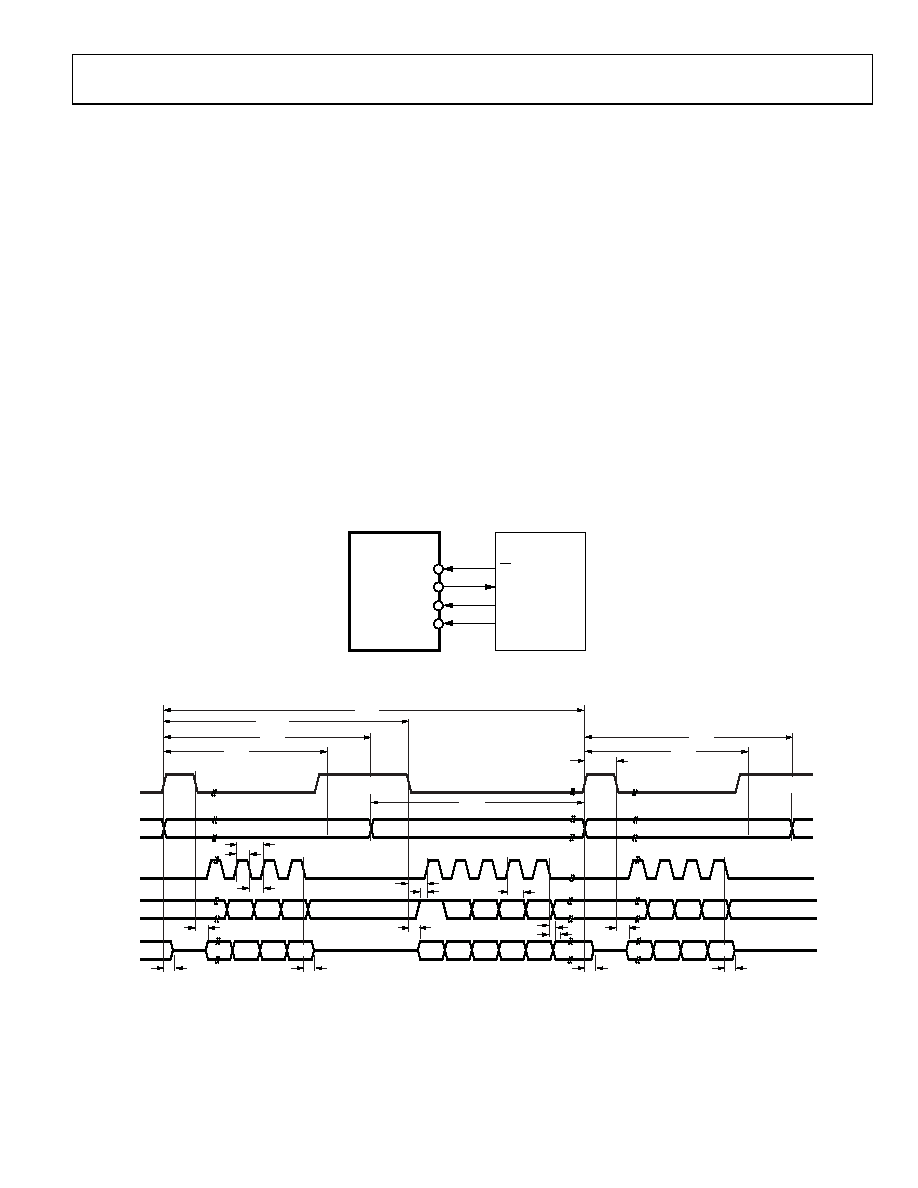

READ/WRITE SPANNING CONVERSION WITHOUT

A BUSY INDICATOR

This mode is used when the AD7699 is connected to any host

using an SPI, serial port, or FPGA. The connection diagram is

shown in Figure 36, and the corresponding timing is given in

Figure 37. For SPI, the host should use CPHA = CPOL = 0.

Reading/writing spanning conversion is shown, which covers

all three modes detailed in the Digital Interface section. For this

mode, the host must generate the data transfer based on the

conversion time. For an interrupt driven transfer, refer to the

next section, which uses a busy indicator.

A rising edge on CNV initiates a conversion, forces SDO to

high impedance, and ignores data present on DIN. After a

conversion is initiated, it continues until completion irrespective

of the state of CNV. CNV must be returned high before the safe

data transfer time, tDATA, and then held high beyond the conver-

sion time, tCONV, to avoid generation of the busy signal indicator.

After the conversion is complete, the AD7699 enters the acquisi-

tion phase and powers down. When the host brings CNV low

after tCONV (max), the MSB is enabled on SDO. The host also

must enable the MSB of CFG at this time (if necessary) to begin

the CFG update. While CNV is low, both a CFG update and a

data readback take place. The first 14 SCK rising edges are used

to update the CFG, and the first 15 SCK falling edges clock out

the conversion results starting with MSB 1. The restriction

for both configuring and reading is that they both must occur

before the tDATA time of the next conversion elapses. All 14 bits

of CFG[13:0] must be written, or they are ignored. In addition,

if the 16-bit conversion result is not read back before tDATA elapses,

it is lost.

The SDO data is valid on both SCK edges. Although the rising

edge can be used to capture the data, a digital host using the

SCK falling edge allows a faster reading rate, provided it has an

acceptable hold time. After the 16th (or 30th) SCK falling edge, or

when CNV goes high (whichever occurs first), SDO returns to

high impedance.

If CFG readback is enabled, the CFG associated with the conver-

sion result is read back MSB first following the LSB of the

conversion result. A total of 30 SCK falling edges is required to

return SDO to high impedance if this is enabled.

MISO

MOSI

SCK

SS

CNV

FOR SPI USE CPHA = 0, CPOL = 0.

SCK

SDO

DIN

AD7699

DIGITAL HOST

07

35

4-

03

4

Figure 36. Connection Diagram for the AD7699 Without a Busy Indicator

UPDATE (n)

CFG/SDO

UPDATE (n + 1)

CFG/SDO

ACQUISITION (n)

ACQUISITION

(n + 1)

ACQUISITION

(n – 1)

MSB MSB – 1

1

2

BEGIN DATA (n – 1)

BEGIN CFG (n + 1)

CFG

MSB

CFG

MSB – 1

LSB + 1

14

15

SEE NOTE

NOTES

1. THE LSB IS FOR CONVERSION RESULTS OR THE CONFIGURATION REGISTER CFG (n – 1) IF.

15 SCK FALLING EDGES = LSB OF CONVERSION RESULTS.

29 SCK FALLING EDGES = LSB OF CONFIGURATION REGISTER.

ON THE 16TH OR 30TH SCK FALLING EDGE, SDO IS DRIVEN TO HIGH IMPENDANCE.

16/

30

CONVERSION (n)

RETURN CNV HIGH

FOR NO BUSY

END DATA (n – 1)

END CFG (n + 1)

CFG

LSB

X

>

tCONV

LSB

SCK

CNV

DIN

SDO

LSB + 1

14

15

16/

30

CONVERSION (n – 1)

RETURN CNV HIGH

FOR NO BUSY

END DATA (n – 2)

END CFG (n)

CFG

LSB

X

tCONV

tDATA

tCNVH

tDATA

tDIS

tEN

tDSDO

tHSDO

tHDIN

tSDIN

tCLSCK

tEN

tSCK

tSCKH

tSCKL

tDIS

tCONV

LSB

07

35

4-

03

5

tACQ

tCYC

(QUIET

TIME)

(QUIET

TIME)

Figure 37. Serial Interface Timing for the AD7699 Without a Busy Indicator

B

相关PDF资料 |

PDF描述 |

|---|---|

| AD7701BN | IC ADC 16BIT LC2MOS MONO 20-DIP |

| AD7703BN | IC ADC 20BIT LC2MOS 20-DIP |

| AD7706BN | IC ADC 16BIT 3CH 16-DIP |

| AD7707BRU | IC ADC 16BIT 3CH 20-TSSOP |

| AD7709ARU | IC ADC 16BIT SIGMA-DELTA 24TSSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD7701 | 制造商:AD 制造商全称:Analog Devices 功能描述:LC2MOS 16-Bit A/D Converter |

| AD7701AN | 功能描述:IC ADC 16BIT LC2MOS 20-DIP RoHS:否 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1 系列:- 位数:14 采样率(每秒):83k 数据接口:串行,并联 转换器数目:1 功率耗散(最大):95mW 电压电源:双 ± 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:28-DIP(0.600",15.24mm) 供应商设备封装:28-PDIP 包装:管件 输入数目和类型:1 个单端,双极 |

| AD7701ANZ | 功能描述:IC ADC 16BIT LC2MOS 20-DIP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1 系列:microPOWER™ 位数:8 采样率(每秒):1M 数据接口:串行,SPI? 转换器数目:1 功率耗散(最大):- 电压电源:模拟和数字 工作温度:-40°C ~ 125°C 安装类型:表面贴装 封装/外壳:24-VFQFN 裸露焊盘 供应商设备封装:24-VQFN 裸露焊盘(4x4) 包装:Digi-Reel® 输入数目和类型:8 个单端,单极 产品目录页面:892 (CN2011-ZH PDF) 其它名称:296-25851-6 |

| AD7701AQ | 制造商:AD 制造商全称:Analog Devices 功能描述:LC2MOS 16-Bit A/D Converter |

| AD7701AR | 功能描述:IC ADC 16BIT LC2MOS 20-SOIC RoHS:否 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1 系列:- 位数:14 采样率(每秒):83k 数据接口:串行,并联 转换器数目:1 功率耗散(最大):95mW 电压电源:双 ± 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:28-DIP(0.600",15.24mm) 供应商设备封装:28-PDIP 包装:管件 输入数目和类型:1 个单端,双极 |

发布紧急采购,3分钟左右您将得到回复。