- 您现在的位置:买卖IC网 > PDF目录1983 > AD7764BRUZ-REEL7 (Analog Devices Inc)IC ADC 24BIT S/D 312KSPS 28TSSOP PDF资料下载

参数资料

| 型号: | AD7764BRUZ-REEL7 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 20/33页 |

| 文件大小: | 0K |

| 描述: | IC ADC 24BIT S/D 312KSPS 28TSSOP |

| 标准包装: | 1,000 |

| 位数: | 24 |

| 采样率(每秒): | 312k |

| 数据接口: | 串行,SPI? |

| 转换器数目: | 1 |

| 功率耗散(最大): | 371mW |

| 电压电源: | 模拟和数字 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 28-TSSOP(0.173",4.40mm 宽) |

| 供应商设备封装: | 28-TSSOP |

| 包装: | 带卷 (TR) |

| 输入数目和类型: | 1 个差分,单极;1 个差分,双极 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页当前第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页

AD7764

Rev. A | Page 26 of 32

CLOCKING THE AD7764

The AD7764 requires an external low jitter clock source. This

signal is applied to the MCLK pin. An internal clock signal

(ICLK) is derived from the MCLK input signal. The ICLK

controls the internal operation of the AD7764. The maximum

ICLK frequency is 20 MHz. To generate the ICLK,

ICLK = MCLK/2

For output data rates equal to those used in audio systems, a

12.288 MHz ICLK frequency can be used. As shown in Table 6,

output data rates of 96 kHz and 48 kHz are achievable with this

ICLK frequency.

MCLK JITTER REQUIREMENTS

The MCLK jitter requirements depend on a number of factors

and are given by

20

)

(

10

2

)

(

dB

SNR

f

OSR

t

IN

rms

j

×

π

×

=

where:

OSR = oversampling ratio = fICLK/ODR.

fIN = maximum input frequency.

SNR(dB) = target SNR.

Example 1

This example can be taken from Table 6, where:

ODR = 312.5 kHz.

fICLK = 20 MHz.

fIN (max) = 156.25 kHz.

SNR = 104 dB.

ps

t

rms

j

41

.

51

10

25

.

156

2

64

2

.

5

3

)

(

=

×

π

×

=

This is the maximum allowable clock jitter for a full-scale,

156.25 kHz input tone with the given ICLK and output

data rate.

Example 2

This second example can also be taken from Table 6, where:

ODR = 48 kHz.

fICLK = 12.288 MHz.

fIN (max) = 19.2 kHz.

SNR = 109 dB.

ps

470

10

2

.

19

2

256

45

.

5

3

)

(

=

×

π

×

=

rms

j

t

The input amplitude also has an effect on these jitter figures.

For example, if the input level is 3 dB below full scale, the allow-

able jitter is increased by a factor of √2, increasing the first

example to 144.65 ps rms. This happens when the maximum

slew rate is decreased by a reduction in amplitude.

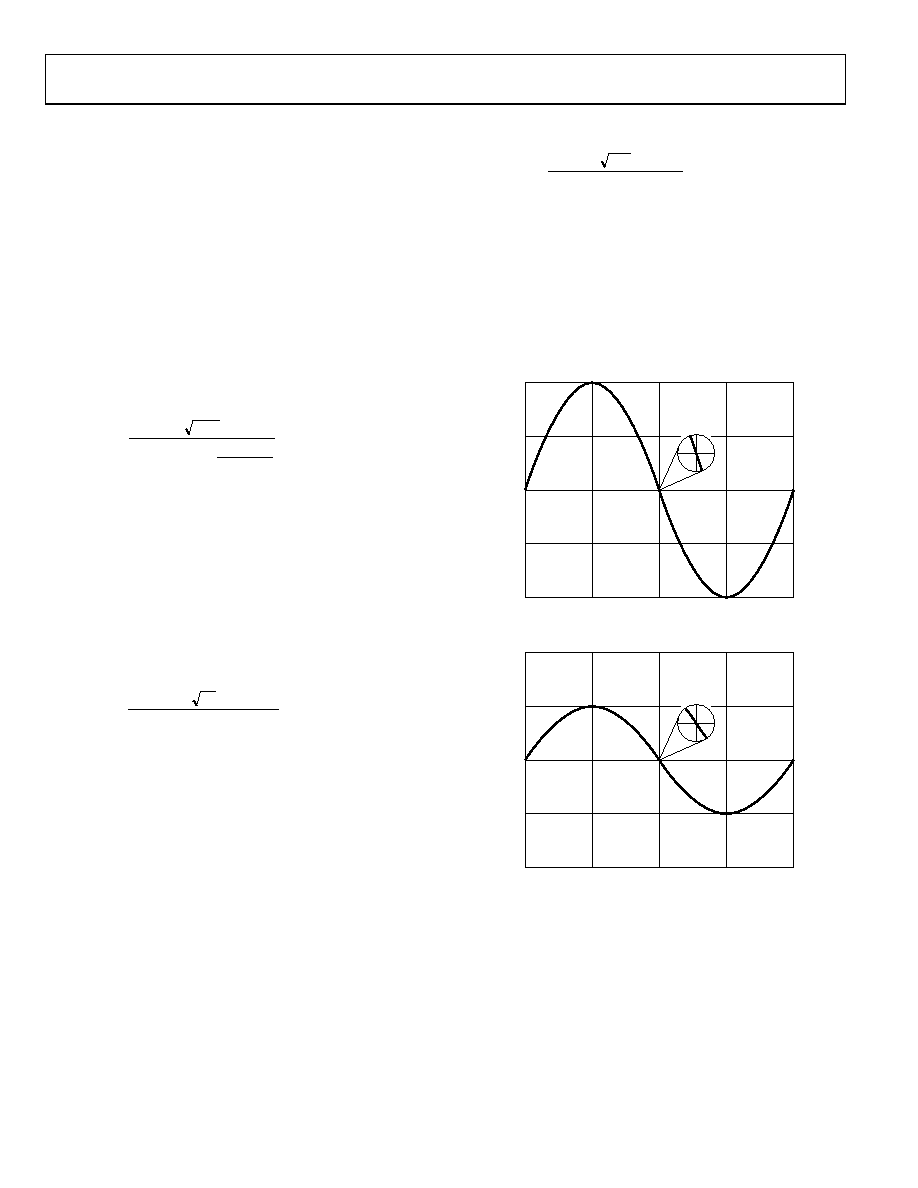

Figure 49 and Figure 50 illustrate this point, showing the

maximum slew rate of a sine wave of the same frequency but

with different amplitudes.

1.0

–1.0

0.5

0

–0.5

06518-

022

Figure 49. Maximum Slew Rate of a Sine Wave

with an Amplitude of 2 V p-p

1.0

–1.0

0.5

0

–0.5

06518-

023

Figure 50. Maximum Slew Rate of the Same Frequency Sine Wave

as in Figure 49 with an Amplitude of 1 V p-p

相关PDF资料 |

PDF描述 |

|---|---|

| AD7765BRUZ-REEL7 | IC ADC 24BIT S/D 156KSPS 28TSSOP |

| AD7766BRUZ-RL7 | IC ADC 24BIT 128KSPS SAR 16TSSOP |

| AD7767BRUZ-RL7 | ADC 24BIT 15MW 128KSPS 16TSSOP |

| AD7776ARZ | IC ADC 10BIT 1CHAN HS 24SOIC |

| AD7780BRZ-REEL | IC ADC 24BIT 1CH LP SD 14SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD7765 | 制造商:AD 制造商全称:Analog Devices 功能描述:24-Bit, 8.5 mW, 109 dB, 128/64/32 kSPS ADCs |

| AD7765_07 | 制造商:AD 制造商全称:Analog Devices 功能描述:24-Bit, 156 kSPS, 112 dB ヒ-ツ ADC with On-Chip Buffers and Serial Interface |

| AD7765BRUZ | 功能描述:IC ADC 24BIT S/D 156KSPS 28TSSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 其它有关文件:TSA1204 View All Specifications 标准包装:1 系列:- 位数:12 采样率(每秒):20M 数据接口:并联 转换器数目:2 功率耗散(最大):155mW 电压电源:模拟和数字 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-TQFP 供应商设备封装:48-TQFP(7x7) 包装:Digi-Reel® 输入数目和类型:4 个单端,单极;2 个差分,单极 产品目录页面:1156 (CN2011-ZH PDF) 其它名称:497-5435-6 |

| AD7765BRUZ-REEL7 | 功能描述:IC ADC 24BIT S/D 156KSPS 28TSSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1,000 系列:- 位数:12 采样率(每秒):300k 数据接口:并联 转换器数目:1 功率耗散(最大):75mW 电压电源:单电源 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:24-SOIC(0.295",7.50mm 宽) 供应商设备封装:24-SOIC 包装:带卷 (TR) 输入数目和类型:1 个单端,单极;1 个单端,双极 |

| AD7766 | 制造商:AD 制造商全称:Analog Devices 功能描述:24-Bit, 8.5 mW, 109 dB, 128/64/32 kSPS ADCs |

发布紧急采购,3分钟左右您将得到回复。