- 您现在的位置:买卖IC网 > PDF目录9712 > AD7877ACPZ-REEL (Analog Devices Inc)IC ADC 12BIT TOUCHSCREEN 32LFCSP PDF资料下载

参数资料

| 型号: | AD7877ACPZ-REEL |

| 厂商: | Analog Devices Inc |

| 文件页数: | 16/45页 |

| 文件大小: | 0K |

| 描述: | IC ADC 12BIT TOUCHSCREEN 32LFCSP |

| 标准包装: | 5,000 |

| 类型: | 电阻 |

| 触摸面板接口: | 4 线 |

| 输入数/键: | 1 TSC |

| 分辨率(位): | 12 b |

| 评估套件: | 可供 |

| 数据接口: | 串行,SPI? |

| 数据速率/采样率 (SPS,BPS): | 125k |

| 电压基准: | 外部,内部 |

| 电源电压: | 2.7 V ~ 5.25 V |

| 电流 - 电源: | 1µA |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 32-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 32-LFCSP-VQ |

| 包装: | 带卷 (TR) |

| 配用: | EVAL-AD7877EBZ-ND - BOARD EVALUATION FOR AD7877 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页当前第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页

AD7877

Data Sheet

Rev. D | Page 22 of 44

STOPACQ Polarity (Control Register 2, Bit[3])

This bit should be set according to the polarity of the signal

applied to the STOPACQ pin. If that signal is active high, that

is, no acquisitions should occur during the high period of the

signal, then the POL bit should be set to 1. If the signal is active

low, then the POL bit should be 0. The default value for POL is 0.

First Conversion Delay (Control Register 2, Bits[5:4])

The first conversion delay (FCD) bits in Control Register 2

program a delay of 500 ns (default), 128 s, 1.024 ms, or 8.19 ms

before the first conversion, to allow the ADC time to power up.

This delay also occurs before conversion of the X and Y coordi-

nate channels, to allow extra time for screen settling, and after

the last conversion in a sequence, to precharge PENIRQ. If the

signal on the STOPACQ pin is being monitored and goes active

during the FCD, it is ignored until after the FCD period.

Table 8. First Conversion Delay Selection

FCD1

FCD

Function

0

1 clock delay (500 ns)

0

1

256 clock delays (128 s)

1

0

2048 clock delays (1.024 ms)

1

16,384 clock delays (8.19 ms)

Power Management (Control Register 2, Bits[7:6])

The power management (PM) bits in Control Register 2 allow

the power management features of the ADC to be programmed.

If the PM bits are 00, the ADC is powered down permanently.

This overrides any setting of the mode bits in Control Register 1.

If the PM bits are 01, the ADC and the reference both power

down when the ADC is not converting. If the PM bits are 10,

the ADC and reference are powered up continuously. If the PM

bits are 11, the ADC, but not the reference, powers down when

the ADC is not converting. If the AD7879 is in full power mode

(PM=10), the master sequencer should not be used. PM bits

must be set to 01 or 11 when using the master sequencer.

Table 9. Power Management Selection

PM1

PM0

Function

0

Power down continuously (default)

0

1

Power down ADC and reference when

ADC is not converting (powers up with

FCD at start of a conversion)

1

0

Powered up continuously

1

Power down ADC when ADC is not

converting (powers up with FCD at start

of conversion)

Acquisition Time (Control Register 2, Bits[9:8])

The ACQ bits in Control Register 2 allow the selection of

acquisition times for the ADC of 2 s (default), 4 s, 8 s, or

16 s. The user can program the ADC with an acquisition time

suitable for the type of signal being sampled. For example,

signals with large RC time constants can require longer

acquisition times.

Table 10. Acquisition Time Selection

ACQ1

ACQ0

Function

0

4 clock periods (2 s)

0

1

8 clock periods (4 s)

1

0

16 clock periods (8 s)

1

32 clock periods (16 s)

Averaging (Control Register 2, Bits[11:10])

Signals from touch screens can be extremely noisy. The AVG

bits in Control Register 2 allow multiple conversions to be

performed on each input channel and averaged to reduce noise.

A single conversion can be selected (no averaging), which is the

default, or 4, 8, or 16 conversions can be averaged. Only the

final averaged result is written into the results register.

Table 11. Averaging Selection

AVG1

AVG0

Function

0

ADC performs 1 average per channel

0

1

ADC performs 4 averages per channel

1

0

ADC performs 8 averages per channel

1

ADC performs 16 averages per channel

SEQUENCER REGISTERS

There are two sequencer registers on the AD7877. Sequencer

Register 0 controls the measurements performed during a slave

mode sequence. Sequencer Register 1 controls the measure-

ments performed during a master mode sequence.

To include a measurement in a slave mode or master mode

sequence, the relevant bit must be set in Sequencer Register 0 or

Sequencer Register 1. Setting Bit 11 includes a measurement on

ADC Channel 0 in the sequence, which is the Y positional

measurement. Setting Bit 10 includes a measurement on ADC

Channel 1 (X+ measurement), and so on, through Bit 1 for

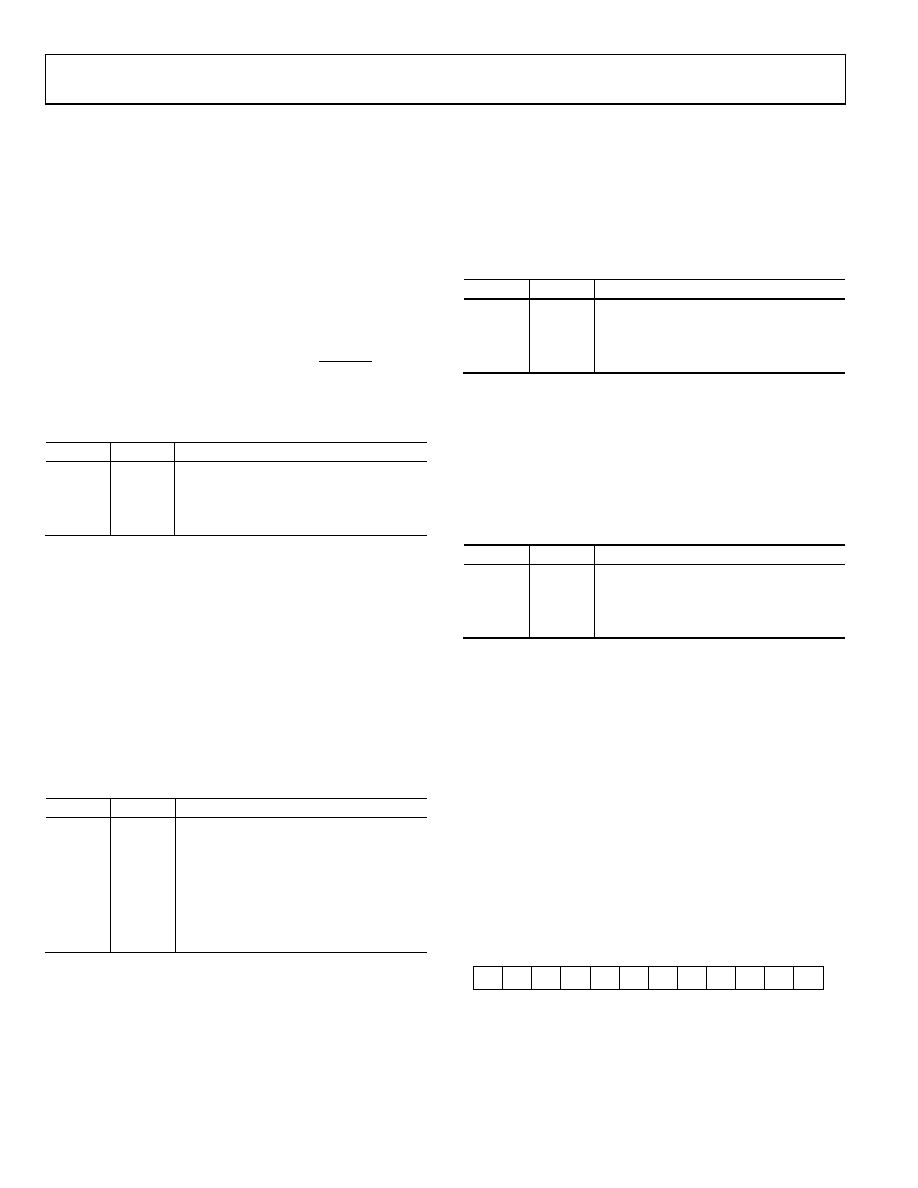

Channel 10. Figure 37 illustrates the correspondence between

the bits in the sequencer registers and the various measure-

ments. Bit 0 in both sequencer registers is not used. See also the

Detailed Register Descriptions section.

03796-015

Y+

X+

Z2

AUX

1

AUX

2

AUX

3

BAT

1

BAT

2

TEMP

1

TEMP

2

Z1

NOT

USED

11

0

Figure 37. Sequencer Register

相关PDF资料 |

PDF描述 |

|---|---|

| MS3106R32-17PX | CONN PLUG 4POS STRAIGHT W/PINS |

| MS3122E14-5SW | CONN RCPT 5POS BOX MNT W/SCKT |

| MS3126F20-41PY | CONN PLUG 41POS STRAIGHT W/PINS |

| M83723/82W803N | CONN RCPT 3POS WALL MT W/SCKT |

| MS3126F20-41PX | CONN PLUG 41POS STRAIGHT W/PINS |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD7877ACPZ-REEL7 | 功能描述:IC ADC 12BIT TOUCHSCREEN 32LFCSP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 触摸屏控制器 系列:- 标准包装:96 系列:- 类型:- 触摸面板接口:- 输入数/键:- 分辨率(位):- 评估套件:* 数据接口:- 数据速率/采样率 (SPS,BPS):- 电压基准:- 电源电压:- 电流 - 电源:- 工作温度:- 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:带卷 (TR) |

| AD7877WACPZ-REEL7 | 功能描述:IC CTRLR TOUCH SCREEN 32LFCSP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 触摸屏控制器 系列:- 标准包装:96 系列:- 类型:- 触摸面板接口:- 输入数/键:- 分辨率(位):- 评估套件:* 数据接口:- 数据速率/采样率 (SPS,BPS):- 电压基准:- 电源电压:- 电流 - 电源:- 工作温度:- 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:带卷 (TR) |

| AD7878 | 制造商:AD 制造商全称:Analog Devices 功能描述:LC2MOS Complete 12-Bit 100 kHz Sampling ADC with DSP Interface |

| AD7878AQ | 制造商:Rochester Electronics LLC 功能描述:COMPLETE 12 BIT ADC IC - Bulk |

| AD7878BQ | 功能描述:IC ADC 12BIT W/DSP INT 28-CDIP RoHS:否 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:250 系列:- 位数:12 采样率(每秒):1.8M 数据接口:并联 转换器数目:1 功率耗散(最大):1.82W 电压电源:模拟和数字 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-LQFP 供应商设备封装:48-LQFP(7x7) 包装:管件 输入数目和类型:2 个单端,单极 |

发布紧急采购,3分钟左右您将得到回复。