- 您现在的位置:买卖IC网 > PDF目录10664 > AD7894BRZ-10 (Analog Devices Inc)IC ADC 14BIT SRL T/H LP 8-SOIC PDF资料下载

参数资料

| 型号: | AD7894BRZ-10 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 11/12页 |

| 文件大小: | 0K |

| 描述: | IC ADC 14BIT SRL T/H LP 8-SOIC |

| 标准包装: | 1 |

| 位数: | 14 |

| 采样率(每秒): | 200k |

| 数据接口: | 串行 |

| 转换器数目: | 1 |

| 功率耗散(最大): | 27.5mW |

| 电压电源: | 单电源 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 8-SOIC(0.154",3.90mm 宽) |

| 供应商设备封装: | 8-SOIC |

| 包装: | 管件 |

| 输入数目和类型: | 1 个单端,双极 |

| 产品目录页面: | 779 (CN2011-ZH PDF) |

AD7894

–8–

REV. 0

250ns MIN

BUSY

SCLK

CONVST

CONVERSION

IS INITIATED;

TRACK/HOLD

GOES INTO

HOLD

CONVERSION

ENDS

10 s LATER

SERIAL READ

OPERATION

READ OPERATION

SHOULD END 250ns

PRIOR TO NEXT

RISING EDGE OF

CONVST

OUTPUT

SERIAL SHIFT

REGISTER

IS RESET

tCONVERT = 10 s

PART

WAKES

UP

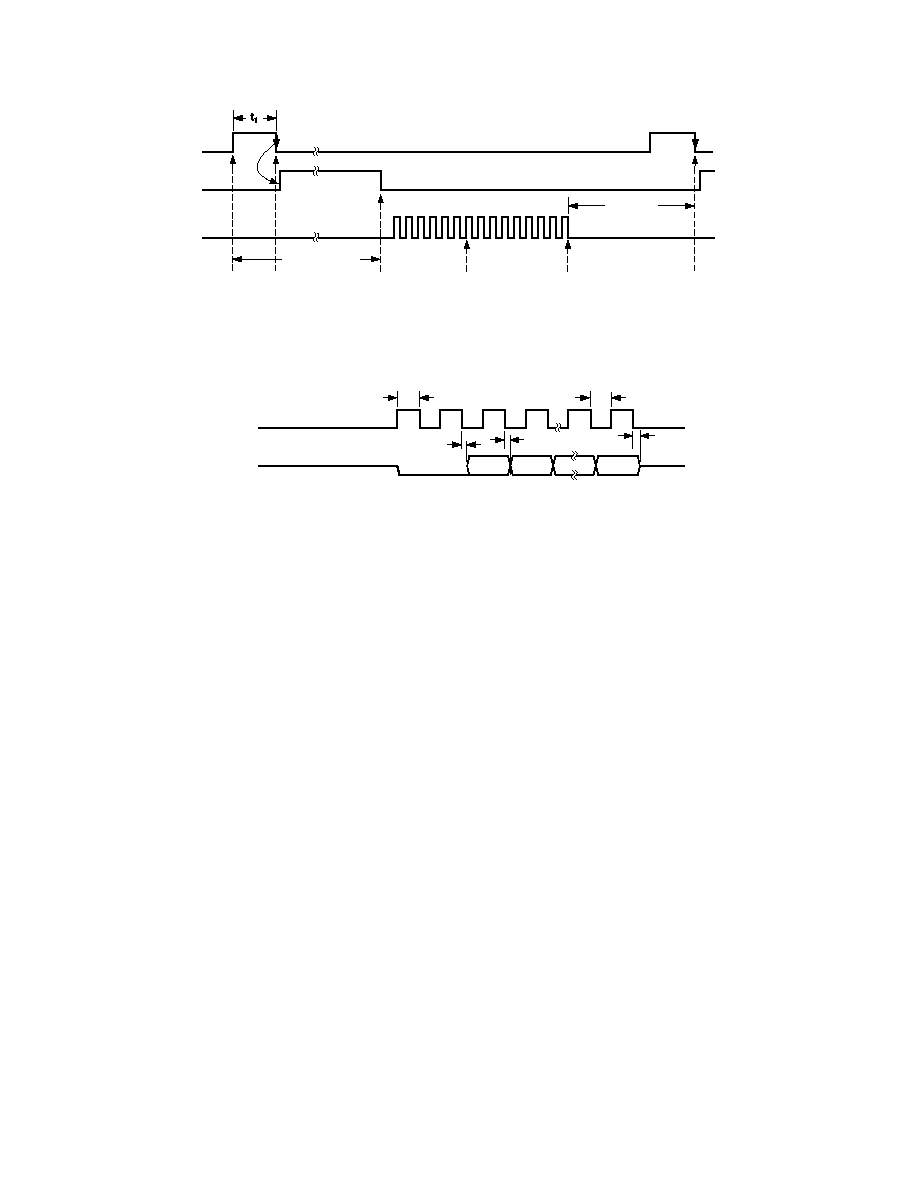

Figure 4. Mode 2 Timing Diagram Where Automatic Sleep Function is Initiated

t2

t3

t4

t5

t6

2 LEADING

ZEROS

THREE-STATE

THREE-

STATE

1

2

3

4

15

16

DB13

DB12

DB0

SCLK (I/P)

DOUT (O/P)

t2 = t3 = 31.25ns MIN, t4 = 60ns MAX, t5 = 10ns MIN, t6 = 20ns MAX @ 5V, A, B, VERSIONS

Figure 5. Data Read Operation

Mode 2 Operation (Auto Sleep After Conversion)

The timing diagram in Figure 4 is for optimum performance in

operating Mode 2, where the part automatically goes into sleep

mode once BUSY goes low, after conversion and “wakes up”

before the next conversion takes place. This is achieved by keep-

ing

CONVST low at the end of conversion, whereas it was high

at the end of conversion for Mode 1 Operation. The rising edge

of

CONVST “wakes up” the AD7894. This wake-up time is

typically 5

s and is controlled internally by a monostable cir-

cuit. While the AD7894 is waking up there is some digital activ-

ity internal to the part. If the falling edge of

CONVST (putting

the track/hold amplifier into hold mode) should occur during

this digital activity, noise will be injected into the track/hold

amplifier resulting in a poor conversion. For optimum results

the

CONVST pulse should be between 40 ns and 2

s or greater

than 6

s in width. The narrower pulse will allow a system to

instruct the AD7894 to begin waking up and perform a conver-

sion when ready, whereas the pulse greater than 6

s will give

control over when the sampling instant takes place. Note that

the 10

s wake-up time shown in Figure 4 is for a CONVST pulse

less than 2

s. If a CONVST pulse greater than 6 s is used, the

conversion will not complete for a further 5

s after the falling edge

of

CONVST. Even though the part is in sleep mode, data can still

be read from it. The read operation consists of 16 clock cycles as in

Mode 1 Operation. For the fastest serial clock of 16 MHz, the read

operation will take 1.0

s and this must be complete at least 250 ns

before the falling edge of the next

CONVST, to allow the track/

hold amplifier to have enough time to settle. This mode is very

useful when the part is converting at a slow rate, as the power

consumption will be significantly reduced from that of Mode 1

Operation.

Serial Interface

The serial interface to the AD7894 consists of just three wires, a

serial clock input (SCLK) and the serial data output (SDATA)

and a conversion status output (BUSY). This allows for an

easy-to-use interface to most microcontrollers, DSP processors

and shift registers.

Figure 5 shows the timing diagram for the read operation to the

AD7894. The serial clock input (SCLK) provides the clock

source for the serial interface. Serial data is clocked out from

the SDATA line on the falling edge of this clock and is valid on

both the rising and falling edges of SCLK. The advantage of

having the data valid on both the rising and falling edges of the

SCLK is to give the user greater flexibility in interfacing to the

part and so a wider range of microprocessor and microcontrol-

ler interfaces can be accommodated. This also explains the two

timing figures, t4 and t5, that are quoted on the diagram. The

time t4 specifies how long after the falling edge of the SCLK the

next data bit becomes valid, whereas the time t5 specifies for

how long after the falling edge of the SCLK the current data bit

is valid. The first leading zero is clocked out on the first rising

edge of SCLK. Note that the first zero will be valid on the first

falling edge of SCLK even though the data access time is speci-

fied at 60 ns for the other bits. The reason for this is that the

first bit will be clocked out faster than the other bits is due to

the internal architecture of the part. Sixteen clock pulses must

be provided to the part to access to full conversion result. The

AD7894 provides two leading zeros followed by the 14-bit

conversion result starting with the MSB (DB13). The last data

bit to be clocked out on the penultimate falling clock edge is the

LSB (DB0). On the 16th falling edge of SCLK the LSB (DB0)

will be valid for a specified time to allow the bit to be read on

the falling edge of the SCLK and then the SDATA line is dis-

abled (three-stated). After this last bit has been clocked out,

the SCLK input should return low and remain low until the

next serial data read operation. If there are extra clock pulses

after the 16th clock, the AD7894 will start over again with

outputting data from its output register and the data bus will

no longer be three-stated even when the clock stops. Provided

the serial clock has stopped before the next falling edge of

相关PDF资料 |

PDF描述 |

|---|---|

| LMX393HAUA+T | IC COMPARATOR GP DUAL 8-UMAX |

| VI-B13-MX-F1 | CONVERTER MOD DC/DC 24V 75W |

| AD9214BRSZ-105 | IC ADC 10BIT 105MSPS 28-SSOP |

| AD7980BCPZ-RL7 | IC ADC 16BIT 1MSPS SAR 10LFCSP |

| VE-J1N-MW-F4 | CONVERTER MOD DC/DC 18.5V 100W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD7894BRZ-10REEL | 功能描述:IC ADC 14BIT SRL T/H LP 8SOIC RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1,000 系列:- 位数:12 采样率(每秒):300k 数据接口:并联 转换器数目:1 功率耗散(最大):75mW 电压电源:单电源 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:24-SOIC(0.295",7.50mm 宽) 供应商设备封装:24-SOIC 包装:带卷 (TR) 输入数目和类型:1 个单端,单极;1 个单端,双极 |

| AD7894BRZ-10REEL7 | 功能描述:IC ADC 14BIT SRL T/H LP 8SOIC RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1,000 系列:- 位数:12 采样率(每秒):300k 数据接口:并联 转换器数目:1 功率耗散(最大):75mW 电压电源:单电源 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:24-SOIC(0.295",7.50mm 宽) 供应商设备封装:24-SOIC 包装:带卷 (TR) 输入数目和类型:1 个单端,单极;1 个单端,双极 |

| AD7894BRZ-3 | 功能描述:IC ADC 14BIT SRL T/H LP 8SOIC RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 其它有关文件:TSA1204 View All Specifications 标准包装:1 系列:- 位数:12 采样率(每秒):20M 数据接口:并联 转换器数目:2 功率耗散(最大):155mW 电压电源:模拟和数字 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-TQFP 供应商设备封装:48-TQFP(7x7) 包装:Digi-Reel® 输入数目和类型:4 个单端,单极;2 个差分,单极 产品目录页面:1156 (CN2011-ZH PDF) 其它名称:497-5435-6 |

| AD7895ACHIPS-10 | 功能描述:12 Bit Analog to Digital Converter 1 Input 1 SAR Die 制造商:analog devices inc. 系列:- 包装:托盘 - 晶粒 零件状态:上次购买时间 位数:12 采样率(每秒):192k 输入数:1 输入类型:单端 数据接口:SPI 配置:S/H-ADC 无线电 - S/H:ADC:1:1 A/D 转换器数:1 架构:SAR 参考类型:外部 电压 - 电源,模拟:5V 电压 - 电源,数字:5V 特性:- 工作温度:-40°C ~ 85°C 封装/外壳:模具 供应商器件封装:模具 标准包装:1 |

| AD7895AN-10 | 制造商:Analog Devices 功能描述:ADC Single SAR 192ksps 12-bit Serial 8-Pin PDIP 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Analog Devices 功能描述:IC 12-BIT ADC |

发布紧急采购,3分钟左右您将得到回复。