- 您现在的位置:买卖IC网 > PDF目录10245 > AD9204BCPZRL7-65 (Analog Devices Inc)IC ADC 10BIT 65MSPS 64LFCSP PDF资料下载

参数资料

| 型号: | AD9204BCPZRL7-65 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 16/36页 |

| 文件大小: | 0K |

| 描述: | IC ADC 10BIT 65MSPS 64LFCSP |

| 标准包装: | 750 |

| 位数: | 10 |

| 采样率(每秒): | 65M |

| 数据接口: | 串行,SPI? |

| 转换器数目: | 2 |

| 功率耗散(最大): | 128.5mW |

| 电压电源: | 模拟和数字 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 64-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 64-LFCSP-VQ(9x9) |

| 包装: | 带卷 (TR) |

| 输入数目和类型: | 4 个单端,单极;2 个差分,单极 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页当前第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页

AD9204

Rev. 0 | Page 23 of 36

External Reference Operation

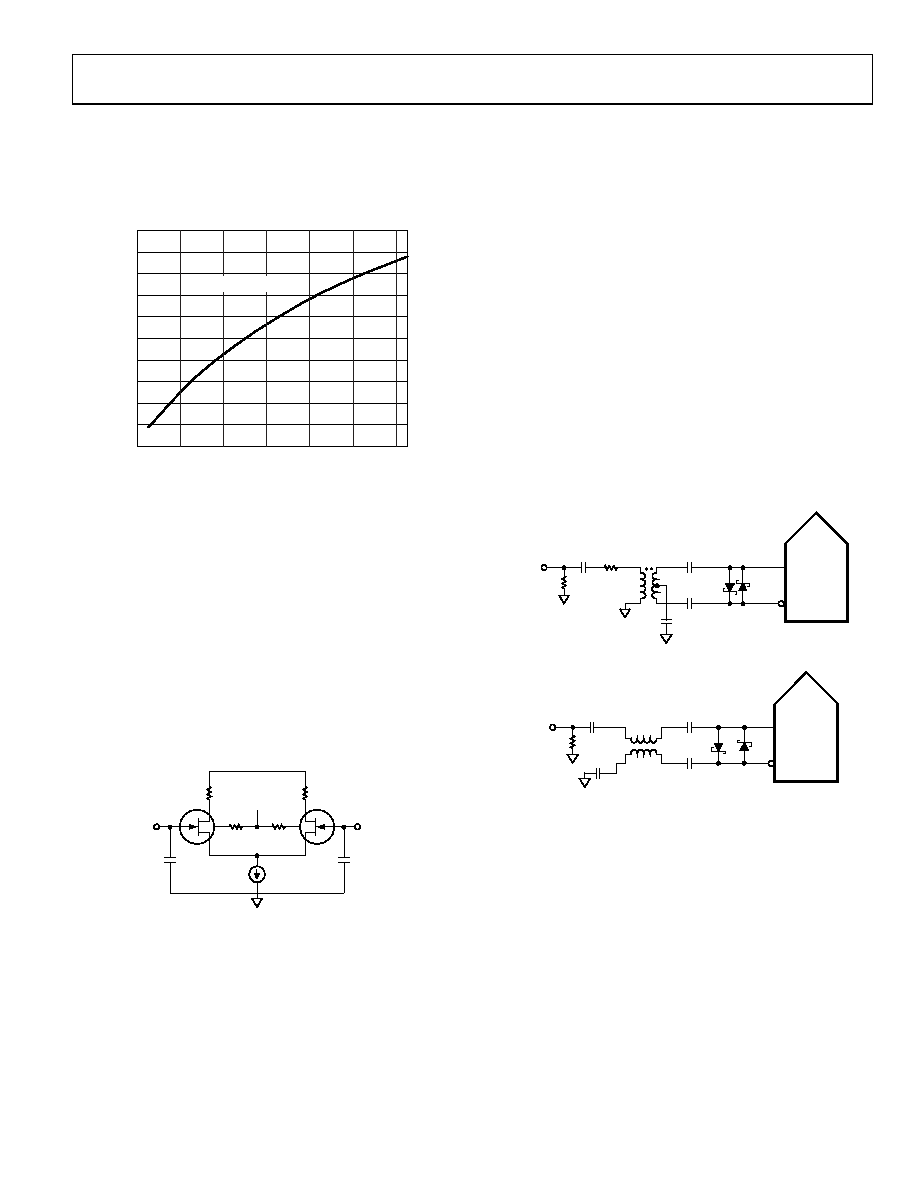

The use of an external reference may be necessary to enhance

the gain accuracy of the ADC or improve thermal drift charac-

teristics. Figure 48 shows the typical drift characteristics of the

internal reference in 1.0 V mode.

4

3

2

1

0

–1

–2

–3

–4

–5

–6

–40

–20

0

20

40

60

80

TEMPERATURE (°C)

V

RE

F

E

RRO

R

(m

V

)

08

122

-05

2

VREF ERROR (mV)

Figure 48. Typical VREF Drift

When the SENSE pin is tied to AVDD, the internal reference is

disabled, allowing the use of an external reference. An internal

reference buffer loads the external reference with an equivalent

7.5 kΩ load (see Figure 37). The internal buffer generates the

positive and negative full-scale references for the ADC core.

Therefore, the external reference must be limited to a maximum

of 1.0 V.

CLOCK INPUT CONSIDERATIONS

For optimum performance, clock the AD9204 sample clock

inputs, CLK+ and CLK, with a differential signal. The signal

is typically ac-coupled into the CLK+ and CLK pins via a

transformer or capacitors. These pins are biased internally

(see Figure 49) and require no external bias.

0.9V

AVDD

2pF

CLK–

CLK+

08

12

2-

0

16

Figure 49. Equivalent Clock Input Circuit

Clock Input Options

The AD9204 has a very flexible clock input structure. The clock

input can be a CMOS, LVDS, LVPECL, or sine wave signal.

Regardless of the type of signal being used, clock source jitter

is of the most concern, as described in the Jitter Considerations

section.

the AD9204 (at clock rates up to 625 MHz). A low jitter clock

source is converted from a single-ended signal to a differential

signal using either an RF transformer or an RF balun.

The RF balun configuration is recommended for clock frequencies

between 125 MHz and 625 MHz, and the RF transformer is recom-

mended for clock frequencies from 10 MHz to 200 MHz. The

back-to-back Schottky diodes across the transformer/balun

secondary limit clock excursions into the AD9204 to approx-

imately 0.8 V p-p differential.

This limit helps prevent the large voltage swings of the clock

from feeding through to other portions of the AD9204 while

preserving the fast rise and fall times of the signal that are critical

to a low jitter performance.

0.1F

SCHOTTKY

DIODES:

HSMS2822

CLOCK

INPUT

50

100

CLK–

CLK+

ADC

Mini-Circuits

ADT1-1WT, 1:1 Z

XFMR

08

12

2-

0

17

Figure 50. Transformer-Coupled Differential Clock (Up to 200 MHz)

0.1F

1nF

CLOCK

INPUT

1nF

50

CLK–

CLK+

SCHOTTKY

DIODES:

HSMS2822

ADC

08

12

2-

01

8

Figure 51. Balun-Coupled Differential Clock (Up to 625 MHz)

相关PDF资料 |

PDF描述 |

|---|---|

| MS3106E24-9P | CONN PLUG 2POS STRAIGHT W/PINS |

| MS3106E22-22PY | CONN PLUG 4POS STRAIGHT W/PINS |

| CS5560-ISZR | IC ADC 24BIT DELTA-SIGMA 24-SSOP |

| AD7739BRUZ-REEL7 | IC ADC 24BIT 8CH SIG-DEL 24TSSOP |

| AD9223ARSZ-REEL | IC ADC 12BIT 3.0MSPS 28SSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9204BCPZRL7-80 | 功能描述:IC ADC 10BIT 80MSPS 64LFCSP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1,000 系列:- 位数:12 采样率(每秒):300k 数据接口:并联 转换器数目:1 功率耗散(最大):75mW 电压电源:单电源 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:24-SOIC(0.295",7.50mm 宽) 供应商设备封装:24-SOIC 包装:带卷 (TR) 输入数目和类型:1 个单端,单极;1 个单端,双极 |

| AD9208BBPZRL-3000 | |

| AD9211 | 制造商:AD 制造商全称:Analog Devices 功能描述:10-Bit, 200 MSPS/250 MSPS/300 MSPS, 1.8 V Analog-to-Digital Converter |

| AD9211_07 | 制造商:AD 制造商全称:Analog Devices 功能描述:10-Bit, 200 MSPS/250 MSPS/300 MSPS, 1.8 V Analog-to-Digital Converter |

| AD9211-170EB | 制造商:AD 制造商全称:Analog Devices 功能描述:10-Bit, 170/200/250 MSPS 1.8 V A/D Converter |

发布紧急采购,3分钟左右您将得到回复。