- 您现在的位置:买卖IC网 > PDF目录10073 > AD9229ABCPZRL7-50 (Analog Devices Inc)IC ADC 12BIT SRL 50MSPS 48LFCSP PDF资料下载

参数资料

| 型号: | AD9229ABCPZRL7-50 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 14/40页 |

| 文件大小: | 0K |

| 描述: | IC ADC 12BIT SRL 50MSPS 48LFCSP |

| 标准包装: | 750 |

| 位数: | 12 |

| 采样率(每秒): | 50M |

| 数据接口: | 串行 |

| 转换器数目: | 4 |

| 功率耗散(最大): | 1.08W |

| 电压电源: | 模拟和数字 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 48-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 48-LFCSP-VQ(7x7) |

| 包装: | 带卷 (TR) |

| 输入数目和类型: | 8 个单端,单极;4 个差分,单极 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页当前第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页

AD9229

Rev. B | Page 21 of 40

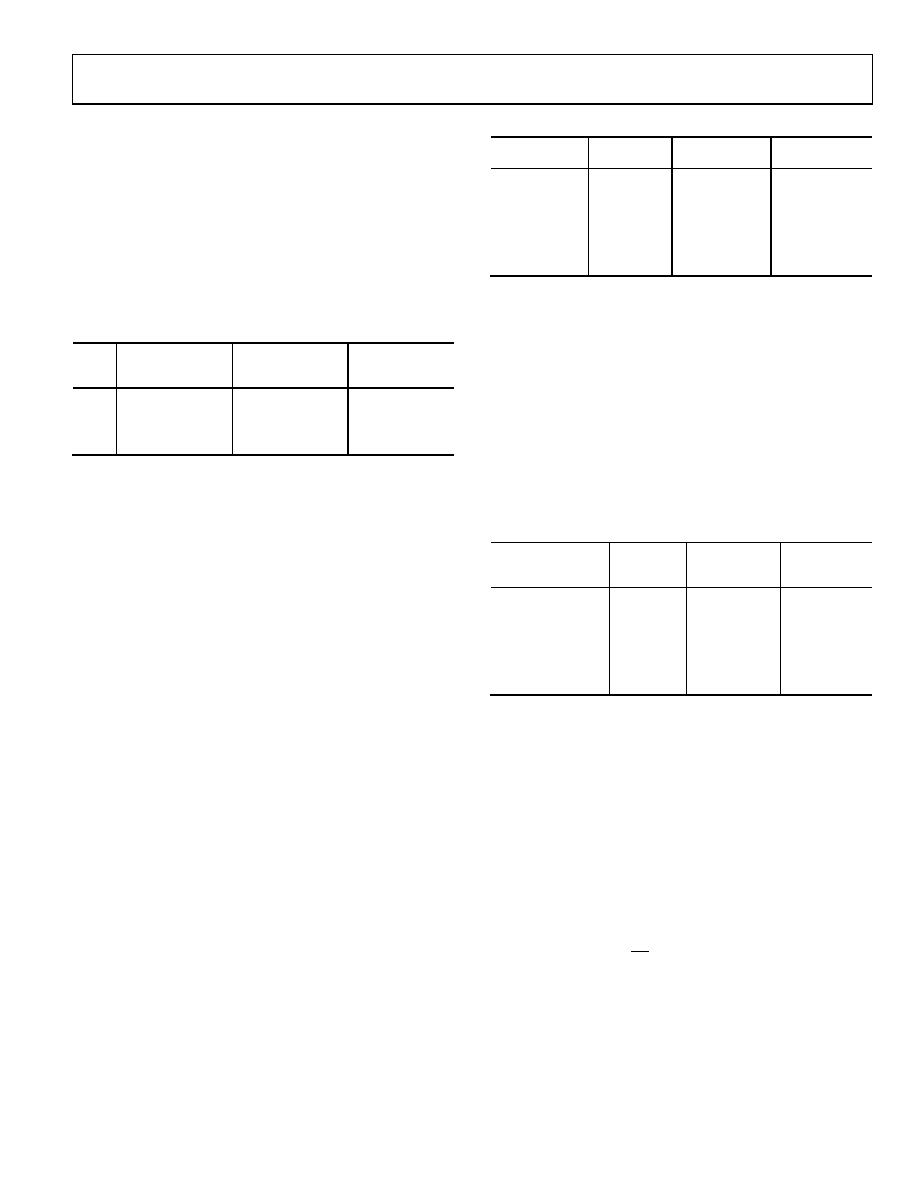

Table 9. Digital Test Pattern Pin Settings

The AD9229’s LVDS outputs facilitate interfacing with LVDS

receivers in custom ASICs and FPGAs that have LVDS capa-

bility for superior switching performance in noisy environ-

ments. Single point-to-point net topologies are recommended

with a 100 Ω termination resistor placed as close to the receiver

as possible. It is recommended to keep the trace length no

longer than 12 inches and to keep differential output traces

close together and at equal lengths.

Selected DTP

DTP Voltage

Resulting

D+ and D–

Resulting

FCO and DCO

Normal

operation

AGND

Normal

operation

Normal

operation

DTP1

AVDD/3

1000 0000 0000

Normal

operation

DTP2

2 × AVDD/3

1010 1010 1010

Normal

operation

Restricted

AVDD

N/A

The format of the output data is offset binary. An example of

the output coding format can be found in Table 8.

Voltage Reference

A stable and accurate 0.5 V voltage reference is built into the

AD9229. The input range can be adjusted by varying the refer-

ence voltage applied to the AD9229, using either the internal

reference or an externally applied reference voltage. The input

span of the ADC tracks reference voltage changes linearly.

Table 8. Digital Output Coding

Code

(VIN+) (VIN),

Input Span =

2 V p-p (V)

(VIN+) (VIN),

Input Span =

1 V p-p (V)

Digital Output

Offset Binary

(D11 ... D0)

4095

1.000

0.500

1111 1111 1111

2048

0

1000 0000 0000

2047

0.000488

0.000244

0111 1111 1111

0

1.00

0.5000

0000 0000 0000

When applying the decoupling capacitors to the VREF, REFT,

and REFB pins, use ceramic, low ESR capacitors. These

capacitors should be close to the ADC pins and on the same

layer of the PCB as the AD9229. The recommended capacitor

values and configurations for the AD9229 reference pin can be

Timing

Data from each ADC is serialized and provided on a separate

channel. The data rate for each serial stream is equal to 12 bits

times the sample clock rate, with a maximum of 780 bps (12 bits

× 65 MSPS = 780 bps). The lowest typical conversion rate is

10 MSPS.

Table 10. Reference Settings

Selected Mode

SENSE

Voltage

Resulting

VREF (V)

Resulting

Differential

Span (V p-p)

External Reference

AVDD

N/A

2 × external

reference

Internal, 1 V p-p FSR

VREF

0.5

1.0

Programmable

0.2 V to

VREF

0.5 × (1 +

R2/R1)

2 × VREF

Internal, 2 V p-p FSR

AGND to

0.2 V

1.0

2.0

Two output clocks are provided to assist in capturing data from

the AD9229. The DCO is used to clock the output data and is

equal to six times the sampling clock (CLK) rate. Data is

clocked out of the AD9229 and can be captured on the rising

and falling edges of the DCO that supports double-data rate

(DDR) capturing. The frame clock out (FCO) is used to signal

the start of a new output byte and is equal to the sampling clock

rate. See the timing diagram shown in Figure 2 for more

information.

Internal Reference Connection

A comparator within the AD9229 detects the potential at the

SENSE pin and configures the reference into four possible states

(summarized in Table 10). If SENSE is grounded, the reference

amplifier switch is connected to the internal resistor divider (see

Figure 42), setting VREF to 1 V. Connecting the SENSE pin to

the VREF pin switches the amplifier output to the SENSE pin,

configuring the internal op amp circuit as a voltage follower and

providing a 0.5 V reference output. If an external resistor

divider is connected as shown in Figure 43, the switch is again

set to the SENSE pin. This puts the reference amplifier in a

noninverting mode and defines the VREF output as

DTP Pin

The digital test pattern (DTP) pin can be enabled for two types

of test patterns, as summarized in Table 9. When the DTP is

tied to AVDD/3, all the ADC channel outputs shift out the

following pattern: 1000 0000 0000. When the DTP is tied to 2 ×

AVDD/3, all the ADC channel outputs shift out the following

pattern: 1010 1010 1010. The FCO and DCO outputs still work

as usual while all channels shift out the test pattern. This

pattern allows the user to perform timing alignment

adjustments between the FCO, DCO, and the output data. For

normal operation, this pin should be tied to AGND.

+

×

=

R1

R2

VREF

1

5

.

0

In all reference configurations, REFT and REFB establish their

input span of the ADC core. The analog input full-scale range

of the ADC equals twice the voltage at the reference pin for

either an internal or an external reference configuration.

相关PDF资料 |

PDF描述 |

|---|---|

| AD7870JP | IC ADC 12BIT SAMPLING 3V 28-PLCC |

| MS27467E21F35PB | CONN PLUG 79POS STRAIGHT W/PINS |

| D38999/20FA98PE | CONN RCPT 3POS WALL MNT W/PINS |

| AD7626BCPZ-RL7 | IC ADC 16BIT 10MSPS DIFF 32LFCSP |

| LTC2369IMS-18#TRPBF | IC ADC 18BIT SRL/SPI 16-MSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9229ABCPZRL7-65 | 功能描述:IC ADC 12BIT SRL 65MSPS 48LFCSP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1 系列:- 位数:14 采样率(每秒):83k 数据接口:串行,并联 转换器数目:1 功率耗散(最大):95mW 电压电源:双 ± 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:28-DIP(0.600",15.24mm) 供应商设备封装:28-PDIP 包装:管件 输入数目和类型:1 个单端,双极 |

| AD9229BBC-65 | 制造商:Analog Devices 功能描述:- Bulk |

| ad9229bcp-50 | 制造商:Analog Devices 功能描述: |

| AD9229BCP-65 | 制造商:Analog Devices 功能描述:- Bulk |

| AD9229BCPZ-50 | 制造商:Analog Devices 功能描述:ADC Quad Pipelined 50Msps 12-bit Serial 48-Pin LFCSP EP |

发布紧急采购,3分钟左右您将得到回复。