- 您现在的位置:买卖IC网 > PDF目录1986 > AD9248BCPZRL-65 (Analog Devices Inc)IC ADC 14BIT DUAL 65MSPS 64LFCSP PDF资料下载

参数资料

| 型号: | AD9248BCPZRL-65 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 29/48页 |

| 文件大小: | 0K |

| 描述: | IC ADC 14BIT DUAL 65MSPS 64LFCSP |

| 标准包装: | 2,500 |

| 位数: | 14 |

| 采样率(每秒): | 65M |

| 数据接口: | 并联 |

| 转换器数目: | 2 |

| 功率耗散(最大): | 600mW |

| 电压电源: | 单电源 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 64-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 64-LFCSP-VQ(9x9) |

| 包装: | 带卷 (TR) |

| 输入数目和类型: | 4 个单端,单极;2 个差分,单极 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页当前第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页

AD9248

Rev. B | Page 35 of 48

DUAL ADC LFCSP PCB

The PCB requires a low jitter clock source, analog sources, and

power supplies. The PCB interfaces directly with Analog Devices

standard dual-channel data capture board (HSC-ADC-EVAL-DC),

which together with ADI’s ADC Analyzer software allows for

quick ADC evaluation.

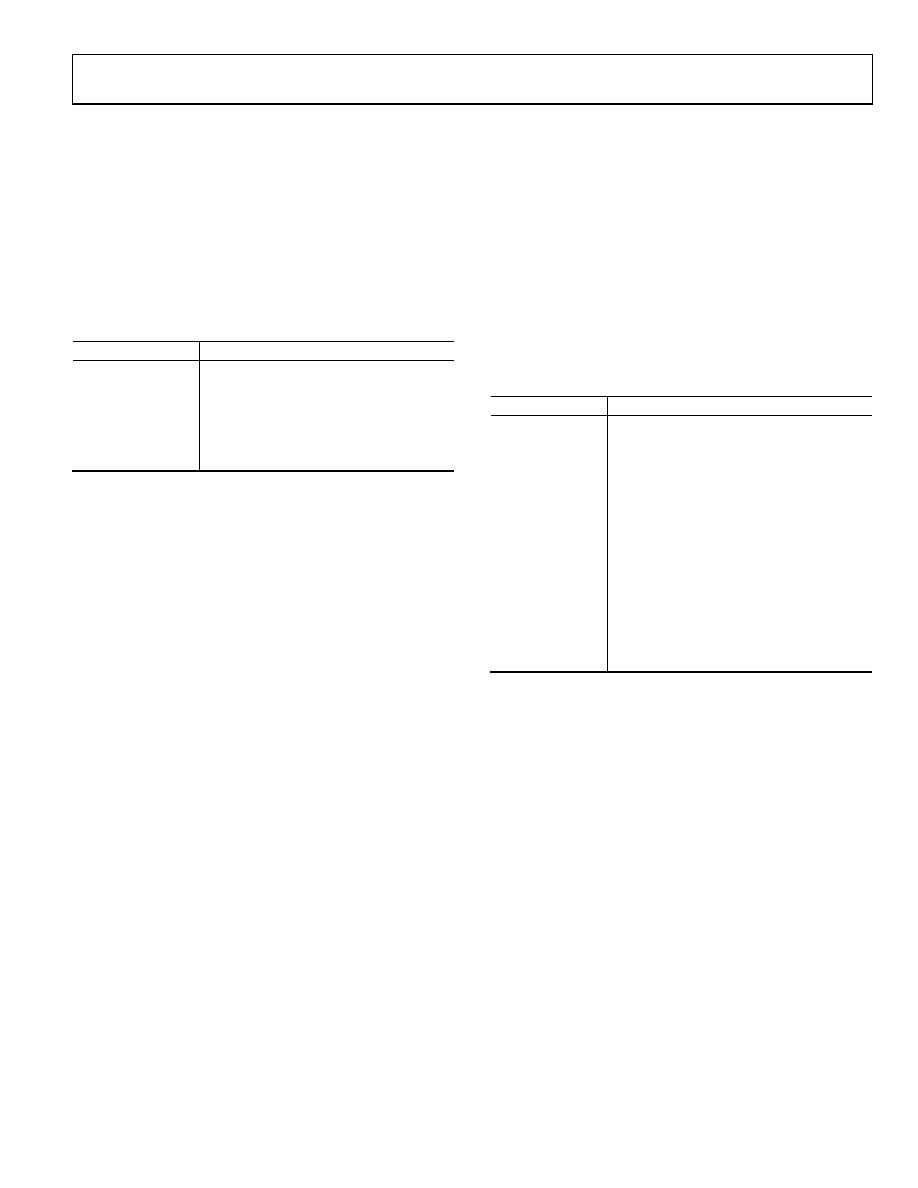

POWER CONNECTOR

Power is supplied to the board via three detachable 4-lead

power strips.

Table 11. Power Connector

Comments

Analog supply for ADC

Output supply for ADC

Supply circuitry

VREF

Optional external VREF

+5 V

Optional op amp supply

5 V

Optional op amp supply

1VCC, VDD, and VDL are the minimum required power connections.

ANALOG INPUTS

The evaluation board accepts a 2 V p-p analog input signal

centered at ground at two SMB connectors, Input A and

Input B. These signals are terminated at their respective

transformer primary side. T1 and T2 are wideband RF

transformers that provide the single-ended-to-differential

conversion, allowing the ADC to be driven differentially,

minimizing even-order harmonics. The analog signals can be

low-pass filtered at the transformer secondary to reduce high

frequency aliasing.

OPTIONAL OPERATIONAL AMPLIFIER

The PCB has been designed to accommodate an optional

AD8139 op amp that can serve as a convenient solution for

dc-coupled applications. To use the AD8139 op amp, remove

C14, R4, R5, C13, R37, and R36. Place R22, R23, R30, and R24.

CLOCK

The clock inputs are buffered on the board at U5 and U6. These

gates provide buffered clocks to the on-board latches, U2 and

U4, ADC input clocks, and DRA, DRB that are available at the

output Connector P3, P8. The clocks can be inverted at the

timing jumpers labeled with the respective clocks. The clock

paths also provide for various termination options. The ADC

input clocks can be set to bypass the buffers at solder bridges

P2, P9 and P10, P12. An optional clock buffer U3, U7 can also

be placed. The clock inputs can be bridged at TIEA, TIEB (R20,

R40) to allow one to clock both channels from one clock source;

however, optimal performance is obtained by driving J2 and J3.

Table 12. Jumpers

Terminal

Comments

OEB A

Output Enable for A Side

PDWN A

Power-Down A

MUX

Mux Input

SHARED REF

Shared Reference Input

DR A

Invert DR A

LATA

Invert A Latch Clock

ENC A

Invert Encode A

OEB B

Output Enable for B Side

PDWN B

Power-Down B

DFS

Data Format Select

SHARED REF

Shared Reference Input

DR B

Invert DR B

LATB

Invert B Latch Clock

ENC B

Invert Encode B

VOLTAGE REFERENCE

The ADC SENSE pin is brought out to E41, and the internal

reference mode is selected by placing a jumper from E41 to

ground (E27). External reference mode is selected by placing a

jumper from E41 to E25 and E30 to E2. R56 and R45 allow for

programmable reference mode selection.

DATA OUTPUTS

The ADC outputs are latched on the PCB at U2, U4. The ADC

outputs have the recommended series resistors in line to limit

switching transient effects on ADC performance.

相关PDF资料 |

PDF描述 |

|---|---|

| AD9251BCPZ-65 | IC ADC 14BIT 65MSPS 64LFCSP |

| AD9252ABCPZRL7-50 | IC ADC 14BIT SRL 50MSPS 64LFCSP |

| AD9253TCPZ-125EP | IC ADC 14BIT SRL 125MSPS 48LFCSP |

| AD9257BCPZ-65 | IC ADC 14BIT SRL 65MSPS 64LFCSP |

| AD9258BCPZ-125 | IC ADC 14BIT 125MSPS DL 64LFCSP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9248BCPZRL7-20 | 制造商:AD 制造商全称:Analog Devices 功能描述:14-Bit, 20/40/65 MSPS Dual A/ D Converter |

| AD9248BCPZRL7-40 | 制造商:AD 制造商全称:Analog Devices 功能描述:14-Bit, 20/40/65 MSPS Dual A/ D Converter |

| AD9248BCPZRL7-65 | 制造商:AD 制造商全称:Analog Devices 功能描述:14-Bit, 20/40/65 MSPS Dual A/ D Converter |

| AD9248BST-20 | 制造商:AD 制造商全称:Analog Devices 功能描述:14-Bit, 20/40/65 MSPS Dual A/ D Converter |

| AD9248BST-40 | 制造商:AD 制造商全称:Analog Devices 功能描述:14-Bit, 20/40/65 MSPS Dual A/ D Converter |

发布紧急采购,3分钟左右您将得到回复。