- 您现在的位置:买卖IC网 > PDF目录1987 > AD9517-3ABCPZ-RL7 (Analog Devices Inc)IC CLOCK GEN 2.0GHZ VCO 48LFCSP PDF资料下载

参数资料

| 型号: | AD9517-3ABCPZ-RL7 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 4/80页 |

| 文件大小: | 0K |

| 描述: | IC CLOCK GEN 2.0GHZ VCO 48LFCSP |

| 标准包装: | 750 |

| 类型: | 时钟发生器,扇出配送 |

| PLL: | 是 |

| 输入: | CMOS,LVDS,LVPECL |

| 输出: | CMOS,LVDS,LVPECL |

| 电路数: | 1 |

| 比率 - 输入:输出: | 1:12 |

| 差分 - 输入:输出: | 是/是 |

| 频率 - 最大: | 2.25GHz |

| 除法器/乘法器: | 是/无 |

| 电源电压: | 3.135 V ~ 3.465 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 48-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 48-LFCSP-VQ(7x7) |

| 包装: | 带卷 (TR) |

第1页第2页第3页当前第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页

AD9517-3

Data Sheet

Rev. E | Page 12 of 80

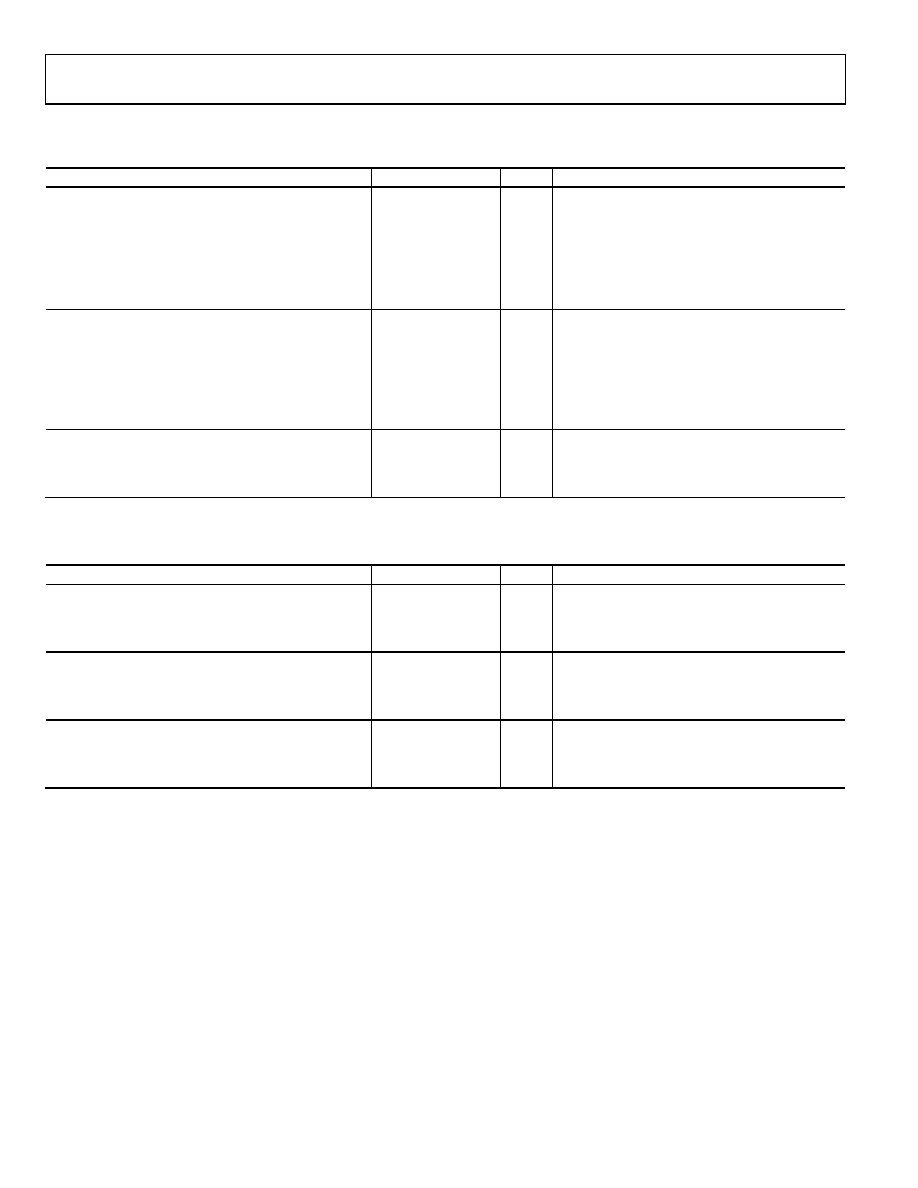

CLOCK OUTPUT ADDITIVE TIME JITTER (VCO DIVIDER NOT USED)

Table 11.

Parameter

Min

Typ

Max

Unit

Test Conditions/Comments

LVPECL OUTPUT ADDITIVE TIME JITTER

Distribution section only; does not include PLL

and VCO; uses rising edge of clock signal

CLK = 622.08 MHz; LVPECL = 622.08 MHz; Divider = 1

40

fs rms

BW = 12 kHz to 20 MHz

CLK = 622.08 MHz; LVPECL = 155.52 MHz; Divider = 4

80

fs rms

BW = 12 kHz to 20 MHz

CLK = 1.6 GHz; LVPECL = 100 MHz; Divider = 16

215

fs rms

Calculated from SNR of ADC method; DCC not

used for even divides

CLK = 500 MHz; LVPECL = 100 MHz; Divider = 5

245

fs rms

Calculated from SNR of ADC method; DCC on

LVDS OUTPUT ADDITIVE TIME JITTER

Distribution section only; does not include PLL and

VCO; uses rising edge of clock signal

CLK = 1.6 GHz; LVDS = 800 MHz; Divider = 2;

VCO Divider Not Used

85

fs rms

BW = 12 kHz to 20 MHz

CLK = 1 GHz; LVDS = 200 MHz; Divider = 5

113

fs rms

BW = 12 kHz to 20 MHz

CLK = 1.6 GHz; LVDS = 100 MHz; Divider = 16

280

fs rms

Calculated from SNR of ADC method; DCC not used

for even divides

CMOS OUTPUT ADDITIVE TIME JITTER

Distribution section only; does not include PLL and

VCO; uses rising edge of clock signal

CLK = 1.6 GHz; CMOS = 100 MHz; Divider = 16

365

fs rms

Calculated from SNR of ADC method; DCC not used

for even divides

CLOCK OUTPUT ADDITIVE TIME JITTER (VCO DIVIDER USED)

Table 12.

Parameter

Min

Typ

Max

Unit

Test Conditions/Comments

LVPECL OUTPUT ADDITIVE TIME JITTER

Distribution section only; does not include PLL and

VCO; uses rising edge of clock signal

CLK = 2.4 GHz; VCO DIV = 2; LVPECL = 100 MHz;

Divider = 12; Duty-Cycle Correction = Off

210

fs rms

Calculated from SNR of ADC method

LVDS OUTPUT ADDITIVE TIME JITTER

Distribution section only; does not include PLL and

VCO; uses rising edge of clock signal

CLK = 2.4 GHz; VCO DIV = 2; LVDS = 100 MHz;

Divider = 12; Duty-Cycle Correction = Off

285

fs rms

Calculated from SNR of ADC method

CMOS OUTPUT ADDITIVE TIME JITTER

Distribution section only; does not include PLL and

VCO; uses rising edge of clock signal

CLK = 2.4 GHz; VCO DIV = 2; CMOS = 100 MHz;

Divider = 12; Duty-Cycle Correction = Off

350

fs rms

Calculated from SNR of ADC method

相关PDF资料 |

PDF描述 |

|---|---|

| AD9517-4ABCPZ-RL7 | IC CLOCK GEN 1.8GHZ VCO 48LFCSP |

| AD9518-0ABCPZ | IC CLOCK GEN 6CH 2.8GHZ 48LFCSP |

| AD9518-1ABCPZ | IC CLOCK GEN 6CH 2GHZ 48LFCSP |

| AD9518-2ABCPZ-RL7 | IC CLOCK GEN 6CH 2.2GHZ 48LFCSP |

| AD9518-3ABCPZ | IC CLOCK GEN 6CH 2GHZ 48LFCSP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9517-3BCPZ | 制造商:Analog Devices 功能描述: |

| AD9517-3BCPZ-REEL7 | 制造商:Analog Devices 功能描述: |

| AD9517-3BCPZ-TR | 制造商:Analog Devices 功能描述:12-OUTPUT CLOCK GENERATOR WITH INTEGRATED 2.0 GHZ VCO - Tape and Reel |

| AD9517-4 | 制造商:AD 制造商全称:Analog Devices 功能描述:12-Output Clock Generator with Integrated 1.6 GHz VCO |

| AD9517-4A/PCBZ | 功能描述:BOARD EVALUATION FOR AD9517-4A RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 标准包装:1 系列:- 主要目的:电信,线路接口单元(LIU) 嵌入式:- 已用 IC / 零件:IDT82V2081 主要属性:T1/J1/E1 LIU 次要属性:- 已供物品:板,电源,线缆,CD 其它名称:82EBV2081 |

发布紧急采购,3分钟左右您将得到回复。