- 您现在的位置:买卖IC网 > PDF目录17022 > AD9633-125EBZ (Analog Devices Inc)BOARD EVAL FOR AD9633 PDF资料下载

参数资料

| 型号: | AD9633-125EBZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 22/40页 |

| 文件大小: | 0K |

| 描述: | BOARD EVAL FOR AD9633 |

| 标准包装: | 1 |

| 系列: | * |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页当前第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页

Data Sheet

AD9633

Rev. 0 | Page 29 of 40

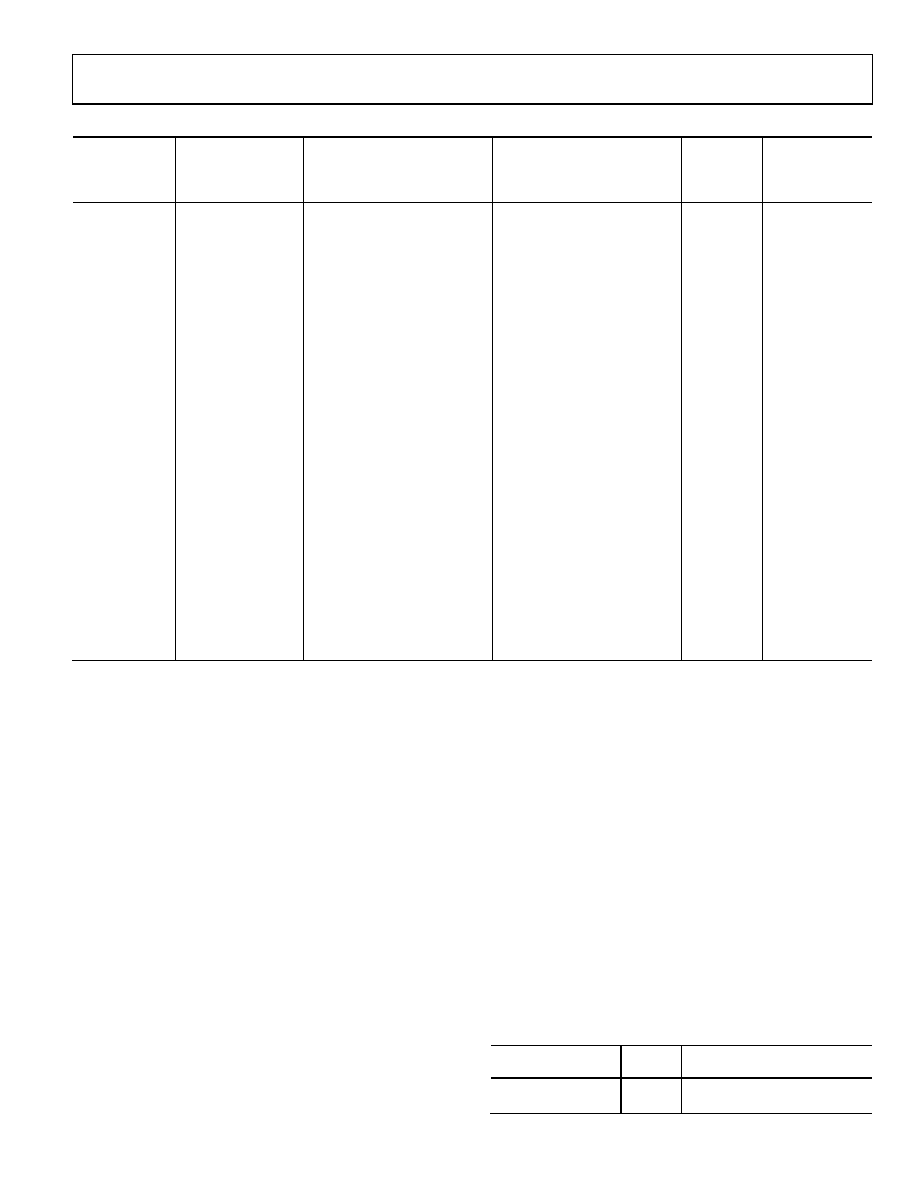

Table 11. Flexible Output Test Modes

Output Test

Mode

Bit Sequence

Pattern Name

Digital Output Word 1

Digital Output Word 2

Subject to

Data

Format

Select

Notes

0000

Off (default)

N/A

0001

Midscale short

10 0000 0000 (10-bit)

1000 0000 0000 (12-bit)

N/A

Yes

Offset binary

code shown

0010

+Full-scale short

11 1111 1111 (10-bit)

1111 1111 1111 (12-bit)

N/A

Yes

Offset binary

code shown

0011

Full-scale short

00 0000 0000 (10-bit)

0000 0000 0000 (12-bit)

N/A

Yes

Offset binary

code shown

0100

Checkerboard

10 1010 1010 (10-bit)

1010 1010 1010 (12-bit)

01 0101 0101 (10-bit)

0101 0101 0101 (12-bit)

No

0101

PN sequence long1

N/A

Yes

PN23

ITU 0.150

X23 + X18 + 1

0110

PN sequence short1

N/A

Yes

PN9

ITU 0.150

X9 + X5 + 1

0111

One-/zero-word

toggle

11 1111 1111 (10-bit)

1111 1111 1111 (12-bit)

00 0000 0000 (10-bit)

0000 0000 0000 (12-bit)

No

1000

User input

Register 0x19 to Register 0x1A

Register 0x1B to Register 0x1C

No

1001

1-/0-bit toggle

10 1010 1010 (10-bit)

1010 1010 1010 (12-bit)

N/A

No

1010

1× sync

00 0011 1111 (10-bit)

0000 0111 1111 (12-bit)

N/A

No

1011

One bit high

00 0000 0000 (10-bit)

0000 0000 0000 (12-bit)

N/A

No

Pattern

associated with

the external pin

1100

Mixed frequency

10 0011 0011 (10-bit)

1000 0110 0111 (12-bit)

N/A

No

1 All test mode options except PN sequence short and PN sequence long can support 10-bit to 12-bit word lengths to verify data capture to the receiver.

When the SPI is used, the DCO phase can be adjusted in 60°

increments relative to the data edge. This enables the user to

refine system timing margins if required. The default DCO+

and DCO timing, as shown in Figure 2, is 90° relative to the

output data edge.

A 10-bit serial stream can also be initiated from the SPI. This

allows the user to implement and test compatibility to lower

resolution systems. When changing the resolution to a 10-bit

serial stream, the data stream is shortened.

In default mode, as shown in Figure 2, the MSB is first in the

data output serial stream. This can be inverted so that the LSB is

first in the data output serial stream by using the SPI.

There are 12 digital output test pattern options available that

can be initiated through the SPI. This is a useful feature when

validating receiver capture and timing. Refer to Table 11 for the

output bit sequencing options available. Some test patterns have

two serial sequential words and can be alternated in various

ways, depending on the test pattern chosen. Note that some

patterns do not adhere to the data format select option. In

addition, custom user-defined test patterns can be assigned in

the 0x19, 0x1A, 0x1B, and 0x1C register addresses.

The PN sequence short pattern produces a pseudorandom bit

sequence that repeats itself every 29 1 or 511 bits. A descrip-

tion of the PN sequence and how it is generated can be found in

Section 5.1 of the ITU-T 0.150 (05/96) standard. The seed value

is all 1s (see Table 12 for the initial values). The output is a parallel

representation of the serial PN9 sequence in MSB-first format.

The first output word is the first 12 bits of the PN9 sequence in

MSB aligned form.

The PN sequence long pattern produces a pseudorandom bit

sequence that repeats itself every 223 1 or 8,388,607 bits. A

description of the PN sequence and how it is generated can be

found in Section 5.6 of the ITU-T 0.150 (05/96) standard. The

seed value is all 1s (see Table 12 for the initial values) and the

AD9633 inverts the bit stream with relation to the ITU standard.

The output is a parallel representation of the serial PN23 sequence

in MSB-first format. The first output word is the first 12 bits of

the PN23 sequence in MSB aligned form.

Table 12. PN Sequence

Sequence

Initial

Value

First Three Output Samples

(MSB First) Twos Complement

PN Sequence Short

0x7F8

0xBDF, 0x973, 0xA09

PN Sequence Long

0x7FF

0x7FE, 0x800, 0xFC0

相关PDF资料 |

PDF描述 |

|---|---|

| PM0805-68NK-RC | INDUCTOR CHIP 68NH 10% SMD |

| MAX1379EVKIT+ | EVAL KIT FOR MAX1379 |

| AD9608-125EBZ | BOARD EVAL AD9608-125 |

| AD9484-500EBZ | BOARD EVAL W/AD9484BCPZ-500 |

| SRR6038-560Y | INDUCTOR POWER 56UH .85A SMD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9633BCPZ-105 | 功能描述:IC ADC 12BIT SRL 105MSPS 48LFCSP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 其它有关文件:TSA1204 View All Specifications 标准包装:1 系列:- 位数:12 采样率(每秒):20M 数据接口:并联 转换器数目:2 功率耗散(最大):155mW 电压电源:模拟和数字 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-TQFP 供应商设备封装:48-TQFP(7x7) 包装:Digi-Reel® 输入数目和类型:4 个单端,单极;2 个差分,单极 产品目录页面:1156 (CN2011-ZH PDF) 其它名称:497-5435-6 |

| AD9633BCPZ-125 | 功能描述:IC ADC 12BIT SRL 125MSPS 48LFCSP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 其它有关文件:TSA1204 View All Specifications 标准包装:1 系列:- 位数:12 采样率(每秒):20M 数据接口:并联 转换器数目:2 功率耗散(最大):155mW 电压电源:模拟和数字 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-TQFP 供应商设备封装:48-TQFP(7x7) 包装:Digi-Reel® 输入数目和类型:4 个单端,单极;2 个差分,单极 产品目录页面:1156 (CN2011-ZH PDF) 其它名称:497-5435-6 |

| AD9633BCPZ-80 | 功能描述:IC ADC 12BIT SRL 80MSPS 48LFCSP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 其它有关文件:TSA1204 View All Specifications 标准包装:1 系列:- 位数:12 采样率(每秒):20M 数据接口:并联 转换器数目:2 功率耗散(最大):155mW 电压电源:模拟和数字 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-TQFP 供应商设备封装:48-TQFP(7x7) 包装:Digi-Reel® 输入数目和类型:4 个单端,单极;2 个差分,单极 产品目录页面:1156 (CN2011-ZH PDF) 其它名称:497-5435-6 |

| AD9633BCPZRL7-105 | 功能描述:IC ADC 12BIT SRL 105MSPS 48LFCSP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1 系列:- 位数:14 采样率(每秒):83k 数据接口:串行,并联 转换器数目:1 功率耗散(最大):95mW 电压电源:双 ± 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:28-DIP(0.600",15.24mm) 供应商设备封装:28-PDIP 包装:管件 输入数目和类型:1 个单端,双极 |

| AD9633BCPZRL7-125 | 功能描述:模数转换器 - ADC 12 bit 125msps low pwr quad ADC RoHS:否 制造商:Analog Devices 通道数量: 结构: 转换速率: 分辨率: 输入类型: 信噪比: 接口类型: 工作电源电压: 最大工作温度: 安装风格: 封装 / 箱体: |

发布紧急采购,3分钟左右您将得到回复。