- 您现在的位置:买卖IC网 > PDF目录10652 > AD9639BCPZ-210 (Analog Devices Inc)IC ADC 12B 170MSPS QUAD 72LFCSP PDF资料下载

参数资料

| 型号: | AD9639BCPZ-210 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 14/36页 |

| 文件大小: | 0K |

| 描述: | IC ADC 12B 170MSPS QUAD 72LFCSP |

| 标准包装: | 1 |

| 位数: | 12 |

| 采样率(每秒): | 210M |

| 数据接口: | 串行,SPI? |

| 转换器数目: | 4 |

| 功率耗散(最大): | 1.22W |

| 电压电源: | 模拟和数字 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 72-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 72-LFCSP |

| 包装: | 托盘 |

| 输入数目和类型: | 8 个单端,单极;4 个差分,单极 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页当前第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页

Data Sheet

AD9639

Rev. B | Page 21 of 36

DIGITAL OUTPUTS

Serial Data Frame

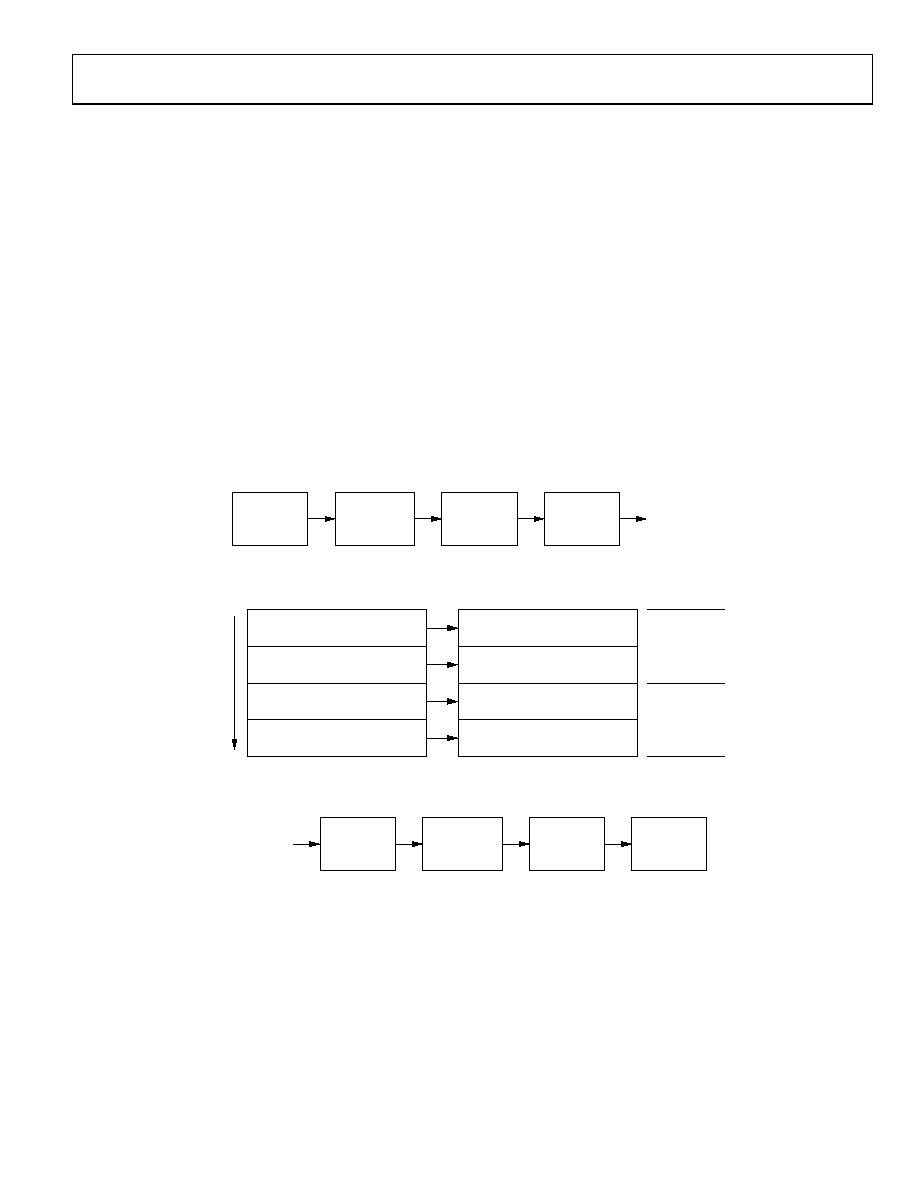

The AD9639 digital output complies with the JEDEC Standard

No. 204 (JESD204), which describes a serial interface for data

converters. JESD204 uses 8B/10B encoding as well as optional

scrambling. K28.5 and K28.7 comma symbols are used for frame

synchronization. The receiver is required to lock onto the serial

data stream and recover the clock with the use of a PLL. (Refer

to IEEE Std 802.3-2002, Section 3, for a complete 8B/10B and

comma symbol description.)

The 8B/10B encoding works by taking eight bits of data (an

octet) and encoding them into a 10-bit symbol. In the AD9639,

the 12-bit converter word is broken into two octets. Bit 11

through Bit 4 are in the first octet. The second octet contains

Bit 3 through Bit 0 and four tail bits. The MSB of the tail bits can

also be used to indicate an out-of-range condition. The tail bits

are configured using the JESD204 register, Address 0x033[3].

The two resulting octets are optionally scrambled and encoded

into their corresponding 10-bit code. The scrambling function

is controlled by the JESD204 register, Address 0x033[0]. Figure 51

shows how the 12-bit data is taken from the ADC, the tail bits are

added, the two octets are scrambled, and the octets are encoded

into two 10-bit symbols. Figure 52 illustrates the data format.

The scrambler uses a self-synchronizing polynomial-based

algorithm defined by the equation 1 + x14 + x15. The descrambler

in the receiver should be a self-synchronizing version of the

scrambler polynomial. A 16-bit parallel implementation is

shown in Figure 54.

Refer to JEDEC Standard No. 204-April 2006, Section 5.1, for

complete transport layer and data format details and Section 5.2

for a complete explanation of scrambling and descrambling.

07973-

201

DATA

FROM

ADC

FRAME

ASSEMBLER

(ADD TAIL BITS)

SCRAMBLER

1 + x14 + x15

8B/10B

ENCODER

TO

RECEIVER

Figure 51. ADC Data Output Path

07973-

200

WORD 0[11:4]

SYMBOL 0[9:0]

WORD 0[3:0],TAIL BITS[3:0]

SYMBOL 1[9:0]

WORD 1[11:4]

SYMBOL 2[9:0]

WORD 1[3:0], TAIL BITS[3:0]

SYMBOL 3[9:0]

TIME

FRAME 0

FRAME 1

Figure 52. 12-Bit Data Transmission with Tail Bits

07973-

202

8B/10B

DECODER

DESCRAMBLER

1 + x14 + x15

FRAME

ALIGNMENT

DATA

OUT

FROM

TRANSMITTER

Figure 53. Required Receiver Data Path

相关PDF资料 |

PDF描述 |

|---|---|

| VI-211-IW-F1 | CONVERTER MOD DC/DC 12V 100W |

| AD9253BCPZ-125 | IC ADC 14BIT SRL 125MSPS 48LFCSP |

| LTC2284IUP#PBF | IC ADC DUAL 14BIT 105MSPS 64-QFN |

| VE-211-IW-F4 | CONVERTER MOD DC/DC 12V 100W |

| LTC2172IUKG-14#PBF | IC ADC 14BIT SER/PAR 65M 52-QFN |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9639BCPZRL-170 | 功能描述:IC ADC 12B 170MSPS QUAD 72LFCSP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:250 系列:- 位数:12 采样率(每秒):1.8M 数据接口:并联 转换器数目:1 功率耗散(最大):1.82W 电压电源:模拟和数字 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-LQFP 供应商设备封装:48-LQFP(7x7) 包装:管件 输入数目和类型:2 个单端,单极 |

| AD9639BCPZRL-210 | 功能描述:模数转换器 - ADC Quad 12 Bit 210 MSPS Seria 1.8V ADC RoHS:否 制造商:Analog Devices 通道数量: 结构: 转换速率: 分辨率: 输入类型: 信噪比: 接口类型: 工作电源电压: 最大工作温度: 安装风格: 封装 / 箱体: |

| AD9640 | 制造商:AD 制造商全称:Analog Devices 功能描述:14-Bit, 80/105/125/150 MSPS, 1.8 V Dual Analog-to-Digital Converter |

| AD9640/PCB | 制造商:AD 制造商全称:Analog Devices 功能描述:14-Bit, 80/105/125/150 MSPS, 1.8 V Dual Analog-to-Digital Converter |

| AD9640-105EBZ | 功能描述:ADC 14BIT 105MSPS DUAL 64-LFCSP RoHS:是 类别:编程器,开发系统 >> 评估板 - 模数转换器 (ADC) 系列:- 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- ADC 的数量:1 位数:12 采样率(每秒):94.4k 数据接口:USB 输入范围:±VREF/2 在以下条件下的电源(标准):- 工作温度:-40°C ~ 85°C 已用 IC / 零件:MAX11645 已供物品:板,软件 |

发布紧急采购,3分钟左右您将得到回复。