- 您现在的位置:买卖IC网 > PDF目录17019 > AD9644-155KITZ (Analog Devices Inc)KIT EVAL FOR AD9644 PDF资料下载

参数资料

| 型号: | AD9644-155KITZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 32/44页 |

| 文件大小: | 0K |

| 描述: | KIT EVAL FOR AD9644 |

| 设计资源: | AD9644 Gerber Files |

| 标准包装: | 1 |

| 系列: | * |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页当前第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页

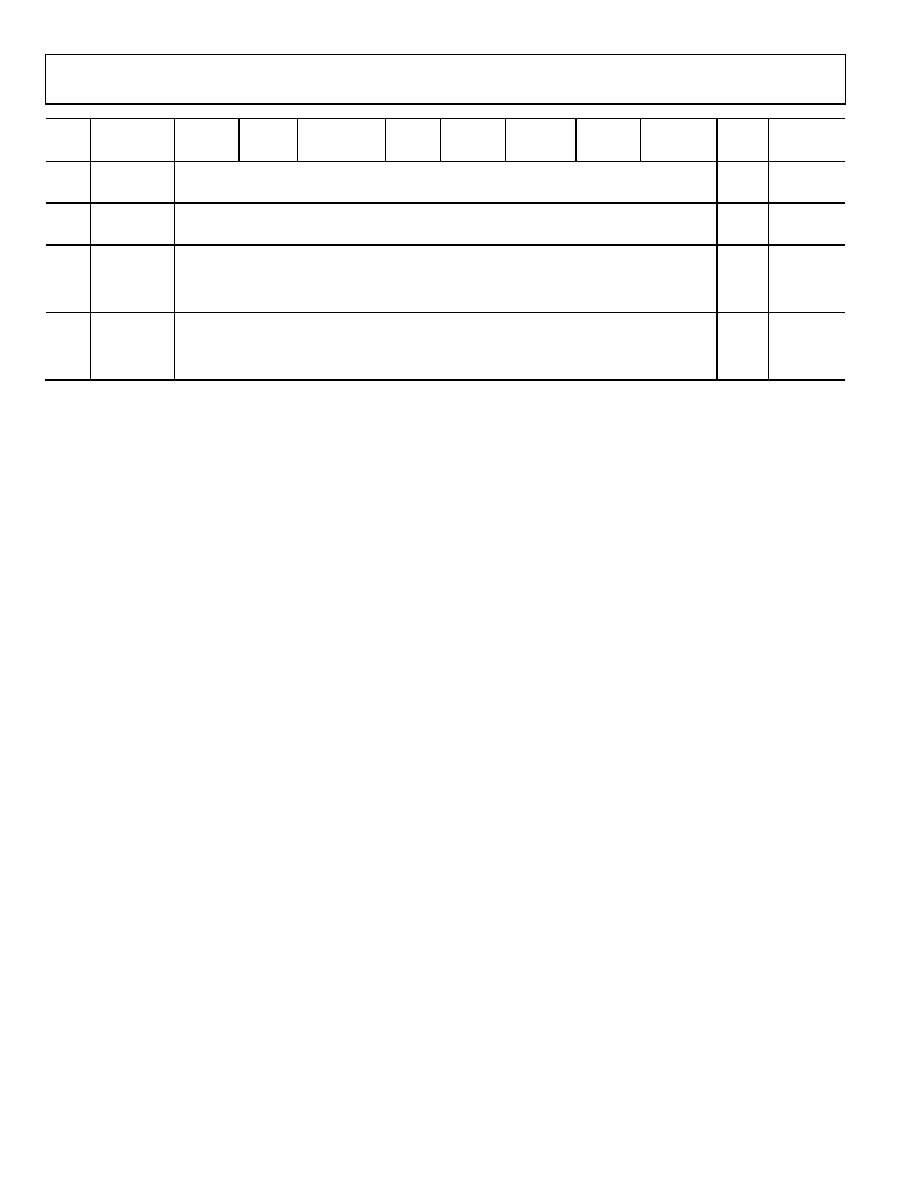

AD9644

Data Sheet

Rev. C | Page 38 of 44

Addr

(Hex)

Register

Name

Bit 7

(MSB)

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

(LSB)

Default

Value

(Hex)

Default/

Comments

0x76

JESD204A

serial reserved

Field 1 (RES1)

Serial Reserved Field 1 (RES1) – these registers are available for customer use

0x00

0x77

JESD204A

serial reserved

Field 2 (RES2)

Serial Reserved Field 2 (RES2) – these registers are available for customer use

0x00

0x78

JESD204A

checksum

value (FCHK)

for Lane 0

(local)

Serial checksum value for Lane 0 (FCHK)

0x00

Read only

0x79

JESD204A

checksum

value (FCHK)

for lane 1

(local)

Serial checksum value for Lane 1 (FCHK)

0x00

Read only

1

The channel index register at Address 0x05 should be set to 0x03 (default) when writing to Address 0x00.

MEMORY MAP REGISTER DESCRIPTIONS

For additional information about functions controlled in

Register 0x00 to Register 0x25, see the AN-877 Application Note,

Interfacing to High Speed ADCs via SPI.

Sync Control (Register 0x3A)

Bits[7:3]—Open

Bit 2—Clock Divider Next Sync Only

If the master sync buffer enable bit (Address 0x3A, Bit 0) and

the clock divider sync enable bit (Address 0x3A, Bit 1) are high, Bit

2 allows the clock divider to sync to the first sync pulse it receives

and to ignore the rest. The clock divider sync enable bit (Address

0x3A, Bit 1) resets after it syncs.

Bit 1—Clock Divider Sync Enable

Bit 1 gates the sync pulse to the clock divider. The sync signal is

enabled when Bit 1 is high and Bit 0 is high. This is continuous

sync mode.

Bit 0—Master Sync Buffer Enable

Bit 0 must be high to enable any of the sync functions. If the

sync capability is not used this bit should remain low to

conserve power.

JESD204A Quick Configure (Register 0x5E)

Bits[7:3]—Reserved

Bits[2:0]—Register Quick Configuration

Writes to Bits[2:0] of this register configure the part for the

most popular modes of operation for the JESD204A link. The

intent of this register is to simplify the part setup for typical

serial link operation modes. Writing values other than 0x0 to

this register causes registers throughout the JESD204A memory

map to be updated. Once these registers have been written the

affected JESD204A configuration register reads back with their

new values and can be updated. These bits are self clearing and

always read back as 0b000.

000: default—configuration determined by other registers

001: two converters using two links with one lane per link

(maximum sample rate = 80 MHz or 155 MHz) Each link

configuration:

M = 1; N’ = 16; CF = 0; K = 16; S = 1; F = 2; L = 1; HD = 0;

010 = two converters using one link with two lanes per link

(Maximum sample rate = 80 MHz or 155 MHz). Each link

configuration:

M = 2; N’ = 16; CF = 0; K = 16; S = 1; F = 2; L = 2; HD = 0;

uses DSYNCA pin for synchronization. Setting this mode sets

Address 0x5F = 0x02 and sets Address 0x60 = 0x14 for Link A

and sets Address 0x60 = 0x01 for Link B.

011 = two converters using one link and a single lane (maxi-

mum sample rate = 78.125 MHz). Each link configuration: M = 2;

N’ = 16; CF = 0; K = 8;S = 1; F = 4; L = 1; HD = 0; uses DSYNCA

pin for synchronization and DOUTA for output signals.

100 to 111: reserved.

JESD204A Lane Assignment (Register 0x5F)

Bits[7:4]—Reserved

Bits[3:0]—JESD204A Serial Lane Control

These bits set the lane usage. See Figure 62.

0000: one lane per link. Link A: Lane 0 sent on Lane A,

Link B: Lane 0 sent on Lane B.

0001: one lane per link. Link A: Lane 0 sent on Lane B,

Link B: Lane 0 sent on Lane A.

0010: two lanes per link. Link A: Lane 0, one sent on Lane A,

Link B disabled.

0011: two lanes per link. Link A: Lane 0, one sent on Lane B,

Lane A. Link B disabled.

0100: two lanes per link. Link B: Lane 0, one sent on Lane A,

Lane B. Link A disabled.

0101: two lanes per link. Link B: Lane 0, one sent on Lane B,

Lane A. Link A disabled.

0110 to 1111: reserved for future use.

相关PDF资料 |

PDF描述 |

|---|---|

| 0210490367 | CABLE JUMPER 1.25MM .051M 30POS |

| DS9097U-009# | COM PORT ADAPTER |

| HKQ0603S3N6C-T | INDUCTOR HI FREQ 3.6NH 0201 |

| VI-2WX-EY | CONVERTER MOD DC/DC 5.2V 50W |

| AD9641-155KITZ | KIT EVAL FOR AD9641 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9644-80KITZ | 功能描述:BOARD EVALUATION FOR AD9644 RoHS:是 类别:编程器,开发系统 >> 评估板 - 模数转换器 (ADC) 系列:- 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- ADC 的数量:1 位数:12 采样率(每秒):94.4k 数据接口:USB 输入范围:±VREF/2 在以下条件下的电源(标准):- 工作温度:-40°C ~ 85°C 已用 IC / 零件:MAX11645 已供物品:板,软件 |

| AD9644BCPZ-155 | 功能描述:模数转换器 - ADC 14 Bit 155 Msps Dual 1.8V ADC RoHS:否 制造商:Analog Devices 通道数量: 结构: 转换速率: 分辨率: 输入类型: 信噪比: 接口类型: 工作电源电压: 最大工作温度: 安装风格: 封装 / 箱体: |

| AD9644BCPZ-80 | 功能描述:IC ADC 14BIT 80MSPS 3V 48LFCSP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1 系列:- 位数:14 采样率(每秒):83k 数据接口:串行,并联 转换器数目:1 功率耗散(最大):95mW 电压电源:双 ± 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:28-DIP(0.600",15.24mm) 供应商设备封装:28-PDIP 包装:管件 输入数目和类型:1 个单端,双极 |

| AD9644BCPZRL7-155 | 功能描述:模数转换器 - ADC 14 Bit 155 Msps Dual 1.8V ADC RoHS:否 制造商:Analog Devices 通道数量: 结构: 转换速率: 分辨率: 输入类型: 信噪比: 接口类型: 工作电源电压: 最大工作温度: 安装风格: 封装 / 箱体: |

| AD9644BCPZRL7-80 | 功能描述:IC ADC 14BIT 80MSPS 3V 48LFCSP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1 系列:- 位数:14 采样率(每秒):83k 数据接口:串行,并联 转换器数目:1 功率耗散(最大):95mW 电压电源:双 ± 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:28-DIP(0.600",15.24mm) 供应商设备封装:28-PDIP 包装:管件 输入数目和类型:1 个单端,双极 |

发布紧急采购,3分钟左右您将得到回复。