- 您现在的位置:买卖IC网 > PDF目录17064 > AD9726-EBZ (Analog Devices Inc)BOARD EVAL FOR AD9726 PDF资料下载

参数资料

| 型号: | AD9726-EBZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 2/24页 |

| 文件大小: | 0K |

| 描述: | BOARD EVAL FOR AD9726 |

| 产品培训模块: | DAC Architectures |

| 设计资源: | AD9726 Eval Brd Schematic AD9726 Eval Brd BOM |

| 标准包装: | 1 |

| 系列: | TxDAC+® |

| DAC 的数量: | 1 |

| 位数: | 16 |

| 采样率(每秒): | 400M |

| 数据接口: | 并联 |

| DAC 型: | 电流 |

| 工作温度: | -40°C ~ 85°C |

| 已供物品: | 板 |

| 已用 IC / 零件: | AD9726 |

| 相关产品: | AD9726BSVZ-ND - IC DAC 16IT LVDS 400MSPS 80-TQFP AD9726BSVZRL-ND - IC DAC 16IT LVDS 400MSPS 80-TQFP |

AD9726

Rev. B | Page 10 of 24

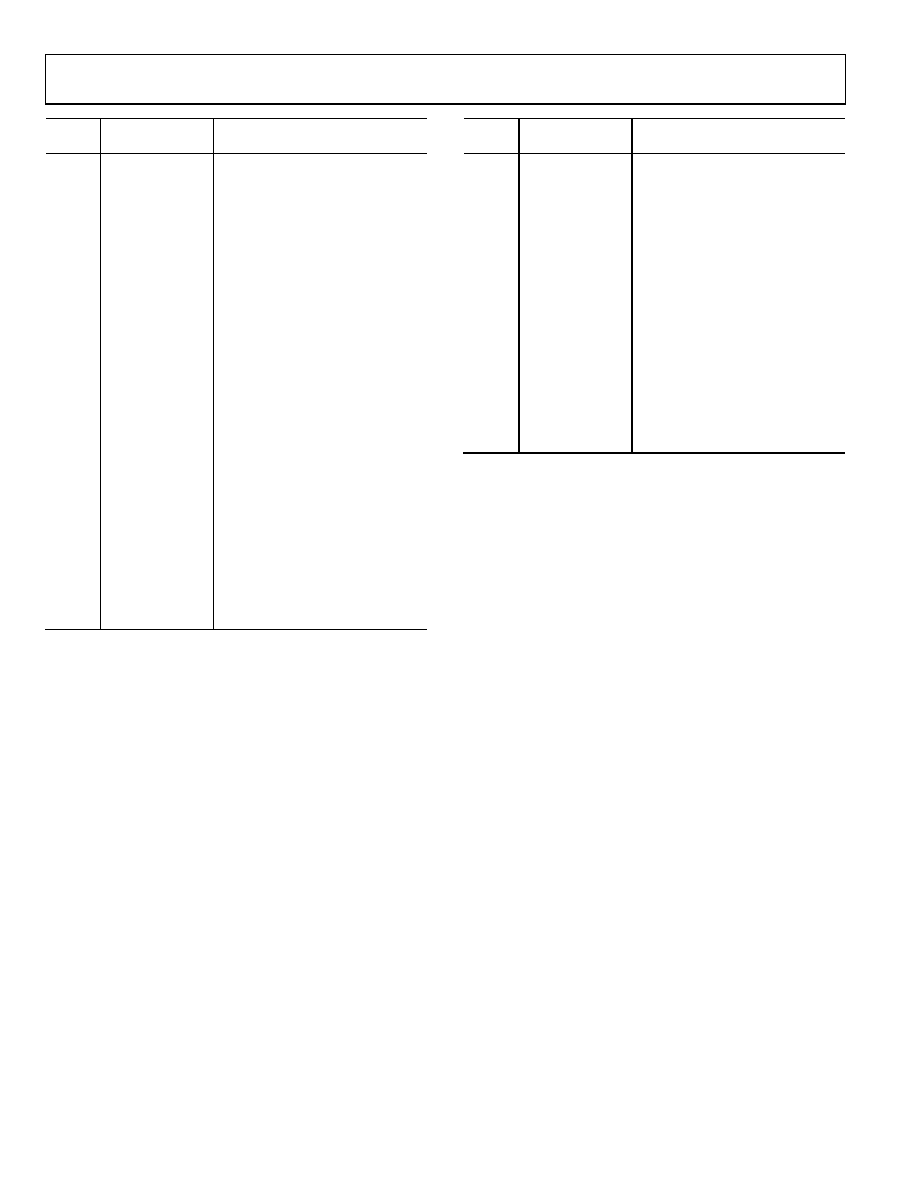

Pin

No.

Mnemonic

Description

43

DB4

Data Bit 4 Complement

44

DB3+

Data Bit 3 True

45

DB3

Data Bit 3 Complement

46

DB2+

Data Bit 2 True

47

DB2

Data Bit 2 Complement

48

DB1+

Data Bit 1 True

49

DB1

Data Bit 1 Complement

50

DB0+

Data Bit 0 True

51

DB0

Data Bit 0 Complement

52

DVDD

Digital Supply Voltage

53

DGND

Digital Supply Common

54

SDO (SYNCALRM)

55

SDIO

56

SCLK (SYNCUPD)

57

CSB

SPI Chip Select Bar (Active Low)

58

RESET

Hardware Reset (Active High)

59

REFIO

60

FSADJ

61

SDR_EN

62

ADVDD

Analog Supply Voltage

63

ADGND

Analog Supply Common

64

ACVDD

Analog Supply Voltage

65

ACGND

Analog Supply Common

66

AVDD2

Analog Supply Voltage

67

AGND2

Analog Supply Common

68

AVDD1

Analog Supply Voltage

Pin

No.

Mnemonic

Description

69

AGND1

Analog Supply Common

70

IOUTB

Analog Current Output Complement

71

IOUTA

Analog Current Output True

72

AGND1

Analog Supply Common

73

AVDD1

Analog Supply Voltage

74

AGND2

Analog Supply Common

75

AVDD2

Analog Supply Voltage

76

ACGND

Analog Supply Common

77

ACVDD

Analog Supply Voltage

78

ADGND

Analog Supply Common

79

ADVDD

Analog Supply Voltage

80

SPI_DIS

EPAD

Analog Ground. Serves as an

electrical connection to the

substrate of the die and should be

connected to ground for electrical

and thermal purposes.

1 Nominally 1 kΩ to DBGND (may be omitted if data clock output is unused).

2 SDO is output in 4-wire SPI mode and three-state in 3-wire SPI mode. If SPI is

disabled (SPI_DIS = ADVDD), the alternate pin function is SYNCALRM output.

3 SDIO is input only in 4-wire SPI mode and bidirectional in 3-wire SPI mode.

4 If SPI is disabled (SPI_DIS = ADVDD), the alternate pin function is SYNCUPD.

5 Bypass with 0.1 μF to AGND1. Use the buffer amp to drive external circuitry.

Limit the output current to 1 μA. Apply an external reference to this pin.

6 Nominally 2 kΩ to AGND1 for 20 mA full-scale output (internal reference).

7 If SPI is disabled, tie the pin to ADVDD to enable SDR. Otherwise, tie to

ADGND.

8 Tie the pin to ADVDD to disable SPI; otherwise, tie to ADGND.

相关PDF资料 |

PDF描述 |

|---|---|

| 0210490202 | CABLE JUMPER 1.25MM .178M 14POS |

| 0210490201 | CABLE JUMPER 1.25MM .178M 14POS |

| AP2182MPG-13 | IC PWR SW USB 2CH 1.5A 8-MSOP |

| 0210391009 | CABLE JUMPER 1MM .030M 31POS |

| DC1337A | BOARD SAR ADC LTC2309 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD972A | 制造商:Analog Devices 功能描述:- Bulk |

| AD9731 | 制造商:AD 制造商全称:Analog Devices 功能描述:10-Bit, 170 MSPS D/A Converter |

| AD9731/PCB | 制造商:Analog Devices 功能描述:EVAL BOARDS FOR 10 BIT 125MHZ DAC - Bulk |

| AD97310713F | 制造商:Analog Devices 功能描述:- Rail/Tube |

发布紧急采购,3分钟左右您将得到回复。