参数资料

| 型号: | AD9765ASTZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 22/44页 |

| 文件大小: | 0K |

| 描述: | IC DAC 12BIT DUAL 125MSPS 48LQFP |

| 产品培训模块: | Data Converter Fundamentals DAC Architectures |

| 标准包装: | 1 |

| 系列: | TxDAC+® |

| 设置时间: | 35ns |

| 位数: | 12 |

| 数据接口: | 并联 |

| 转换器数目: | 2 |

| 电压电源: | 模拟和数字 |

| 功率耗散(最大): | 450mW |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 48-LQFP |

| 供应商设备封装: | 48-LQFP(7x7) |

| 包装: | 托盘 |

| 输出数目和类型: | 4 电流,单极;4 电流,双极 |

| 采样率(每秒): | 125M |

| 产品目录页面: | 785 (CN2011-ZH PDF) |

| 配用: | AD9765-EBZ-ND - BOARD EVAL FOR AD9765 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页当前第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页

Data Sheet

AD9763/AD9765/AD9767

Rev. G | Page 29 of 44

500

225

25

AD8055

IOUTA

IOUTB

225

COPT

AVDD

1k

AD9763/

AD9765/

AD9767

0

06

17-

0

74

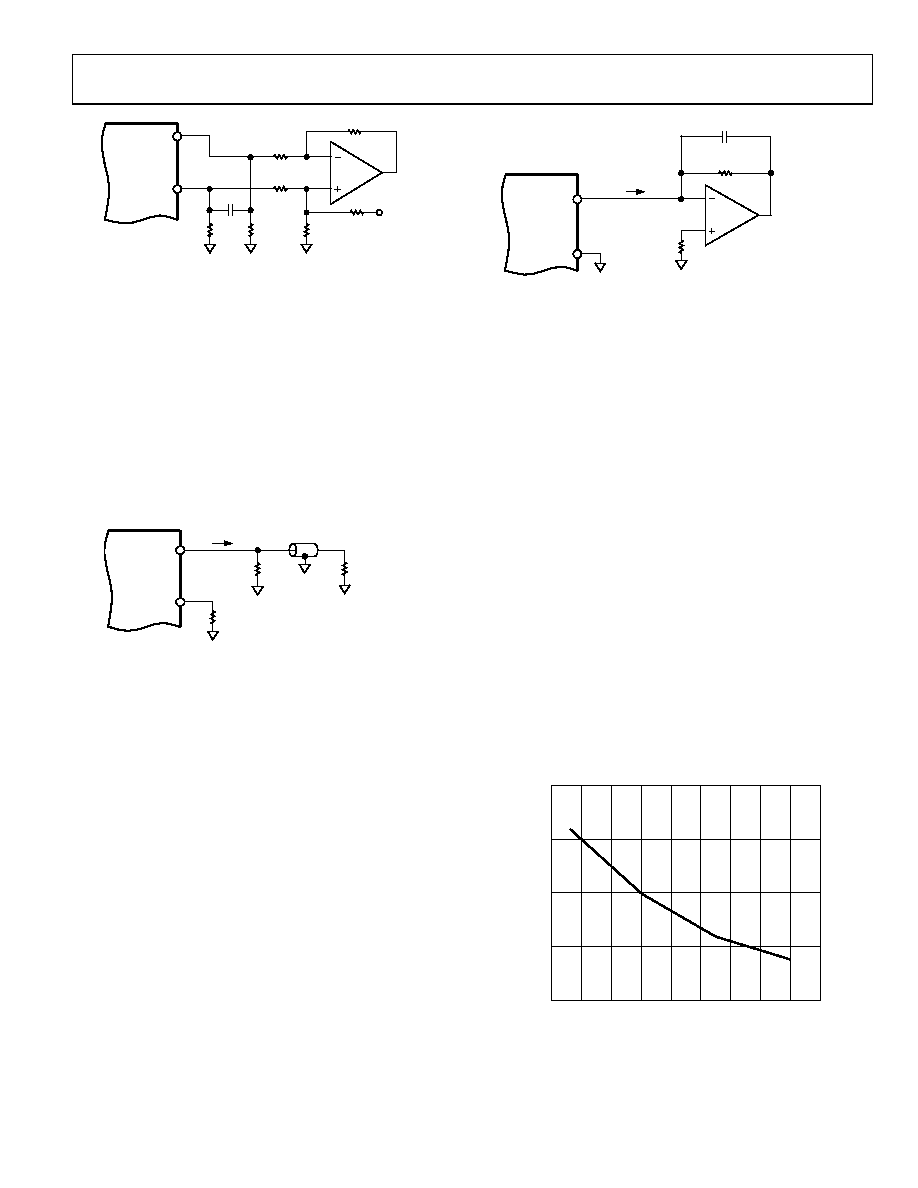

Figure 74. Single-Supply DC Differential-Coupled Circuit

SINGLE-ENDED, UNBUFFERED VOLTAGE OUTPUT

Figure 75 shows the AD9763/AD9765/AD9767 configured to

provide a unipolar output range of approximately 0 V to 0.5 V

for a doubly terminated 50 Ω cable, because the nominal full-

scale current (IOUTFS) of 20 mA flows through the equivalent

RLOAD of 25 Ω. In this case, RLOAD represents the equivalent load

resistance seen by IOUTA or IOUTB. The unused output (IOUTA or IOUTB)

can be connected directly to ACOM or via a matching RLOAD.

Different values of IOUTFS and RLOAD can be selected as long as the

positive compliance range is adhered to. One additional

consideration in this mode is the INL (see the Analog Outputs

section). For optimum INL performance, the single-ended,

buffered voltage output configuration is suggested.

50

25

50

VOUTA = 0V TO 0.5V

IOUTFS = 20mA

IOUTA

IOUTB

AD9763/

AD9765/

AD9767

00

61

7-

0

75

Figure 75. 0 V to 0.5 V Unbuffered Voltage Output

SINGLE-ENDED, BUFFERED VOLTAGE OUTPUT

CONFIGURATION

Figure 76 shows a buffered single-ended output configuration

in which the U1 op amp performs an I-V conversion on the

AD9763/AD9765/AD9767 output current. U1 maintains IOUTA

(or IOUTB) at a virtual ground, thus minimizing the nonlinear

output impedance effect on the INL performance of the DAC,

as described in the Analog Outputs section. Although this single-

ended configuration typically provides the best dc linearity

performance, its ac distortion performance at higher DAC update

rates may be limited by the slewing capabilities of U1. U1

provides a negative unipolar output voltage, and its full-scale

output voltage is simply the product of RFB and IOUTFS. Set the

full-scale output within U1’s voltage output swing capabilities

by scaling IOUTFS and/or RFB. An improvement in ac distortion

performance may result with a reduced IOUTFS because the signal

current U1 has to sink will be subsequently reduced.

IOUTFS = 10mA

U1

IOUTA

IOUTB

VOUT = IOUTFS × RFB

COPT

200

RFB

200

AD9763/

AD9765/

AD9767

00

61

7-

0

76

Figure 76. Unipolar Buffered Voltage Output

POWER AND GROUNDING CONSIDERATIONS

Power Supply Rejection

Many applications seek high speed and high performance under

less than ideal operating conditions. In these applications, the

implementation and construction of the printed circuit board is

as important as the circuit design. Proper RF techniques must

be used for device selection, placement, and routing as well as

power supply bypassing and grounding to ensure optimum

printed circuit board ground, power, and signal plane layouts

that are implemented on the AD9763/AD9765/AD9767

evaluation board.

One factor that can measurably affect system performance is

the ability of the DAC output to reject dc variations or ac noise

superimposed on the analog or digital dc power distribution.

This is referred to as the power supply rejection ratio (PSRR).

For dc variations of the power supply, the resulting performance

of the DAC directly corresponds to a gain error associated with

the DAC’s full-scale current, IOUTFS. AC noise on the dc supplies

is common in applications where the power distribution is

generated by a switching power supply. Typically, switching

power supply noise occurs over the spectrum of tens of

kilohertz to several megahertz. The PSRR vs. frequency of the

AD9763/AD9765/AD9767 AVDD supply over this frequency

range is shown in Figure 77.

90

70

85

80

75

P

S

RR

(

d

B)

0.20.3

0.40.50.60.70.80.91.01.1

FREQUENCY (MHz)

00

61

7-

0

77

Figure 77. AVDD Power Supply Rejection Ratio vs. Frequency

相关PDF资料 |

PDF描述 |

|---|---|

| MS3120F16-8S | CONN RCPT 8POS WALL MNT W/SCKT |

| VI-J4B-MZ-F1 | CONVERTER MOD DC/DC 95V 25W |

| VI-24Z-MU-F1 | CONVERTER MOD DC/DC 2V 80W |

| MS27468T25F19PC | CONN RCPT 19POS JAM NUT W/PINS |

| VI-J1L-MZ-F4 | CONVERTER MOD DC/DC 28V 25W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9765ASTZ | 制造商:Analog Devices 功能描述:12BIT DAC DUAL 125MSPS 48LQFP 制造商:Analog Devices 功能描述:12BIT DAC, DUAL, 125MSPS, 48LQFP |

| AD9765ASTZKL1 | 制造商:Rochester Electronics LLC 功能描述: 制造商:Analog Devices 功能描述: |

| AD9765ASTZRL | 功能描述:IC DAC 12BIT DUAL 125MSPS 48LQFP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:TxDAC+® 产品培训模块:Data Converter Fundamentals DAC Architectures 标准包装:750 系列:- 设置时间:7µs 位数:16 数据接口:并联 转换器数目:1 电压电源:双 ± 功率耗散(最大):100mW 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-LCC(J 形引线) 供应商设备封装:28-PLCC(11.51x11.51) 包装:带卷 (TR) 输出数目和类型:1 电压,单极;1 电压,双极 采样率(每秒):143k |

| AD9765-EB | 制造商:Analog Devices 功能描述: |

| AD9765-EBZ | 功能描述:BOARD EVAL FOR AD9765 RoHS:是 类别:编程器,开发系统 >> 评估板 - 数模转换器 (DAC) 系列:TxDAC+® 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- DAC 的数量:4 位数:12 采样率(每秒):- 数据接口:串行,SPI? 设置时间:3µs DAC 型:电流/电压 工作温度:-40°C ~ 85°C 已供物品:板 已用 IC / 零件:MAX5581 |

发布紧急采购,3分钟左右您将得到回复。