- 您现在的位置:买卖IC网 > PDF目录17062 > AD9786-EBZ (Analog Devices Inc)BOARD EVALUATION FOR AD9786 PDF资料下载

参数资料

| 型号: | AD9786-EBZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 21/56页 |

| 文件大小: | 0K |

| 描述: | BOARD EVALUATION FOR AD9786 |

| 产品培训模块: | DAC Architectures |

| 标准包装: | 1 |

| 系列: | TxDAC+® |

| DAC 的数量: | 1 |

| 位数: | 16 |

| 采样率(每秒): | 500M |

| 数据接口: | 并联 |

| DAC 型: | 电流 |

| 工作温度: | -40°C ~ 85°C |

| 已供物品: | 板,CD |

| 已用 IC / 零件: | AD9786 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页当前第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页

AD9786

Rev. B | Page 28 of 56

03152-046

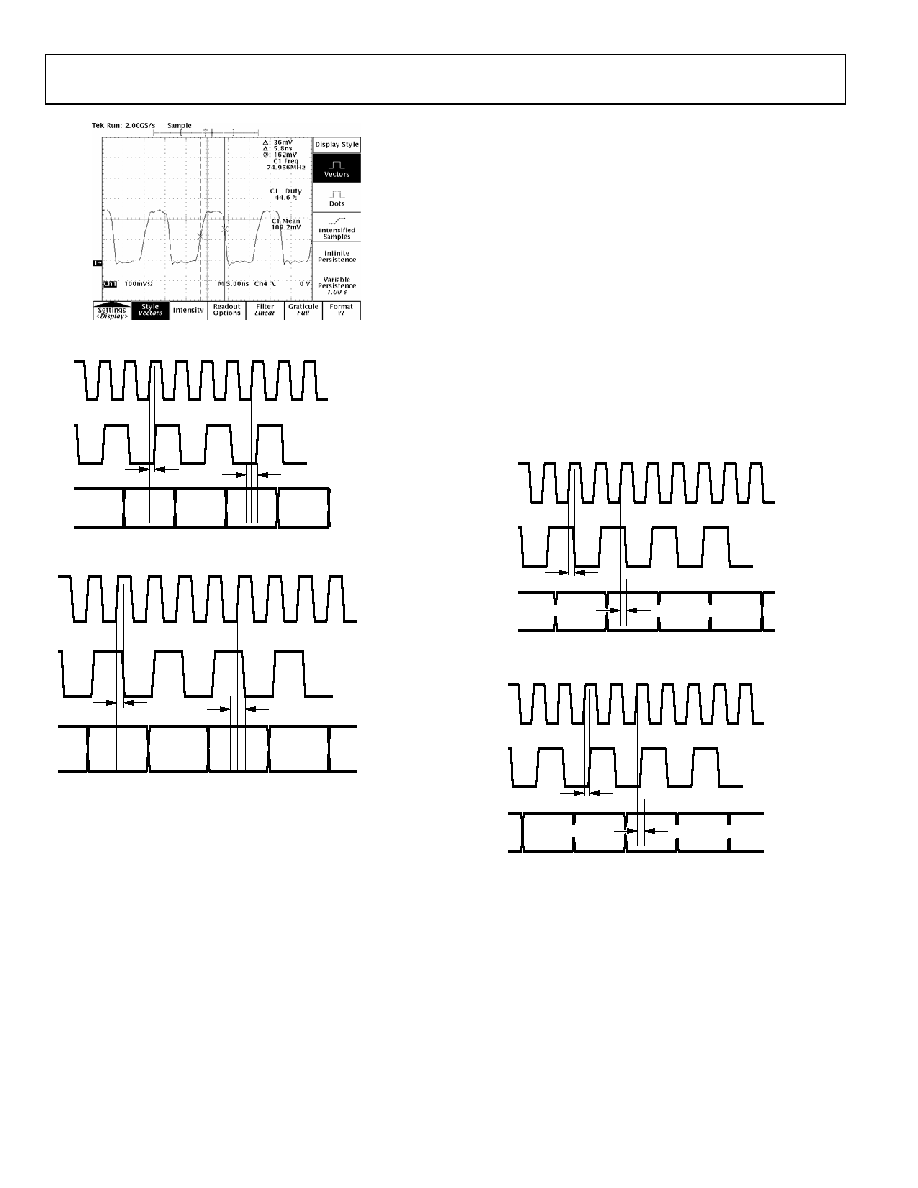

Figure 46. DATACLK Duty Cycle

03152-047

tD = 6ns TYP

tH = 2.9ns MIN

tS = –0.5ns MIN

DACCLKIN

DATACLKOUT

DATA

Figure 47. Data Timing, 2× Interpolation, DCLKPOL = 0

tD = 5ns TYP

tS = –0.5ns MIN

tH = 2.9ns MIN

DACCLKIN

DATACLKOUT

DATA

03152-048

Figure 48. Data Timing, 2× Interpolation, DCLKPOL = 1

DATACLK Slave Mode (Data Recovery On)

DATACLK (Pin 31) can be used as an input to synchronize

multiple AD9786s. A clock generated by an AD9786 operating

in master mode, or a clock from an external source, can be used

to drive DATACLK.

In this mode, two clocks are required to be applied to the

AD9786. A clock running at the DAC sample rate, referred to as

DACCLK, must be applied to the differential inputs (Pin 5 and

Pin 6) of the AD9786. As described previously, a clock at the

input sample rate must also be applied to Pin 31 (DATACLK).

An internal DLL synchronizes the two applied clocks. The

timing relationships between the input data, DATACLK, and

DACCLK are given in Figure 49 and Figure 50.

Note that DCLKPOL (Register 0x02, Bit 4) can be used to select

the edge of DACCLK upon which the input data is latched.

There is a defined setup-and-hold window with respect to input

data and the latching edge of DACCLK. There is also a required

timing relationship between DATACLK and DACCLK. This is

referred to in Figure 49 and Figure 50 as tST and tHT (setup and

hold for transition). For example, with DCLKPOL set to Logic 0,

the input data latches upon the first rising edge of DACCLK

that occurs more than 1.5 ns before the falling edge of DATACLK.

DACCLK should not be given a rising edge in the window of

500 ps to 1.5 ns before the latching edge (falling edge when

DCLKPOL = 0, rising edge when DCLKPOL = 1) of DATACLK.

Failure to account for this timing relationship could result in

corrupt data.

There are three status bits available for a read that allow the user

to verify DLL lock. These are Bit 0, Bit 1, and Bit 2 (DCRCSTAT) in

Register 0x12.

03152-049

DACCLKIN

DATACLKIN

DATA

tHT = 1.5ns MIN

tS = 0.0ns MIN

tST = –500ps MIN

tH = 3.2ns MIN

Figure 49. Slave Mode Timing, 2× Interpolation, DCLKPOL = 0

03152-050

DACCLKIN

DATACLKIN

DATA

tHT = 2.0ns MIN

tS = 0.0ns MIN

tST = –1.0ns MIN

tH = 3.2ns MIN

Figure 50. Slave Mode Timing, 2× Interpolation, DCLKPOL = 1

相关PDF资料 |

PDF描述 |

|---|---|

| MIC2099-1YMT TR | IC DISTRIBUTION SWITCH |

| RCA10DRMI-S288 | CONN EDGECARD 20POS .125 EXTEND |

| HBM11DSEN-S243 | CONN EDGECARD 22POS .156 EYELET |

| AD9772A-EBZ | BOARD EVAL FOR AD9772A |

| ECE-V1VA101UP | CAP ALUM 100UF 35V 20% SMD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9786XSV | 制造商:Analog Devices 功能描述:- Bulk |

| AD9787 | 制造商:AD 制造商全称:Analog Devices 功能描述:Dual 12-/14-/16-Bit 800 MSPS DAC with Low Power 32-Bit Complex NCO |

| AD9787BSVZ | 功能描述:IC DAC 14BIT 800MSPS 100TQFP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:TxDAC® 标准包装:1 系列:- 设置时间:4.5µs 位数:12 数据接口:串行,SPI? 转换器数目:1 电压电源:单电源 功率耗散(最大):- 工作温度:-40°C ~ 125°C 安装类型:表面贴装 封装/外壳:8-SOIC(0.154",3.90mm 宽) 供应商设备封装:8-SOICN 包装:剪切带 (CT) 输出数目和类型:1 电压,单极;1 电压,双极 采样率(每秒):* 其它名称:MCP4921T-E/SNCTMCP4921T-E/SNRCTMCP4921T-E/SNRCT-ND |

| AD9787BSVZRL | 功能描述:IC DAC 14BIT 800MSPS 100TQFP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:TxDAC® 产品培训模块:Data Converter Fundamentals DAC Architectures 标准包装:750 系列:- 设置时间:7µs 位数:16 数据接口:并联 转换器数目:1 电压电源:双 ± 功率耗散(最大):100mW 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-LCC(J 形引线) 供应商设备封装:28-PLCC(11.51x11.51) 包装:带卷 (TR) 输出数目和类型:1 电压,单极;1 电压,双极 采样率(每秒):143k |

| AD9787-DPG2-EBZ | 功能描述:BOARD EVALUATION FOR AD9787 RoHS:是 类别:编程器,开发系统 >> 评估板 - 数模转换器 (DAC) 系列:* 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- DAC 的数量:4 位数:12 采样率(每秒):- 数据接口:串行,SPI? 设置时间:3µs DAC 型:电流/电压 工作温度:-40°C ~ 85°C 已供物品:板 已用 IC / 零件:MAX5581 |

发布紧急采购,3分钟左右您将得到回复。