- 您现在的位置:买卖IC网 > PDF目录1988 > AD9920ABBCZRL (Analog Devices Inc)IC PROCESSOR CCD 12BIT 105CSPBGA PDF资料下载

参数资料

| 型号: | AD9920ABBCZRL |

| 厂商: | Analog Devices Inc |

| 文件页数: | 58/112页 |

| 文件大小: | 0K |

| 描述: | IC PROCESSOR CCD 12BIT 105CSPBGA |

| 标准包装: | 2,000 |

| 位数: | 12 |

| 电压 - 电源,模拟: | 1.6 V ~ 2 V |

| 电压 - 电源,数字: | 1.6 V ~ 2 V |

| 封装/外壳: | 105-LFBGA,CSPBGA |

| 供应商设备封装: | 105-CSPBGA(8x8) |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页当前第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页

AD9920A

Rev. B | Page 5 of 112

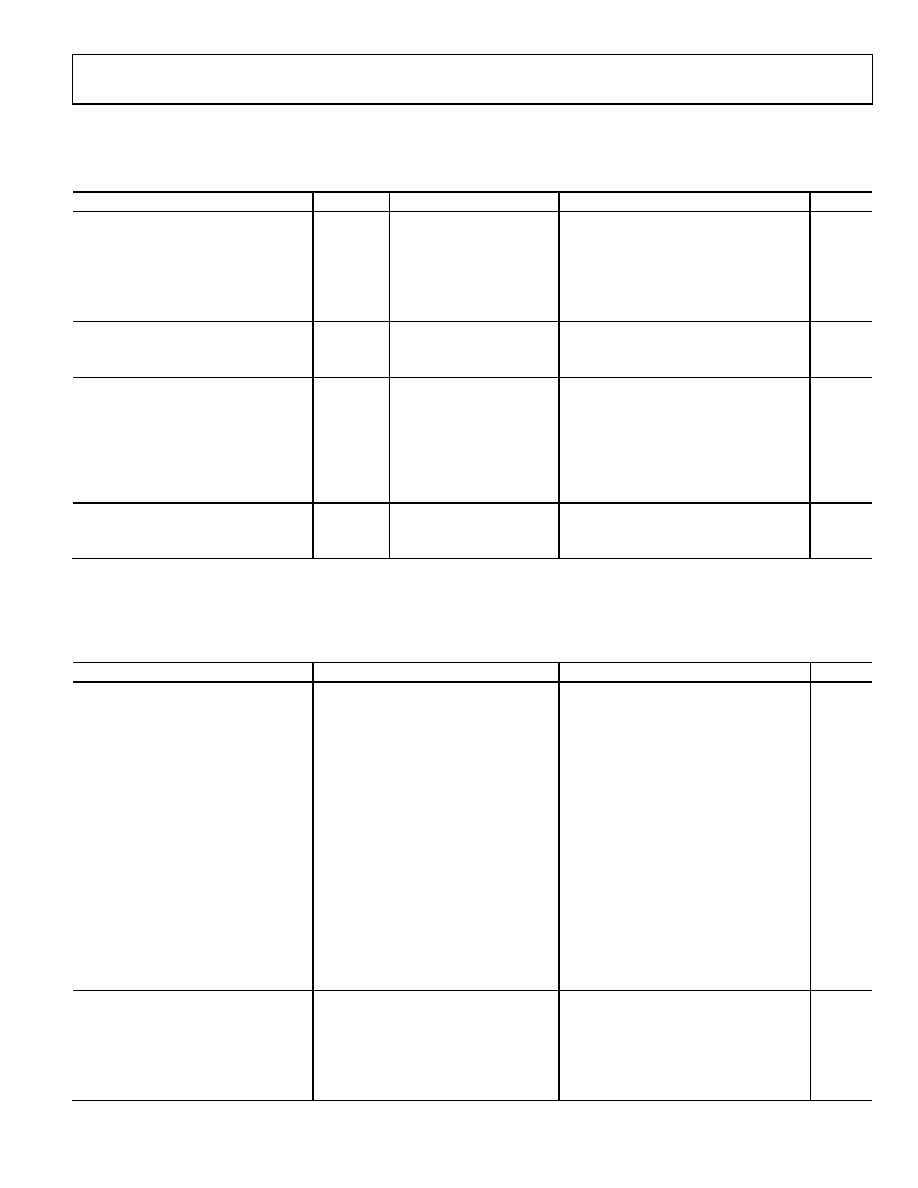

DIGITAL SPECIFICATIONS

IOVDD = 1.6 V to 3.6 V, RGVDD = HVDD1 and HVDD2 = 2.7 V to 3.6 V, CL = 20 pF, TMIN to TMAX, unless otherwise noted.

Table 2.

Parameter

Symbol

Test Conditions/Comments

Min

Typ

Max

Unit

LOGIC INPUTS (IOVDD)

High Level Input Voltage

VIH

VDD 0.6

V

Low Level Input Voltage

VIL

0.6

V

High Level Input Current

IIH

10

μA

Low Level Input Current

IIL

10

μA

Input Capacitance

CIN

10

pF

LOGIC OUTPUTS (IOVDD, DRVDD)

High Level Output Voltage

VOH

IOH = 2 mA

VDD 0.5

V

Low Level Output Voltage

VOL

IOL = 2 mA

0.5

V

RG and H-DRIVER OUTPUTS (HVDD1,

HVDD2, and RGVDD)

High Level Output Voltage

VOH

Maximum current

VDD 0.5

V

Low Level Output Voltage

VOL

Maximum current

0.5

V

Maximum H1 to H8 Output Current

Programmable

30

mA

Maximum HL and RG Output Current

Programmable

17

mA

Maximum Load Capacitance

Each output

60

pF

CLI INPUT

With CLO oscillator disabled

High Level Input Voltage

VIHCLI

CLIVDD/2 + 0.5

V

Low Level Input Voltage

VILCLI

CLIVDD/2 0.5

V

ANALOG SPECIFICATIONS

AVDD = 1.8 V, fCLI = 40.5 MHz, typical timing specifications, TMIN to TMAX, unless otherwise noted.

Table 3.

Parameter

Test Conditions/Comments

Min

Typ

Max

Unit

DC Restore

AVDD 0.5 V

1.21

1.3

1.44

V

Allowable CCD Reset Transient

Limit is the lower of AVDD + 0.3 V or 2.2 V

0.5

0.8

V

CDS Gain Accuracy

VGA gain = 6.3 dB (Code 15, default value)

3 dB CDS Gain

3.1

2.6

2.1

dB

0 dB CDS Gain

0.6

0.1

+0.4

dB

+3 dB CDS Gain

2.7

3.2

3.7

dB

+6 dB CDS Gain

5.2

5.7

6.2

dB

Maximum Input Range Before

Saturation

3 dB CDS Gain

1.4

V p-p

0 dB CDS Gain

1.0

V p-p

+3 dB CDS Gain

0.7

V p-p

+6 dB CDS Gain

0.5

V p-p

Allowable OB Pixel Amplitude1

0 dB CDS Gain (Default)

100

+200

mV

+6 dB CDS Gain

50

+100

mV

VARIABLE GAIN AMPLIFIER (VGA)

Gain Control Resolution

1024

Steps

Gain Monotonicity

Guaranteed

Gain Range

Low Gain

VGA Code 15, default

6.3

dB

Maximum Gain

VGA Code 1023

42.4

dB

相关PDF资料 |

PDF描述 |

|---|---|

| AD9978BCPZRL | IC PROCESSOR CCD 14BIT 40-LFCSP |

| ADADC71KD | IC ADC 16BIT HIGH RES 32-CDIP |

| ADADC80-Z-12 | IC ADC 12BIT INTEGRATED 32-CDIP |

| ADATE207BBPZ | IC TIMING FORMATTER QUAD 256BGA |

| ADC0804LCN | IC ADC 8-BIT 10KSPS 1LSB 20-DIP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9920BBCZ | 制造商:Analog Devices 功能描述: |

| AD9920BBCZRL | 制造商:Rochester Electronics LLC 功能描述: 制造商:Analog Devices 功能描述: |

| AD9921BBCZ | 制造商:Analog Devices 功能描述: |

| AD9921BBCZRL | 制造商:Analog Devices 功能描述: |

| AD9923A | 制造商:AD 制造商全称:Analog Devices 功能描述:CCD Signal Processor with V-Driver and Precision Timing⑩ Generator |

发布紧急采购,3分钟左右您将得到回复。