- 您现在的位置:买卖IC网 > PDF目录10979 > AD9957BSVZ (Analog Devices Inc)IC DDS 1GSPS 14BIT IQ 100TQFP PDF资料下载

参数资料

| 型号: | AD9957BSVZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 9/64页 |

| 文件大小: | 0K |

| 描述: | IC DDS 1GSPS 14BIT IQ 100TQFP |

| 产品培训模块: | Direct Digital Synthesis Tutorial Series (1 of 7): Introduction Direct Digital Synthesizer Tutorial Series (7 of 7): DDS in Action Direct Digital Synthesis Tutorial Series (3 of 7): Angle to Amplitude Converter Direct Digital Synthesis Tutorial Series (6 of 7): SINC Envelope Correction Direct Digital Synthesis Tutorial Series (4 of 7): Digital-to-Analog Converter Direct Digital Synthesis Tutorial Series (2 of 7): The Accumulator |

| 标准包装: | 1 |

| 分辨率(位): | 14 b |

| 主 fclk: | 1GHz |

| 调节字宽(位): | 32 b |

| 电源电压: | 1.8V, 3.3V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 100-TQFP 裸露焊盘 |

| 供应商设备封装: | 100-TQFP-EP(14x14) |

| 包装: | 托盘 |

| 产品目录页面: | 552 (CN2011-ZH PDF) |

| 配用: | AD9957/PCBZ-ND - BOARD EVAL AD9957 QUADRATURE MOD |

第1页第2页第3页第4页第5页第6页第7页第8页当前第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页

Data Sheet

AD9957

Rev. C | Page 17 of 64

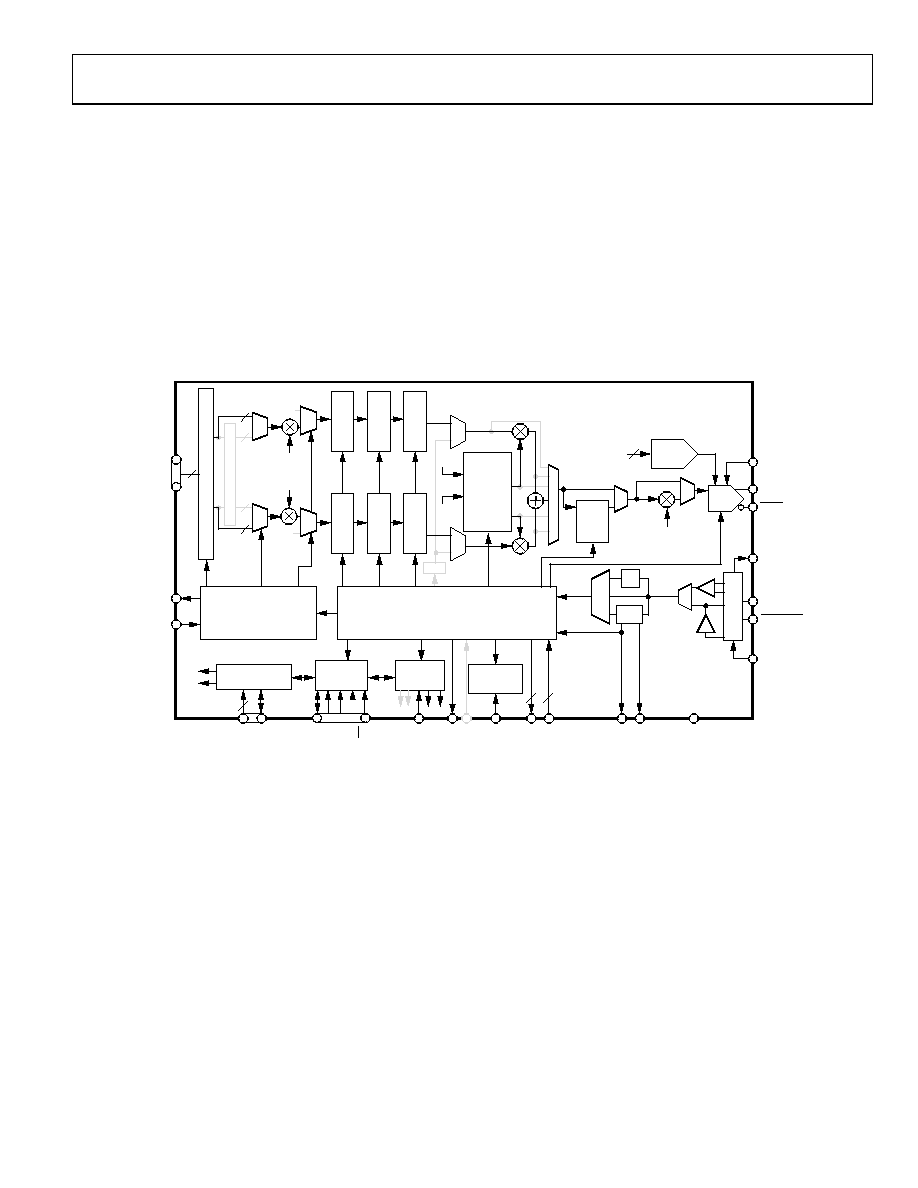

QUADRATURE MODULATION MODE

A block diagram of the AD9957 operating in QDUC mode is

shown in Figure 26; grayed items are inactive. The parallel input

accepts 18-bit I- and Q-words in time-interleaved fashion. That

is, an 18-bit I-word is followed by an 18-bit Q-word, then the

next 18-bit I-word, and so on. One 18-bit I-word and one 18-bit

Q-word together comprise one internal sample. The data assem-

bler and formatter de-interleave the I- and Q-words so that each

sample propagates along the internal data pathway in parallel

fashion. Both I and Q data paths are active; the parallel data

clock (PDCLK) serves to synchronize the input of I/Q data to

the AD9957.

The PROFILE and I/O_UPDATE pins are also synchronous to

the PDCLK.

The DDS core provides a quadrature (sine and cosine) local

oscillator signal to the quadrature modulator, where the

interpolated I and Q samples are multiplied by the respective

phase of the carrier and summed together, producing a

quadrature modulated data stream. This data stream is routed

through the inverse sinc filter (optionally), and the output

scaling multiplier. Then it is applied to the 14-bit DAC to

produce the quadrature modulated analog output signal.

06384-

006

PDCLK

I/Q IN

E

X

T

_P

W

R_DW

N

DAC_RSET

IOUT

TxENABLE

DAC GAIN

OUTPUT

SCALE

FACTOR

θ

IN

VER

SE

S

INC

FILTE

R

CLOCK

FTW

PW

8

SYSCLK

PLL

÷2

CL

O

CK

M

O

DE

REF_CLK

REFCLK_OUT

XTAL_SEL

AD9957

ω

cos (ωt+θ)

sin (ωt+θ)

S

Y

NC_O

UT

S

Y

NC_I

N

P

LL_

LOC

K

P

LL_

LOOP

_

FI

L

T

ER

MA

ST

ER

_

R

ESET

2

O

SK

DDS

AUX

DAC

8-BIT

POWER

DOWN

CONTROL

18

D

AT

A

SSEMB

L

ER

AND

F

O

RM

A

TTE

R

I

Q

IS

QS

BL

ACKF

IN

I

NT

E

R

F

ACE

18

16

IN

VER

SE

CCI

IN

VER

SE

CCI

OSK

INTERNAL CLOCK TIMING AND CONTROL

DAC

14-BIT

CCI

_O

V

F

L

FTW

PW

PARALLEL DATA

TIMING AND CONTROL

RT

RAM

P

R

OFILE

SERIAL I/O

PORT

I/O_

U

P

D

A

TE

PROGRAMMING

REGISTERS

3

I Q

IS QS

HAL

F

-BAND

FI

L

T

ER

S

(4

×

)

CCI

(1×

T

O

63×

)

HAL

F

-BAND

FI

L

T

ER

S

(4

×

)

CCI

(1×

T

O

63×

)

S

DI

O

CS

I/

O

_

R

ESET

S

CL

K

S

DO

Figure 26. Quadrature Modulation Mode

相关PDF资料 |

PDF描述 |

|---|---|

| AD9956YCPZ | IC SYNTHESIZER 1.8V 48LFCSP |

| S9S08DZ60F1MLH | MCU 60K FLASH MASK AUTO 64-LQFP |

| AD9952YSVZ | IC DDS 14BIT DAC 1.8V 48-TQFP |

| MC9S08DZ96MLF | MCU 8BIT 96K FLASH 48-LQFP |

| AD5933YRSZ | IC NTWK ANALYZER 12B 1MSP 16SSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9957BSVZ-REEL | 功能描述:IC DDS 1GSPS 14BIT IQ 100TQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 直接数字合成 (DDS) 系列:- 产品变化通告:Product Discontinuance 27/Oct/2011 标准包装:2,500 系列:- 分辨率(位):10 b 主 fclk:25MHz 调节字宽(位):32 b 电源电压:2.97 V ~ 5.5 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:带卷 (TR) |

| AD9957BSVZREEL13 | 制造商:AD 制造商全称:Analog Devices 功能描述:1 GSPS Quadrature Digital Upconverter w/18-Bit IQ Data Path and 14-Bit DAC |

| AD9958 | 制造商:AD 制造商全称:Analog Devices 功能描述:2-Channel 500 MSPS DDS with 10-Bit DACs |

| AD9958 PCB | 制造商:Analog Devices 功能描述:EVAL BOARD ((NS)) |

| AD9958/PCB | 制造商:Analog Devices 功能描述:Evaluation Board For 2-Channel 500 MSPS DDS With 10-Bit DACs 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Analog Devices 功能描述:IC 10-BIT DAC DDS |

发布紧急采购,3分钟左右您将得到回复。