- 您现在的位置:买卖IC网 > PDF目录10599 > AD9984AKSTZ-170 (Analog Devices Inc)IC DISPLAY 10BIT 170MSPS 80LQFP PDF资料下载

参数资料

| 型号: | AD9984AKSTZ-170 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 13/44页 |

| 文件大小: | 0K |

| 描述: | IC DISPLAY 10BIT 170MSPS 80LQFP |

| 标准包装: | 1 |

| 类型: | 接口 |

| 应用: | 显示器,处理,电视 |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 80-LQFP |

| 供应商设备封装: | 80-LQFP(14x14) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页当前第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页

AD9984A

Rev. 0 | Page 20 of 44

DATAIN

P0

P1

P2

P5

P3

P4

P9

P6

P8

P10

P11

P7

HSYNCx

DATACK

8 CLOCK CYCLE DELAY

DATAOUT

P0

P1

P2

P3

2 CLOCK CYCLE DELAY

HSOUT

06

476

-01

4

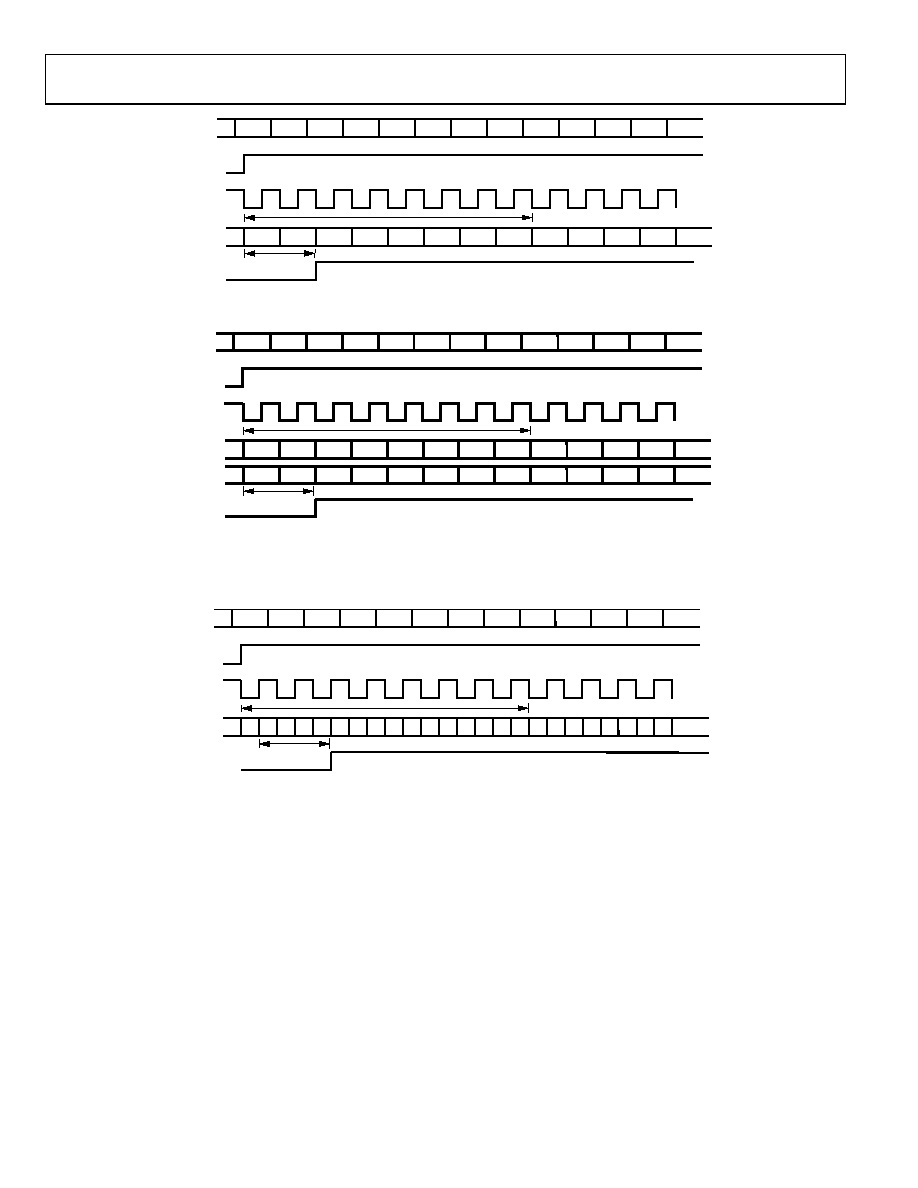

Figure 15. 4:4:4 Timing Mode

DATAIN

HSYNCx

DATACK

8 CLOCK CYCLE DELAY

Cb/CrOUT

YOUT

2 CLOCK CYCLE DELAY

HSOUT

NOTES

1. PIXEL AFTER HSOUT CORRESPONDS TO BLUE INPUT.

2. EVEN NUMBER OF PIXEL DELAY BETWEEN HSOUT AND DATAOUT.

P0

P1

P2

P3

P4

P5

P6

P7

P8

P9

P10

P11

Y0

CB0

CR0

CB2

CR2

Y1

Y2

Y3

06

47

6-

01

5

Figure 16. 4:2:2 Timing Mode

DATAIN

P0

P1

P2

P5

P3

P4

P9

P6

P8

P10

P11

P7

HSYNCx

DATACK

8 CLOCK CYCLE DELAY

2 CLOCK CYCLE DELAY

DDR NOTES

1. OUTPUT DATACK MAY BE DELAYED 1/4 CLOCK PERIOD IN THE REGISTERS.

2. SEE PROJECT DOCUMENT FOR VALUES OF F (FALLING EDGE) AND R (RISING EDGE).

3. FOR DDR 4:2:2 MODE: TIMING IS IDENTICAL, VALUES OF F AND R CHANGE.

GENERAL NOTES

1. DATA DELAY MAY VARY ± ONE CLOCK CYCLE, DEPENDING ON PHASE SETTING.

2. ADCs SAMPLE INPUT ON FALLING EDGE OF DATACK.

3. HSYNC SHOWN IS ACTIVE HIGH (EDGE SHOWN IS LEADING EDGE).

HSOUT

F0 R0 F1 R1 F2 R2 F3 R3

06

476

-01

6

Figure 17. Double Data Rate (DDR) Timing Mode

HSYNC TIMING

The Hsync is processed in the AD9984A to eliminate ambiguity

in the timing of the leading edge with respect to the phase-

delayed pixel clock and data.

The Hsync input is used as a reference to generate the pixel

sampling clock. The sampling phase can be adjusted with

respect to Hsync through a full 360° in 32 steps via the phase

adjust register (to optimize the pixel sampling time). Display

systems use Hsync to align memory and display write cycles.

Therefore, it is important to have a stable timing relationship

between the Hsync output (HSOUT) and data clock (DATACK).

Three things happen to Hsync in the AD9984A. First, the

polarity of Hsync input is determined and, as a result, has a

known output polarity. The known output polarity can be

programmed either active high or active low (Register 0x12,

Bit 3). Second, HSOUT is aligned with DATACK and data

outputs. Third, the duration of HSOUT (in pixel clocks) is set

via Register 0x13. HSOUT is the sync signal that should be used

to drive the rest of the display system.

相关PDF资料 |

PDF描述 |

|---|---|

| VE-BTN-MX-F3 | CONVERTER MOD DC/DC 18.5V 75W |

| ADV7186BBCZ-TL-RL | IC VIDEO DECODER 196CSPBGA |

| VI-2WH-IW-F1 | CONVERTER MOD DC/DC 52V 100W |

| VE-BTN-MX-F2 | CONVERTER MOD DC/DC 18.5V 75W |

| T 3507 009 | CONN FMALE RCPT 8PS FRONT PNL MT |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9984APCBZ | 制造商:AD 制造商全称:Analog Devices 功能描述:High Performance 10-Bit Display Interface |

| AD9984KSTZ-110 | 制造商:Rochester Electronics LLC 功能描述: 制造商:Analog Devices 功能描述: |

| AD9984KSTZ-140 | 制造商:Rochester Electronics LLC 功能描述: 制造商:Analog Devices 功能描述: |

| AD9984KSTZ-170 | 制造商:Analog Devices 功能描述: |

| AD9985 | 制造商:AD 制造商全称:Analog Devices 功能描述:110 MSPS/140 MSPS Analog Interface for Flat Panel Displays |

发布紧急采购,3分钟左右您将得到回复。