- 您现在的位置:买卖IC网 > PDF目录10939 > ADAU1328BSTZ-RL (Analog Devices Inc)IC CODEC 24BIT 2ADC/8DAC 48LQFP PDF资料下载

参数资料

| 型号: | ADAU1328BSTZ-RL |

| 厂商: | Analog Devices Inc |

| 文件页数: | 6/32页 |

| 文件大小: | 0K |

| 描述: | IC CODEC 24BIT 2ADC/8DAC 48LQFP |

| 标准包装: | 2,000 |

| 类型: | 通用 |

| 数据接口: | 串行 |

| 分辨率(位): | 24 b |

| ADC / DAC 数量: | 2 / 8 |

| 三角积分调变: | 是 |

| S/N 比,标准 ADC / DAC (db): | 94 / 94 |

| 动态范围,标准 ADC / DAC (db): | 105 / 106 |

| 电压 - 电源,模拟: | 3 V ~ 3.6 V |

| 电压 - 电源,数字: | 3 V ~ 3.6 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 48-LQFP |

| 供应商设备封装: | 48-LQFP(7x7) |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页当前第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页

ADAU1328

Data Sheet

Rev. B | Page 14 of 32

To maintain the highest performance possible, it is recommended

that the clock jitter of the internal master clock signal be limited

to less than 300 ps rms time interval error (TIE). Even at these

levels, extra noise or tones can appear in the DAC outputs if the

jitter spectrum contains large spectral peaks. If the internal PLL

is not being used, it is highly recommended that an independent

crystal oscillator generate the master clock. In addition, it is

especially important that the clock signal not be passed through

an FPGA, CPLD, or other large digital chip (such as a DSP)

before being applied to the ADAU1328. In most cases, this

induces clock jitter due to the sharing of common power and

ground connections with other unrelated digital output signals.

When the PLL is used, jitter in the reference clock is attenuated

above a certain frequency depending on the loop filter.

RESET AND POWER-DOWN

Reset sets all the control registers to their default settings. To

avoid pops, reset does not power down the analog outputs.

After reset is deasserted, and the PLL acquires lock condition,

an initialization routine runs inside the ADAU1328. This

initialization lasts for approximately 256 MCLKs.

The power-down bits in the PLL and Clock Control 0, DAC

Control 1, and ADC Control 1 registers power down the

respective sections. All other register settings are retained.

The reset pin should be pulled low by an external resistor to

guarantee proper startup.

SERIAL CONTROL PORT

The ADAU1328 has an SPI control port that permits programming

and reading back of the internal control registers for the ADCs,

DACs, and clock system. A standalone mode is available for

operation without serial control, standalone is configured at

reset by connecting CIN, CCLK and CLATCH to ground. In

standalone mode, all registers are set to default, except the internal

MCLK enable which is set to 1. The ADC ABCLK and ALRCLK

clock ports are set to master/slave by the connecting the COUT

pin to either DVDD or ground. Standalone mode only supports

stereo mode with an I2S data format and 256 fS MCLK rate. Refer

to Table 10 for details. If CIN, CCLK, and CLATCH are not

grounded, the ADAU1328 SPI port is active. It is recommended

to use a weak pull-up resistor on CLATCH in applications that

have a microcontroller. This pull-up resistor ensures that the

ADAU1328 recognizes the presence of a microcontroller.

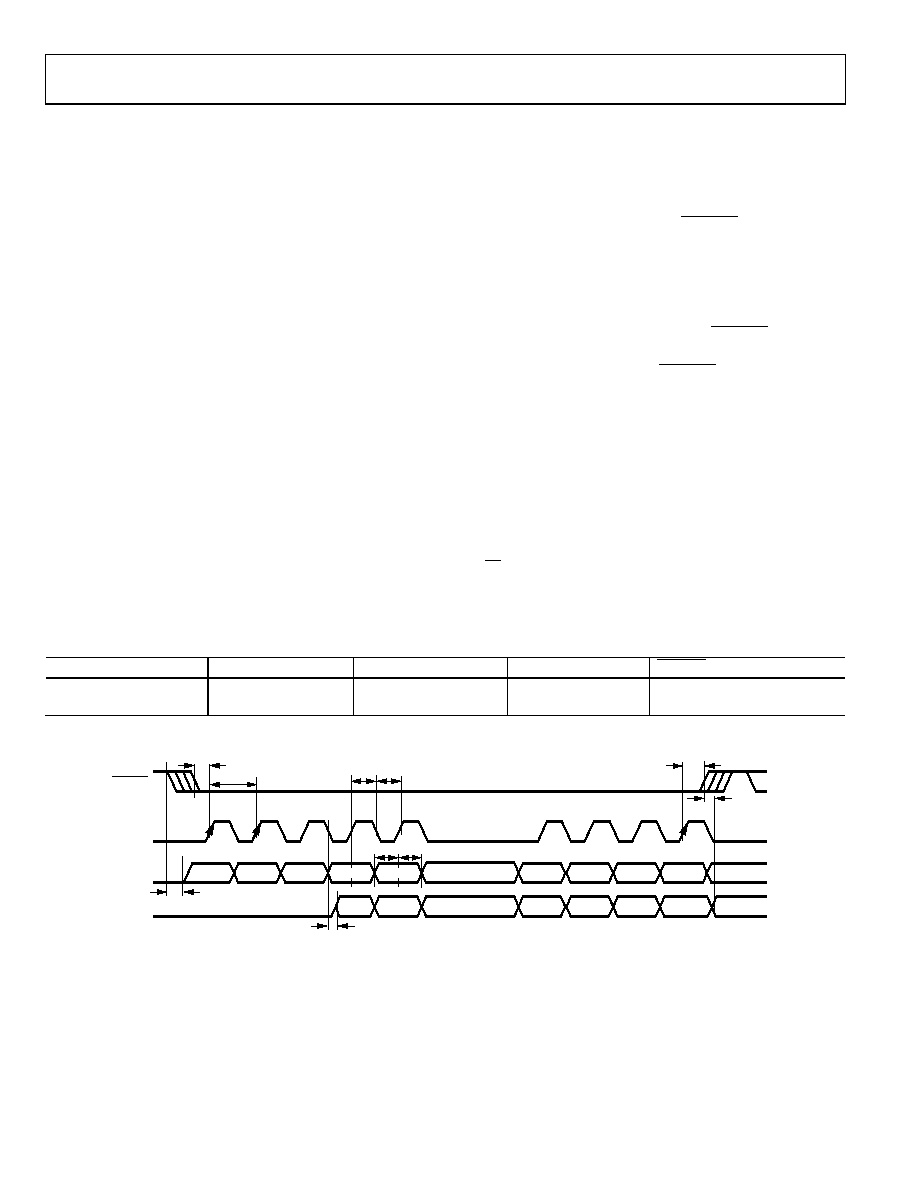

The SPI control port of the ADAU1328 is a 4-wire serial control

port. The format is similar to the Motorola SPI format except

the input data-word is 24 bits wide. The serial bit clock and

latch can be completely asynchronous to the sample rate of the

ADCs and DACs. Figure 11 shows the format of the SPI signal.

The first byte is a global address with a read/write bit. For the

ADAU1328, the address is 0x04, shifted left 1 bit due to the

R/W bit. The second byte is the ADAU1328 register address

and the third byte is the data.

Table 10. Standalone Mode Selection

ADC Clocks

CIN/ADR0

COUT/SDA

CCLK/SCL

CLATCH/ADR1

Slave

0

Master

0

1

0

D0

D8

D22

D23

D9

CLATCH

CCLK

CIN

COUT

tCCH tCCL

tCDS tCDH

tCLS

tCCP

tCLH

tCOTS

tCOD

tCOE

06102-

010

Figure 11. Format of SPI Signal

相关PDF资料 |

PDF描述 |

|---|---|

| CS4271-DZZR | IC CODEC 24BIT 114DB 28-TSSOP |

| JL05-6A20-29S-R | CONN PLUG 17POS W/SOCKET SOLDER |

| VI-J3R-IX-S | CONVERTER MOD DC/DC 7.5V 75W |

| VI-J3N-IX-S | CONVERTER MOD DC/DC 18.5V 75W |

| VI-J3M-IX-S | CONVERTER MOD DC/DC 10V 75W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADAU1361BCPZ | 功能描述:IC CODEC 24B PLL 32LFCSP RoHS:是 类别:集成电路 (IC) >> 接口 - 编解码器 系列:- 标准包装:2,500 系列:- 类型:PCM 数据接口:PCM 音频接口 分辨率(位):15 b ADC / DAC 数量:1 / 1 三角积分调变:是 S/N 比,标准 ADC / DAC (db):- 动态范围,标准 ADC / DAC (db):- 电压 - 电源,模拟:2.7 V ~ 3.3 V 电压 - 电源,数字:2.7 V ~ 3.3 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:80-VFBGA 供应商设备封装:80-BGA MICROSTAR JUNIOR(5x5) 包装:带卷 (TR) 其它名称:296-21257-2 |

| ADAU1361BCPZ | 制造商:Analog Devices 功能描述:IC, AUDIO CODEC, 24BIT, 96KHZ, LFCSP-32 |

| ADAU1361BCPZ-R7 | 功能描述:IC CODEC 24B PLL 32LFCSP RoHS:是 类别:集成电路 (IC) >> 接口 - 编解码器 系列:- 标准包装:2,500 系列:- 类型:立体声音频 数据接口:串行 分辨率(位):18 b ADC / DAC 数量:2 / 2 三角积分调变:是 S/N 比,标准 ADC / DAC (db):81.5 / 88 动态范围,标准 ADC / DAC (db):82 / 87.5 电压 - 电源,模拟:2.6 V ~ 3.3 V 电压 - 电源,数字:1.7 V ~ 3.3 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-WFQFN 裸露焊盘 供应商设备封装:48-TQFN-EP(7x7) 包装:带卷 (TR) |

| ADAU1361BCPZ-RL | 功能描述:IC CODEC 24B PLL 32LFCSP RoHS:是 类别:集成电路 (IC) >> 接口 - 编解码器 系列:- 标准包装:2,500 系列:- 类型:立体声音频 数据接口:串行 分辨率(位):18 b ADC / DAC 数量:2 / 2 三角积分调变:是 S/N 比,标准 ADC / DAC (db):81.5 / 88 动态范围,标准 ADC / DAC (db):82 / 87.5 电压 - 电源,模拟:2.6 V ~ 3.3 V 电压 - 电源,数字:1.7 V ~ 3.3 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-WFQFN 裸露焊盘 供应商设备封装:48-TQFN-EP(7x7) 包装:带卷 (TR) |

| ADAU1372BCPZ | 功能描述:General Purpose Interface 24 b I2C, SPI 40-LFCSP-WQ (6x6) 制造商:analog devices inc. 系列:- 包装:托盘 零件状态:有效 类型:通用 数据接口:I2C, SPI 分辨率(位):24 b ADC/DAC 数:4 / 2 三角积分:是 信噪比,ADC/DAC(db)(典型值):- 动态范围,ADC/DAC(db)(典型值):- 电压 - 电源,模拟:1.71 V ~ 3.63 V 电压 - 电源,数字:1.045 V ~ 1.98 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:40-WFQFN 裸露焊盘,CSP 供应商器件封装:40-LFCSP-WQ(6x6) 标准包装:1 |

发布紧急采购,3分钟左右您将得到回复。