参数资料

| 型号: | ADAU1361BCPZ-R7 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 30/80页 |

| 文件大小: | 0K |

| 描述: | IC CODEC 24B PLL 32LFCSP |

| 标准包装: | 1,500 |

| 类型: | 音频编解码器 |

| 数据接口: | 串行 |

| 分辨率(位): | 24 b |

| ADC / DAC 数量: | 2 / 2 |

| 三角积分调变: | 无 |

| 电压 - 电源,模拟: | 1.8 V ~ 3.6 V |

| 电压 - 电源,数字: | 1.8 V ~ 3.6 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 32-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 32-LFCSP-VQ |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页当前第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页

ADAU1361

Rev. C | Page 36 of 80

HEADPHONE OUTPUT

The LHP and RHP pins can be driven by either a line output

driver or a headphone driver by setting the HPMODE bit in

Register R30 (playback headphone right volume control register,

Address 0x4024). The headphone outputs can drive a load of at

least 16 Ω.

Separate volume controls for the left and right channels range

from 57 dB to +6 dB. Slew can be applied to all the playback

volume controls using the ASLEW[1:0] bits in Register R34

(playback pop/click suppression register, Address 0x4028).

Capless Headphone Configuration

The headphone outputs can be configured in a capless output

configuration with the MONOOUT pin used as a dc virtual

ground reference. Figure 44 depicts a typical playback path in

a capless headphone configuration. Table 19 lists the register

settings for this configuration. As shown in this table, the

MONOOUT pin outputs common mode (AVDD/2), which

is used as the virtual headphone reference.

07

67

9

-07

5

LHP

RHP

MONOOUT

MIXER 3

MX3LM

LHPVOL[5:0]

MX3EN

MIXER 4

MX4RM

RHPVOL[5:0]

MX4EN

MIXER 7

MX7[1:0]

MONOM

MOMODE

MX7EN

LEFT

DAC

RIGHT

DAC

Figure 44. Capless Headphone Configuration Diagram

Table 19. Capless Headphone Register Settings

Register

Bit Name

Setting

R36

DACEN[1:0]

11 = both DACs on

MX3EN

1 = enable Mixer 3

R22

MX3LM

1 = unmute left DAC input

MX4EN

1 = enable Mixer 4

R24

MX4RM

1 = unmute right DAC input

MX7EN

1 = enable Mixer 7

R28

MX7[1:0]

00 = common-mode output

MONOM

1 = unmute mono output

R33

MOMODE

1 = headphone output

LHPVOL[5:0]

Desired volume for LHP output

R29

LHPM

1 = unmute left headphone output

HPMODE

1 = headphone output

RHPVOL[5:0]

Desired volume for RHP output

R30

RHPM

1 = unmute right headphone output

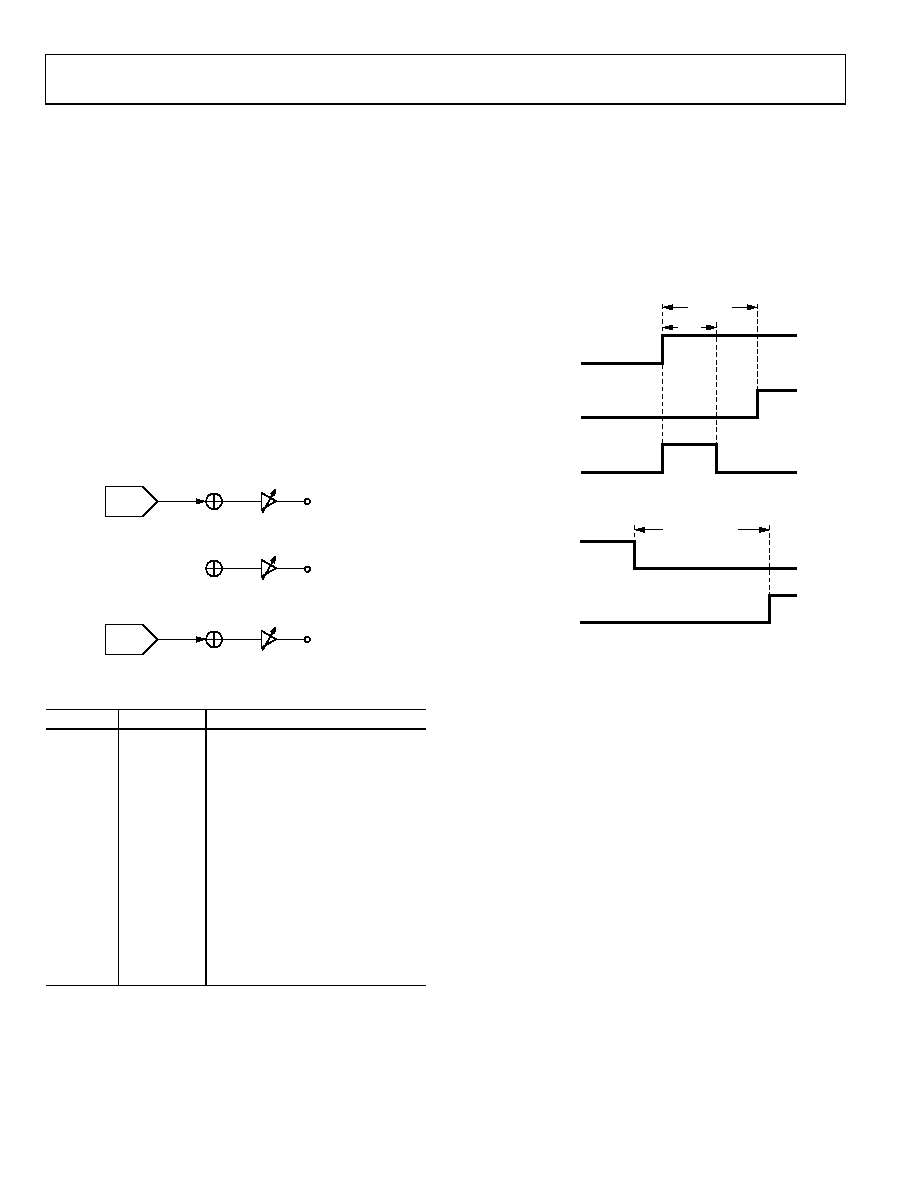

Headphone Output Power-Up/Power-Down Sequencing

To prevent pops when turning on the headphone outputs, the

user must wait at least 4 ms to unmute these outputs after

enabling the headphone output with the HPMODE bit. This is

because of an internal capacitor that must charge before these

headphone power-up/power-down sequencing.

For capless headphones, configure the MONOOUT pin before

unmuting the headphone outputs.

4ms

USER

DEFINED

07

67

9-

04

6

HPMODE

1 = HEADPHONE

INTERNAL

PRECHARGE

RHPM AND LHPM

1 = UNMUTE

Figure 45. Headphone Output Power-Up Timing

07

67

9-

04

7

HPMODE

0 = LINE OUTPUT

RHPM AND LHPM

0 = MUTE

USER DEFINED

Figure 46. Headphone Output Power-Down Timing

Ground-Centered Headphone Configuration

The headphone outputs can also be configured as ground-

centered outputs by placing coupling capacitors on the LHP

and RHP pins. Ground-centered headphones should use the

AGND pin as the ground reference.

When the headphone outputs are configured in this manner,

the capacitors create a high-pass filter on the outputs. The

corner frequency of this filter, at which point its attenuation

is 3 dB, is calculated by the following formula:

f3dB = 1/(2π × R × C)

where:

C is the capacitor value.

R is the impedance of the headphones.

For a typical headphone impedance of 16 Ω and a 47 μF

capacitor, the corner frequency is 211 Hz.

相关PDF资料 |

PDF描述 |

|---|---|

| ADAU1373BCBZ-RL | IC CODEC LP CLASS G HP 81WLCSP |

| ADAU1381BCPZ | IC AUDIO CODEC STEREO LN 32LFCSP |

| ADAU1761BCPZ-RL | IC SIGMADSP CODEC PLL 32LFCSP |

| ADAU1781BCPZ-RL7 | IC SIGMADSP CODEC LN 32LFCSP |

| ADAU1961WBCPZ-R7 | IC STEREO AUD CODEC LP 32LFCSP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADAU1361BCPZ-RL | 功能描述:IC CODEC 24B PLL 32LFCSP RoHS:是 类别:集成电路 (IC) >> 接口 - 编解码器 系列:- 标准包装:2,500 系列:- 类型:立体声音频 数据接口:串行 分辨率(位):18 b ADC / DAC 数量:2 / 2 三角积分调变:是 S/N 比,标准 ADC / DAC (db):81.5 / 88 动态范围,标准 ADC / DAC (db):82 / 87.5 电压 - 电源,模拟:2.6 V ~ 3.3 V 电压 - 电源,数字:1.7 V ~ 3.3 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-WFQFN 裸露焊盘 供应商设备封装:48-TQFN-EP(7x7) 包装:带卷 (TR) |

| ADAU1372BCPZ | 功能描述:General Purpose Interface 24 b I2C, SPI 40-LFCSP-WQ (6x6) 制造商:analog devices inc. 系列:- 包装:托盘 零件状态:有效 类型:通用 数据接口:I2C, SPI 分辨率(位):24 b ADC/DAC 数:4 / 2 三角积分:是 信噪比,ADC/DAC(db)(典型值):- 动态范围,ADC/DAC(db)(典型值):- 电压 - 电源,模拟:1.71 V ~ 3.63 V 电压 - 电源,数字:1.045 V ~ 1.98 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:40-WFQFN 裸露焊盘,CSP 供应商器件封装:40-LFCSP-WQ(6x6) 标准包装:1 |

| ADAU1372BCPZRL | 功能描述:IC CODEC LP CLASS G HP 40LFCSP 制造商:analog devices inc. 系列:- 包装:剪切带(CT) 零件状态:Digi-Key 停止供應 类型:通用 数据接口:I2C, SPI 分辨率(位):24 b ADC/DAC 数:4 / 2 三角积分:是 信噪比,ADC/DAC(db)(典型值):- 动态范围,ADC/DAC(db)(典型值):- 电压 - 电源,模拟:1.71 V ~ 3.63 V 电压 - 电源,数字:1.045 V ~ 1.98 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:40-WFQFN 裸露焊盘,CSP 供应商器件封装:40-LFCSP-WQ(6x6) 标准包装:1 |

| ADAU1372BCPZ-RL | 功能描述:General Purpose Interface 24 b I2C, SPI 40-LFCSP-WQ (6x6) 制造商:analog devices inc. 系列:- 包装:剪切带(CT) 零件状态:停产 类型:通用 数据接口:I2C, SPI 分辨率(位):24 b ADC/DAC 数:4 / 2 三角积分:是 信噪比,ADC/DAC(db)(典型值):- 动态范围,ADC/DAC(db)(典型值):- 电压 - 电源,模拟:1.71 V ~ 3.63 V 电压 - 电源,数字:1.045 V ~ 1.98 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:40-WFQFN 裸露焊盘,CSP 供应商器件封装:40-LFCSP-WQ(6x6) 标准包装:1 |

| ADAU1373BCBZ-R7 | 功能描述:IC CODEC LP W/HDPH AMP 81WLSCP RoHS:是 类别:集成电路 (IC) >> 接口 - 编解码器 系列:- 标准包装:2,500 系列:- 类型:PCM 数据接口:PCM 音频接口 分辨率(位):15 b ADC / DAC 数量:1 / 1 三角积分调变:是 S/N 比,标准 ADC / DAC (db):- 动态范围,标准 ADC / DAC (db):- 电压 - 电源,模拟:2.7 V ~ 3.3 V 电压 - 电源,数字:2.7 V ~ 3.3 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:80-VFBGA 供应商设备封装:80-BGA MICROSTAR JUNIOR(5x5) 包装:带卷 (TR) 其它名称:296-21257-2 |

发布紧急采购,3分钟左右您将得到回复。