- 您现在的位置:买卖IC网 > PDF目录378277 > ADC0802LCN (INTERSIL CORP) 8-Bit, Microprocessor- Compatible, A/D Converters PDF资料下载

参数资料

| 型号: | ADC0802LCN |

| 厂商: | INTERSIL CORP |

| 元件分类: | ADC |

| 英文描述: | 8-Bit, Microprocessor- Compatible, A/D Converters |

| 中文描述: | 1-CH 8-BIT SUCCESSIVE APPROXIMATION ADC, PARALLEL ACCESS, CDIP20 |

| 封装: | CERDIP-20 |

| 文件页数: | 23/41页 |

| 文件大小: | 1118K |

| 代理商: | ADC0802LCN |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页当前第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页

Functional Description

(Continued)

Heavy capacitive or DC loading of the clock R pin should be

avoided as this will disturb normal converter operation.

Loads less than 50 pF, such as driving up to 7 A/D converter

clock inputs from a single clock R pin of 1 converter, are al-

lowed. For larger clock line loading, a CMOS or low power

TTL buffer or PNP input logic should be used to minimize the

loading on the clock R pin (do not use a standard TTL

buffer).

2.7 Restart During a Conversion

If the A/D is restarted (CS and WR go low and return high)

during a conversion, the converter is reset and a new con-

version is started. The output data latch is not updated if the

conversion in process is not allowed to be completed, there-

fore the data of the previous conversion remains in this latch.

The INTR output simply remains at the “1” level.

2.8 Continuous Conversions

For operation in the free-running mode an initializing pulse

should be used, following power-up, to ensure circuit opera-

tion. In this application, the CS input is grounded and the WR

input is tied to the INTR output. This WR and INTR node

should be momentarily forced to logic low following a

power-up cycle to guarantee operation.

2.9 Driving the Data Bus

This MOS A/D, like MOS microprocessors and memories,

will require a bus driver when the total capacitance of the

data bus gets large. Other circuitry, which is tied to the data

bus, will add to the total capacitive loading, even in

TRI-STATE (high impedance mode). Backplane bussing

also greatly adds to the stray capacitance of the data bus.

There are some alternatives available to the designer to

handle this problem. Basically, the capacitive loading of the

data bus slows down the response time, even though DC

specifications are still met. For systems operating with a

relatively slow CPU clock frequency, more time is available

in which to establish proper logic levels on the bus and there-

fore higher capacitive loads can be driven (see typical char-

acteristics curves).

At higher CPU clock frequencies time can be extended for

I/O reads (and/or writes) by inserting wait states (8080) or

using clock extending circuits (6800).

Finally, if time is short and capacitive loading is high, external

bus drivers must be used. These can be TRI-STATE buffers

(low power Schottky such as the DM74LS240 series is rec-

ommended) or special higher drive current products which

are designed as bus drivers. High current bipolar bus drivers

with PNP inputs are recommended.

2.10 Power Supplies

Noise spikes on the V

supply line can cause conversion

errors as the comparator will respond to this noise. A low in-

ductance tantalum filter capacitor should be used close to

the converter V

pin and values of 1 μF or greater are rec-

ommended. If an unregulated voltage is available in the sys-

tem, a separate LM340LAZ-5.0, TO-92, 5V voltage regulator

for the converter (and other analog circuitry) will greatly re-

duce digital noise on the V

CC

supply.

2.11 Wiring and Hook-Up Precautions

Standard digital wire wrap sockets are not satisfactory for

breadboarding this A/D converter. Sockets on PC boards

can be used and all logic signal wires and leads should be

grouped and kept as far away as possible from the analog

signal leads. Exposed leads to the analog inputs can cause

undesired digital noise and hum pickup, therefore shielded

leads may be necessary in many applications.

A single point analog ground that is separate from the logic

ground points should be used. The power supply bypass ca-

pacitor and the self-clocking capacitor (if used) should both

be returned to digital ground. Any V

/2 bypass capacitors,

analog input filter capacitors, or input signal shielding should

be returned to the analog ground point. A test for proper

grounding is to measure the zero error of the A/D converter.

Zero errors in excess of

1

4

LSB can usually be traced to im-

proper board layout and wiring (see section 2.5.1 for mea-

suring the zero error).

3.0 TESTING THE A/D CONVERTER

There are many degrees of complexity associated with test-

ing an A/D converter. One of the simplest tests is to apply a

known analog input voltage to the converter and use LEDs to

display the resulting digital output code as shown in Figure 9

For ease of testing, the V

/2 (pin 9) should be supplied

with 2.560 V

and a V

supply voltage of 5.12 V

DC

should

be used. This provides an LSB value of 20 mV.

If a full-scale adjustment is to be made, an analog input volt-

age of 5.090 V

(5.120–1

1

2

LSB) should be applied to the

V

IN

(+) pin with the V

() pin grounded. The value of the

V

/2 input voltage should then be adjusted until the digital

output code is just changing from 1111 1110 to 1111 1111.

This value of V

REF

/2 should then be used for all the tests.

The digital output LED display can be decoded by dividing

the 8 bits into 2 hex characters, the 4 most significant (MS)

and the 4 least significant (LS). Table 1 shows the fractional

binary equivalent of these two 4-bit groups. By adding the

voltages obtained from the “VMS” and “VLS” columns in

Table 1 the nominal value of the digital display (when

V

/2 = 2.560V) can be determined. For example, for an

output LED display of 1011 0110 or B6 (in hex), the voltage

values from the table are 3.520 + 0.120 or 3.640 V

. These

voltage values represent the center-values of a perfect A/D

converter. The effects of quantization error have to be ac-

counted for in the interpretation of the test results.

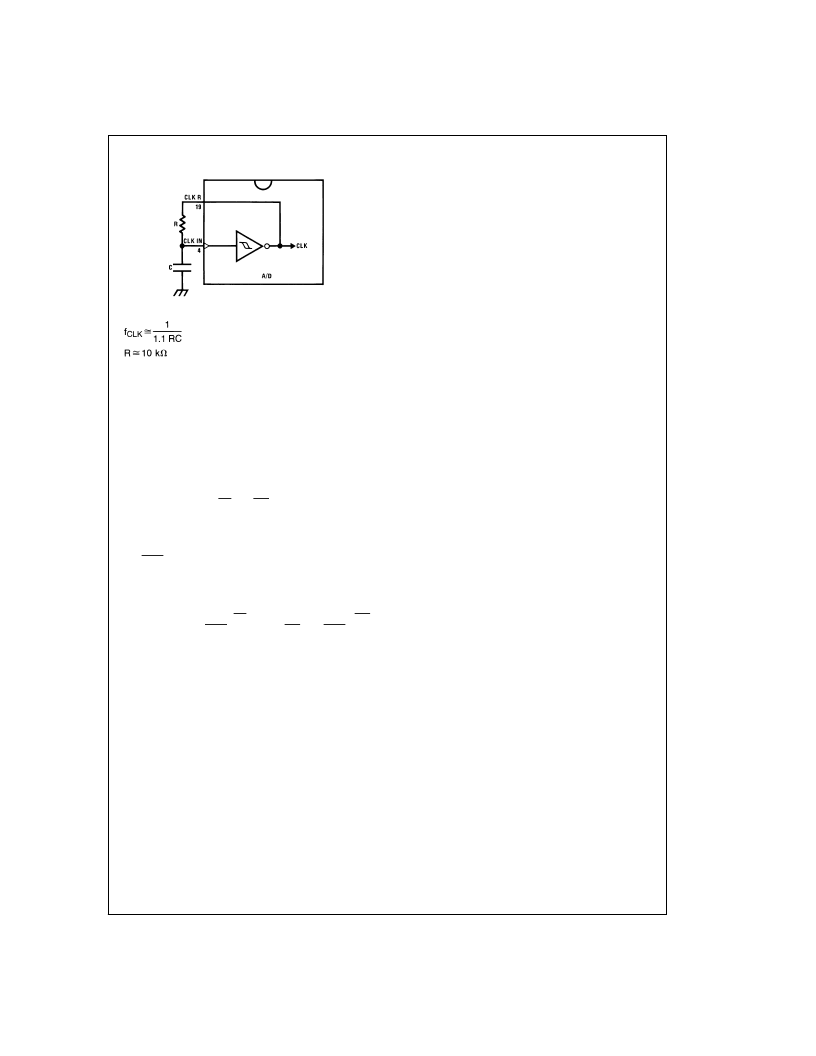

DS005671-17

FIGURE 8. Self-Clocking the A/D

A

www.national.com

23

相关PDF资料 |

PDF描述 |

|---|---|

| ADC0802LD | 8-Bit, Microprocessor- Compatible, A/D Converters |

| ADC0804 | 8-Bit, Microprocessor-Compatible A/D Converters |

| ADC08060 | 8-Bit, 20 MSPS to 60 MSPS, 1.3 mW/MSPS A/D Converter |

| ADC08060CIMT | 8-Bit, 20 MSPS to 60 MSPS, 1.3 mW/MSPS A/D Converter |

| ADC0806 | 8-Bit, 20 MSPS to 60 MSPS, 1.3 mW/MSPS A/D Converter |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADC0802LCN/A+ | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Analog-to-Digital Converter, 8-Bit |

| ADC0802LCN/NOPB | 功能描述:模数转换器 - ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| ADC0802LCN-P | 功能描述:IC ADC 8BIT MPU COMPAT 20-DIP 制造商:texas instruments 系列:- 零件状态:最後搶購 位数:8 采样率(每秒):10k 输入数:1 输入类型:差分 数据接口:并联 配置:ADC 无线电 - S/H:ADC:- A/D 转换器数:1 架构:SAR 参考类型:外部,电源 电压 - 电源,模拟:4.5 V ~ 6.3 V 电压 - 电源,数字:4.5 V ~ 6.3 V 特性:- 工作温度:- 基本零件编号:ADC0802 标准包装:18 |

| ADC0802LCV | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Analog-to-Digital Converter, 8-Bit |

| ADC0802LCWM | 制造商:Texas Instruments 功能描述: |

发布紧急采购,3分钟左右您将得到回复。